Problemas sobre ADCs

Problema 1

Um sinal analógico que varia no intervalo [0 V, 10 V] é convertido para a forma digital por

intermédio de um ADC de 8 bits.

a) Determine a resolução da conversão em Volt;

b) Encontre o código binário quando o sinal analógico assume o valor de 6 V;

c) Faça a representação binária correspondente ao valor de 6,2 V;

d) Considere o valor de 6,2 V para o sinal analógico de entrada.

d1) Determine o erro absoluto de quantificação;

d2) Expresse o erro de quantificação em percentagem relativamente ao valor de

entrada;

d3) Expresse o erro de quantificação em percentagem relativamente ao valor de fim de

escala;

e) Calcule o maior erro de quantificação usualmente tido como admissível, em percentagem,

relativamente à tensão de fim de escala.

Soluções: a) 0,0392 V; b) 10011001; c) 10011110; d1) -0,0064 V; d2) -0,1%; d3) -0,064%;

e)0,196%

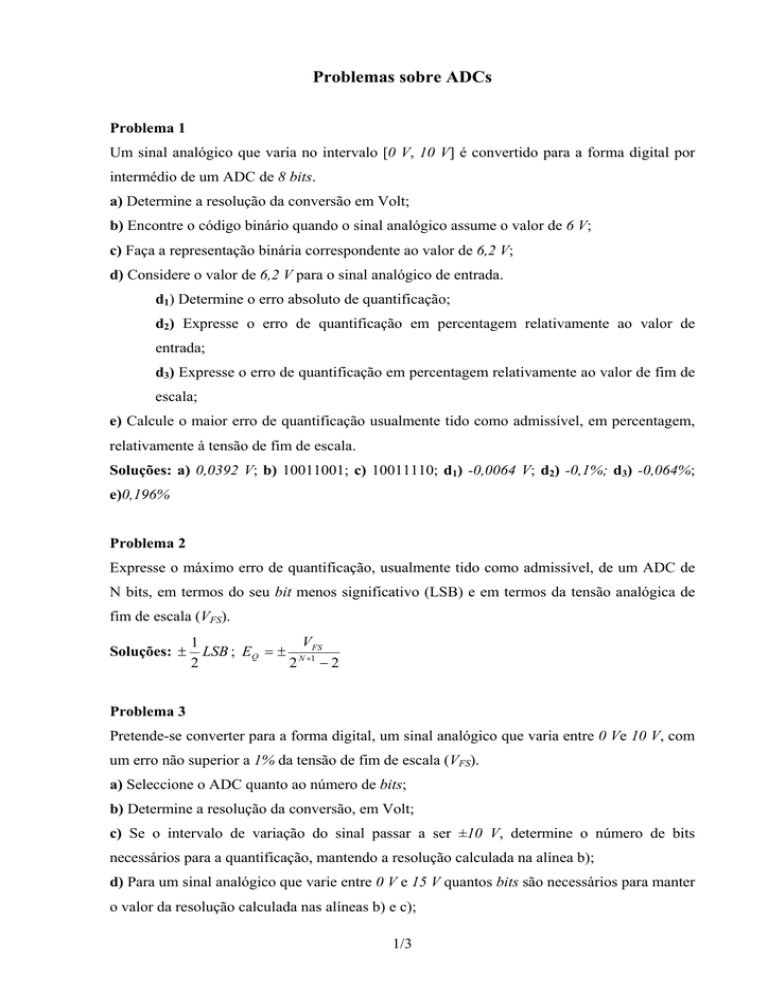

Problema 2

Expresse o máximo erro de quantificação, usualmente tido como admissível, de um ADC de

N bits, em termos do seu bit menos significativo (LSB) e em termos da tensão analógica de

fim de escala (VFS).

Soluções: ±

V

1

LSB ; EQ = ± N +1FS

2

2 −2

Problema 3

Pretende-se converter para a forma digital, um sinal analógico que varia entre 0 Ve 10 V, com

um erro não superior a 1% da tensão de fim de escala (VFS).

a) Seleccione o ADC quanto ao número de bits;

b) Determine a resolução da conversão, em Volt;

c) Se o intervalo de variação do sinal passar a ser ±10 V, determine o número de bits

necessários para a quantificação, mantendo a resolução calculada na alínea b);

d) Para um sinal analógico que varie entre 0 V e 15 V quantos bits são necessários para manter

o valor da resolução calculada nas alíneas b) e c);

1/3

e) Para o caso descrito na alínea d) determine a resolução e o erro máximo de quantificação,

usualmente considerado.

Soluções: a) 6; b) 0,158 V; c) 7; d) 7; e) EQ=59 mV.

Problema 4

Considere um ADC flash de 4 bits, no qual a menor tensão de comparação VR1 é, em Volt;

igual a 1/2 LSB.

a) Determine o número de comparadores do conversor;

b) Determine o valor de todas as tensões de comparação, sabendo que a tensão de referência

tem o valor de 10 V;

c) Faça o diagrama eléctrico da coluna de divisores de tensão, para gerar todas as tensões de

comparação necessárias ao conversor, usando apenas resistências de 1 kΩ, e determine o

número de resistências necessárias;

d) Sabendo que a comparação é feita em 50 ns e que a lógica de controlo e codificação requer

35 ns, determine a taxa máxima de conversão;

e) Determine o estado da saída dos comparadores e o código na saída do conversor para as

entradas analógicas: VA1=0 V, VA2=+5,66 V, VA3=+10 V.

Soluções: a) 15; b) VR1=0,335 V, VR2=1,005 V, VR3=1,675 V, VR4=2,345 V, VR5=3,015 V,

VR6=3,685 V, VR7=4,355 V, VR8=5,025 V, VR9= 5,695 V, VR10=6,365 V, VR11=7,035 V, VR12=

7,0705 V, VR13=8,375 V, VR14=9,045 V, VR15=9,715 V; c) 18; d) fconv=11,76 MHz; e) VA1=0 V

→ todos os comparadores com a saída a “0” e o código: 0000; VA2=+5,66 V → os

comparadores de 1 a 8 com a saída a “1” e os comparadores de 9 a 15 com a saída a “0” e o

código: 1000; VA3=+10 V→todos os comparadores com a saída a “1” e o código: 1111.

Problema 5

Um ADC de Rampa Dupla de 12 bits, utiliza um clock de 1 MHz e uma tensão de referência

de +10 V. A entrada analógica pode assumir valores entre 0 V e -10 V. O intervalo de tempo

fixo T1, corresponde ao tempo necessário para o contador atingir a contagem máxima 2N, onde

N é o seu número de bits.

a) Determine o tempo necessário para codificar em binário uma amostra de -10 V;

b) Assuma que o valor da tensão (Vp) na saída do integrador de Miller no final do tempo T1 é

de + 10 V, para a entrada VA=-10 V, e determine a constante de tempo do integrador;

2/3

c) Considere que, devido ao envelhecimento, os componentes R e C do integrador de Miller

sofrem alterações dos seus valores nominais. Assim, o valor de resistência R aumenta 2% e a

capacidade do condensador C decresce 1%. Calcule o valor da tensão (V’p) na saída do

integrador, no final do tempo T1, para VA=-10 V;

d) Para a situação descrita em c), determine a variação da precisão da conversão.

Soluções: a) T=8,192 ms; b) τ =4,096 ms; c) ⏐V’p⏐=9,9 V; e) n = nref ×

VA

Vref

.

Problema 6 (exercício 10.37 da página 95 do KC’s Problems)

Pretende-se fazer a conversão AD de um sinal analógico que varia no intervalo de ±5 V. Para

fazer a conversão deste sinal é importante reconhecer variações de 0,1 V. Determine:

a) O número de bits do conversor AD;

b) A resolução, em Volt, do ADC, para a situação indicada, tendo em conta o número de bits

seleccionado na alínea anterior.

Soluções: a) 7; b) 0,079 V.

3/3