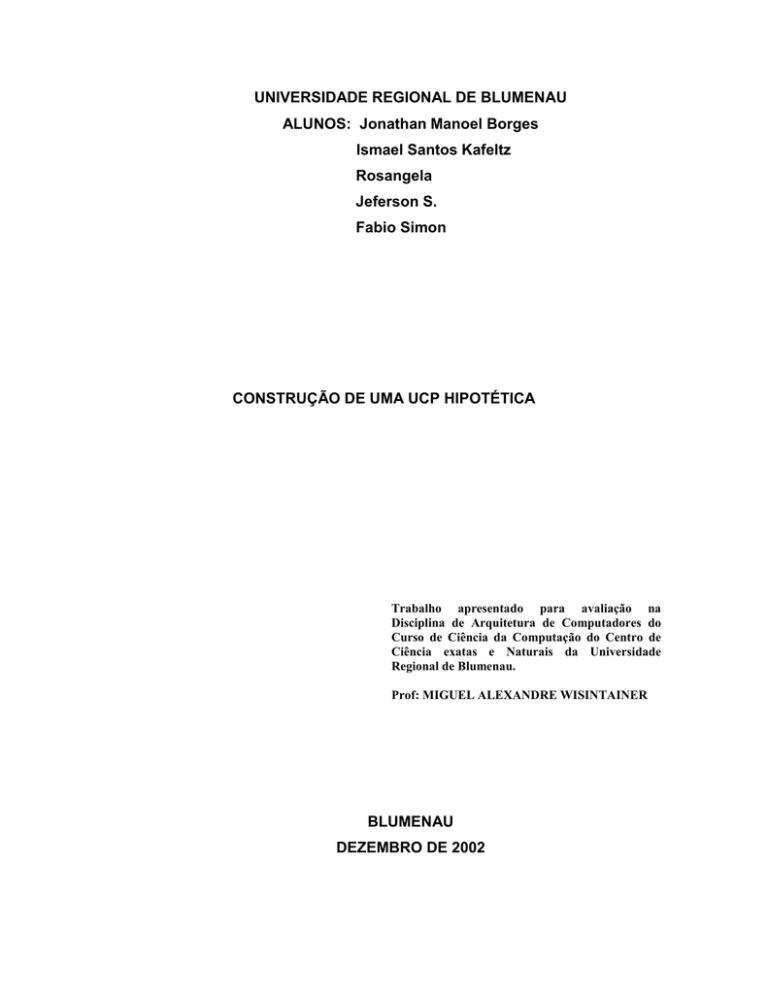

UNIVERSIDADE REGIONAL DE BLUMENAU

ALUNOS: Jonathan Manoel Borges

Ismael Santos Kafeltz

Rosangela

Jeferson S.

Fabio Simon

CONSTRUÇÃO DE UMA UCP HIPOTÉTICA

Trabalho apresentado para avaliação na

Disciplina de Arquitetura de Computadores do

Curso de Ciência da Computação do Centro de

Ciência exatas e Naturais da Universidade

Regional de Blumenau.

Prof: MIGUEL ALEXANDRE WISINTAINER

BLUMENAU

DEZEMBRO DE 2002

Sumário

Introdução ...................................................................................... 1

ULA.................................................................................................. 2

Somador e Subtrator de 8 bits ......................................................... 2

AND ................................................................................................. 3

OR ................................................................................................... 3

XOR ................................................................................................. 3

NOT ................................................................................................. 4

NOP ................................................................................................. 4

Increment......................................................................................... 4

Acumulador ..................................................................................... 5

Banco de Registradores .................................................................. 5

PC.................................................................................................... 5

DIR .................................................................................................. 5

SelDir ............................................................................................... 6

Memória........................................................................................... 6

UCP ................................................................................................. 7

Anexos............................................................................................. 17

Introdução

Este trabalho demostra uma CPU hipotética construída no software Digital

Works 2.0. A CPU tem funções lógicas e aritméticas e movimentação de dados de

uma memória para outra. O objetivo é mostrar como funciona uma UCP passo a

passo baseado em clocks manuais para melhor visualização de todo o processo

que a máquina hipotética realiza, de acordo com as instruções previamente

colocadas na memória de programa.

ULA

ULA é formada por dois operandos de 8 bits A e B, com saída de 8 bits.

Possui 3 entradas de seleção de operação:

Seleção 000 -> Soma1;

Seleção 001 -> Subtração2;

Seleção 010 -> AND;

Seleção 011 -> OR;

Seleção 100 -> XOR;

Seleção 101 -> NOT;

Seleção 110 -> Linha Reta;

Seleção 111 -> Incremento*3;

FC: Flag Carry indica estouro de uma operação;

FZ: Flag Zero indica que o resultado da operação é 0(zero);

Enable: Sistem tri-state que joga o valor da ULA no BUS de dados.

Veja figura 1.

Somador e Subtrador 8 bits

Tem 16 entradas para operando sendo 8 bits para cada entrada A e B, e

uma saída S de 8 bits para resultado da operação. Tem 1 bit para seleção de

operação(0 para soma e 1 para subtração).Veja figura 2.

1|2|3

2

Altera o valor de FC

AND

Sua função é comparar os bits de entrada e jogar o resultado na saída S.

Tem 16 entradas, sendo 8 para entrada A e 8 para entrada B, e uma saída de 8

bits contendo o resultado da operação, contem internamente 8 portas lógicas tipo

AND. A tabela demostra a comparação de 2 bits para exemplo. Veja figura 3.

Entradas

Saída

A

B

S

0

0

0

0

1

0

1

0

0

1

1

1

OR

Tem 16 entradas, sendo 8 para entrada A e 8 para entrada B, e uma saída

de 8 bits contendo o resultado da operação, contem internamente 8 portas lógicas

OR. A tabela verdade demostra sua função. Veja figura 4.

Entradas

Saída

A

B

S

0

0

0

0

1

1

1

0

1

1

1

1

XOR

Tem 16 entradas, sendo 8 para entrada A e 8 para entrada B, e uma saída

de 8 bits contendo o resultado da operação, contem internamente 8 portas lógicas

XOR. A tabela verdade demostra sua função. Veja figura 5.

3

Entradas

Saída

A

B

S

0

0

0

0

1

1

1

0

1

1

1

1

NOT

Tem entrada de 8 bits e saída de 8 bits, contem internamente 8 portas

lógicas NOT e sua função é inverter o valor de entrada.

Veja figura 6.

Entradas

Saída

A

S

0

1

1

0

NOP

No operation, sua função é basicamente nada, somente deixa passar os

valores de entrada da ULA diretamente para a saída sem serem afetados.

Increment

Possui uma entrada B de 8 bits e uma saída de 8 bits, sua função é

incrementar a um, possui uma flag para indicar estouro.

Figura 8.

4

Acumulador

O acumulador nada mais é que um conjunto de Flip-Flips tipo de, teu tem

a função de armazenar dados para realizar operações posteriores.

Características:

Entrada: 8 bits de entrada por onde os valores serão enviados até ele

Saída: 8 bits de saída que jogam seus valores para o BUS de dados.

Carga: 1(um) bit de clock usado para receber os valores que é passado

pelo bus de dados

Enable: usado para ligar/desligar o acumulador.

Veja figura 7.

Banco de Registradores

É encapsulado 4 registradores, B,C,D e E.

Entradas: 8 bits para receber os dados do barramento de dados.

Saídas: 8 bits para colocar no barramento os valores guardados.

Seletores: 2 bits de entradas que selecionará o registrador a ser usado.

Carga: 1 bit de entrada para receber o clock que armazenará no

registrador selecionado o dado.

Enable: Habilita ou desabilita o banco de registradores.

Veja figura 10.

PC

Program Counter. É um buffer, aponta para uma instrução contida na

memória. Contém 8 bits de entrada e 8 bits de saída e 1 bit para carga. Ver figura

11.

DIR

Sua função é apontar para um endereço de memória. Contém 8 bits de

entrada e saída. Ver figura 12.

5

SelDir

É um multiplexador. Ela depende do PC e do DIR, tem duas entradas de 8

bits A e B, pelo seletor ela decide qual dos dois aparecerá na saída.

Memória

Memória do tipo RAM, que armazena as instruções e dados que serão

realizadas com algum propósito pela CPU hipotética.

Características: Possui 8 bits de entrada de dados e 8 bits para saída de

dados, R/W(read/write) que indica a operação de escrita ou de leitura(baixo é

escrita e alto é leitura), e CS que habilita ou desabilita a memória.

6

UCP – Unidade Central de Processamento

Objetivo da UCP é controlar todo o circuito. Recebendo instruções e

decodificando-as, e executando-as através de sinais de controle.

Componentes internos da UCP:

Clock - É ligado no Carga do IC.

RI – Registrador de Instruções, armazena a instrução atual que é

recebida da memória de programa. Tem 8 bits entrada ligadas

fisicamente ao bus de dados onde recebe a instrução. Dos 8 bits de

saída, os primeiros 3 bits (XXX0 0000), estão ligados diretamente à

Seleção de Operação da ULA. Os próximos 2 bits (000X X000), estão

ligados diretamente na Seleção de Registrador. Os 3 últimos

bits(0000 0XXX), estão ligados à Memória de Seleção de Controle. E

por último o sinal de carga que é ligado ao Clock.

Memória de Seleção de Controle(ROM) – Devido a grande

quantidade de sinais de controle da Memória de Controle, esta

memória é usada como uma memória auxiliar para decodificar os 3 bits

que vem do RI, indo para o IC através de um multiplexador, a primeira

Micro-Instrução de cada instrução na memória de controle. Ver tabela

de controle em anexos.

IC – Contador de Micro-Instruções – Objetivo deste registrador é

apontar para cada micro-instrução da memória de controle. A cada fim

de instrução, ou seja, na última micro-instrução é recebido um sinal de

reset apontando para a primeiro micro-instrução da memória de

controle(a primeiro micro-instrução da memória de controle é a busca

de instrução da memória de programa). O sinal de carga do IC, tanto

pode apontar para próxima posição da memória de controle como pode

apontar para primeiro micro-instrução de cada instrução da memória

de programa, dependendo o valor de SelRI.

Memória de controle - Contém todas as micro-instruções que irão

controlar todos os dispositivos. É endereçada pelo registrados IC.

7

Cada bit dos 16 bits de saída controla um dispositivo específico. Veja o

conteúdo da memória de controle na tabela 1 em anexos.

Sinais de Controle da Memória de Controle

Cada bit tem um sinal de controle para estes dispositivos.

Controles Internos:

1 bit ICres (Reseta registrador contador de micro-instrução).

2 bit RIcar (Carga do registrador de instrução).

3 bit SelRI (Seleção de entrada para IC; (0)IC=IC+1, (1)IC=RI).

Controles Externos:

Controles de endereçamento da memória de programa (RAM)

4 bit PCcar (Carga do registrador contador de programa)

5 bit DIRcar (Carga do registrador de endereço de memória RAM).

6 bit SelDIR (Seleção de registrador de endereço de memória de

programa). (0)End=PC, (1)End=Dir)

Controles da memória de programa:

7 bit MEMbus (Enable da Memória de Programa. Joga conteúdo da

memória no bus de dados).

8 bit MEMcar (Carga da memória de programa. Grava conteúdo do bus de

dados na memória)

Controles do Acumulador:

9 bit ACbus (Enable do Acumulador. Joga conteúdo do acumulador no bus

de dados)

10 bit ACcar (Carga do Acumulador. Grava conteúdo do bus de dados no

acumulador)

Controles do Banco de Registradores:

11 bit REGbus (Enable dos registradores. Joga conteúdo do registrador

selecionado no bus de dados)

8

12 bit REGcar (Carga dos registradores. Grava conteúdo do bus de dados

no registrador selecionado)

Controle do Registrador Buffer da ULA:

13 bit BUFcar (Carga do registrador Buffer da ULA. Carrega buffer com

conteúdo do bus de dados)

Controle da ULA:

14 bit ULAbus (Enable da ULA. Joga conteúdo resultante da ULA no bus

de dados)

Instruções da Memória de Programa

As instruções da memória de programa são divididas em três partes.

A primeira parte, com os 3 bits iniciais, referenciam a operação da ULA:

XXX0 0000

000 - ADD

100 - XOR

001 - SUB

101 - NOT

010 - AND

110 - MOV (não altera o valor)

011 - OR

111 - INC

A segunda parte, com os próximos 2 bits, selecionam o registrador no

Banco de Registradores.

000X X000

00 - B

10 - D

01 - C

11 - E

Os últimos três bits seleciona o tipo de operação do controlador(seleciona

a primeira micro-instrução da instrução).

0000 0XXX

9

Os primeiro controles da memória de controle são designados para

instrução de busca de instrução. Ou seja, a primeira instrução executada é

exatamente a busca de instrução, assim como cada fim de instrução da memória

de programa.

Controles de busca de instrução

(próximo clock começa a execução da instrução que está em RI)

0000 0000 0000 0000 (0) ->NOP

0000 0010 0000 0000 (7) ->MEMbus

0111 0000 0000 0000 (2,3,4)->RIcar, SelRI, PCcar

000 - Operação da ULA com AC e AC, resultando no AC

0000 0000 0000 0000 (0)

->NOP

0000 0000 1000 0000 (9)

->ACbus

0000 0000 0000 1000 (13)

->BUFcar

0000 0000 0000 0100 (14)

->ULAbus

0000 0000 0100 0000 (10)

->ACcar

1000 0000 0000 0000 (1)

->ICres

(AC = AC * AC)

001 - Operação da Ula com AC e AC, resultando no REG (REG = REG * AC)

0000 0000 0000 0000 (0)

->NOP

0000 0000 1000 0000 (9)

->ACbus

0000 0000 0000 1000 (13)

->BUFcar

0000 0000 0000 0100 (14)

->ULAbus

0000 0000 0001 0000 (12)

->REGcar

1000 0000 0000 0000 (1)

->ICres

010 - Operação da ULA com REG e AC, resultando no AC (AC = REG * AC)

0000 0000 0000 0000 (0)

->NOP

0000 0000 0010 0000 (11)

->REGbus

0000 0000 0000 1000 (13)

->BUFcar

10

0000 0000 0000 0100 (14)

->ULAbus

0000 0000 0100 0000 (10)

->ACcar

1000 0000 0000 0000 (1)

->ICres

011- Operação da ULA com o REG e AC, resultando no REG (REG = REG *

AC)

0000 0000 0000 0000 (0)

->NOP

0000 0000 0010 0000 (11)

->REGbus

0000 0000 0000 1000 (13)

->BUFcar

0000 0000 0000 0100 (14)

->ULAbus

0000 0000 0001 0000 (12)

->REGcar

1000 0000 0000 0000 (1)

->ICres

100 - Operação da ULA com MEM e o AC, resultando no AC

(AC = MEM *

AC)

0000 0000 0000 0000 (0)

->NOP

0000 0010 0000 0000 (7)

->MEMbus

0000 0000 0000 1000 (13)

->BUFcar

0001 0000 0000 0100 (4,14)

->PCcar, ULAbus

0000 0000 0100 0000 (10)

->ACcar

1000 0000 0000 0000 (1)

->ICres

101 - Operação da Ula com MEM e o AC, resultando em REG(REG = MEM *

AC)

0000 0000 0000 0000 (0)

->NOP

0000 0010 0000 0000 (7)

->MEMbus

0000 0000 0000 1000 (13)

->BUFcar

0001 0000 0000 0100 (4,14)

->PCcar, ULAbus

0000 0000 0001 0000 (12)

->REGcar

1000 0000 0000 0000 (1)

->ICres

11

110 - Operação da Ula com AC e AC, resultando em MEM(MEM = AC * AC)

0000 0000 0000 0000 (0)

->NOP

0000 0000 1000 0000 (9)

->ACbus

0000 0000 0000 1000 (13)

->BUFcar

0000 0010 0000 0000 (7)

->MEMbus

0000 1000 0000 0000 (5)

->DIRcar

0001 0100 0000 0100 (4,6,14)

->PCcar, SelDIR, ULAbus

0000 0101 0000 0000 (6,8)

->SelDIR, MEMcar

0000 0100 0000 0000 (6)

-> SelDIR

1000 0000 0000 0000 (1)

->ICres

111 - Operação da ULA com REG e AC, resultando em MEM (MEM = REG *

AC)

0000 0000 0000 0000 (0)

->NOP

0000 0000 1000 0000 (11)

->REGbus

0000 0000 0000 1000 (13)

->BUFcar

0000 0010 0000 0000 (7)

->MEMbus

0000 1000 0000 0000 (5)

->DIRcar

0001 0100 0000 0100 (4,6,14)

->PCcar, SelDIR, ULAbus

0000 0101 0000 0000 (6,8)

->SelDIR, MEMcar

0000 0100 0000 0000 (6)

-> SelDIR

1000 0000 0000 0000 (1)

->ICres

Siglas

* - Operação da ULA

MEM - Memória do programa

REG - Banco de Registradores

AC - Acumulador

BUF - Buffer da ULA

ULA - ULA

12

DIR - Registrador variável da memória de programa

PC - Registrador de endereço da memória de programa

RI - Registrador de instrução

IC - Contador de instrução

SelDIR - Multiplexador de endereço de memória RAM; (0)End=PC, (1)End=Dir

SelRI - Multiplexador de entrada para IC; (0)IC=IC+1, (1)IC=RI

bus - Sinais de Enable para barramento de dados

car - Sinais de Carga

res - Reseta registrador

PCcar = Esta instrução incrementa PC, fazendo com que ele aponte

para próxima posição de memória da memória de programa.

ICres = Esta instrução reseta IC, fazendo com que o processador execute a

primeira instrução gravada na memória de controle. Ou seja, indica o fim da

instrução corrente.

13

ANEXOS

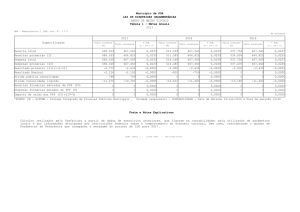

Tabela de seleção de Memória de Controle

$00 -> $03

$01 -> $09

$02 -> $0F

$03 -> $15

$04 -> $1B

$05 -> $21

Tabela das Instruções da Memória de Controle

$00 -> $0000 -> 0000 0000 0000 0000 (0)

->NOP

$01 -> $0200 -> 0000 0010 0000 0000 (7)

->MEMbus

$02 -> $7000 -> 0111 0000 0000 0000 (2,3,4) ->RIcar, SelRI, PCcar

$04 -> $0080 -> 0000 0000 1000 0000 (9)

->ACbus

$05 -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$06 -> $0004 -> 0000 0000 0000 0100 (14) ->ULAbus

$07 -> $0040 -> 0000 0000 0100 0000 (10) ->ACcar

$08 -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

$0A -> $0080 -> 0000 0000 1000 0000 (9)

->ACbus

$0B -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$0C -> $0004 -> 0000 0000 0000 0100 (14) ->ULAbus

$0D -> $0010 -> 0000 0000 0001 0000 (12) ->REGcar

$0E -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

$10 -> $0020 -> 0000 0000 0010 0000 (11) ->REGbus

$11 -> $0080 -> 0000 0000 0000 1000 (13) ->BUFcar

$12 -> $0004 -> 0000 0000 0000 0100 (14) ->ULAbus

$13 -> $0040 -> 0000 0000 0100 0000 (10) ->ACcar

$14 -> $8000 -> 1000 0000 0000 0000 (1)

15

->ICres

$16 -> $0040 -> 0000 0000 0010 0000 (11) ->REGbus

$17 -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$18 -> $0004 -> 0000 0000 0000 0100 (14) ->ULAbus

$19 -> $0010 -> 0000 0000 0001 0000 (12) ->REGcar

$1A -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

$1C -> $0200 -> 0000 0010 0000 0000 (7)

->MEMbus

$1D -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$1E -> $1004 -> 0001 0000 0000 0100 (4,14)->PCcar, ULAbus

$1F -> $0040 -> 0000 0000 0100 0000 (10) ->ACcar

$20 -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

$22 -> $0200 -> 0000 0010 0000 0000 (7)

->MEMbus

$23 -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$24 -> $1004 -> 0001 0000 0000 0100 (4,14) ->PCcar, ULAbus

$25 -> $0010 -> 0000 0000 0001 0000 (12) ->REGcar

$26 -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

$28 -> $0080 -> 0000 0000 1000 0000 (9)

->ACbus

$29 -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$2A -> $0200 -> 0000 0010 0000 0000 (7)

->MEMbus

$2B -> $0800 -> 0000 1000 0000 0000 (5)

->DIRcar

$2C -> $1404 -> 0001 0100 0000 0100 (4,6,14)->PCcar, SelDIR, ULAbus

$2D -> $0100 -> 0000 0001 0000 0000 (8)

->MEMcar

$2E -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

$30 -> $0080 -> 0000 0000 1000 0000 (11) ->REGbus

$31 -> $0008 -> 0000 0000 0000 1000 (13) ->BUFcar

$32 -> $0200 -> 0000 0010 0000 0000 (7)

->MEMbus

$33 -> $0800 -> 0000 1000 0000 0000 (5)

->DIRcar

$34 -> $1404 -> 0001 0100 0000 0100 (4,6,14)->PCcar, SelDIR, ULAbus

$35 -> $0100 -> 0000 0001 0000 0000 (8)

->MEMcar

$36 -> $8000 -> 1000 0000 0000 0000 (1)

->ICres

16

Figura 1 Esquema da ULA internamente.

17

Figura 2 Esquema interno do Somador e Subtrador internamente

Figura 3 Esquema interno do AND internamente

18

Figura 4 Esquema interno do OR internamente

Figura 5 Esquema interno do XOR internamente

19

Figura 6 Esquema interno do NOT internamente

20

Figura 7 Esquema interno do ACUMULADOR internamente

21

Figura 8 Esquema interno do Increment(INCREMENTADOR) internamente

22

Figura 9 Esquema interno do Buffer de 8 bits internamente

23

Figura 10 Esquema interno do Banco de registradores internamente

24

Figura 11 Esquema interno do Program Counter internamente

25

Figura 12 Esquema interno do DIR internamente

26

Figura 13 Esquema interno do Multiplexador.

27

Figura 14 Esquema completo do Simulador.

28

Figura 15 Esquema completo da parte interna da UCP.

29