Aula 16

O inversor TTL

Introdução

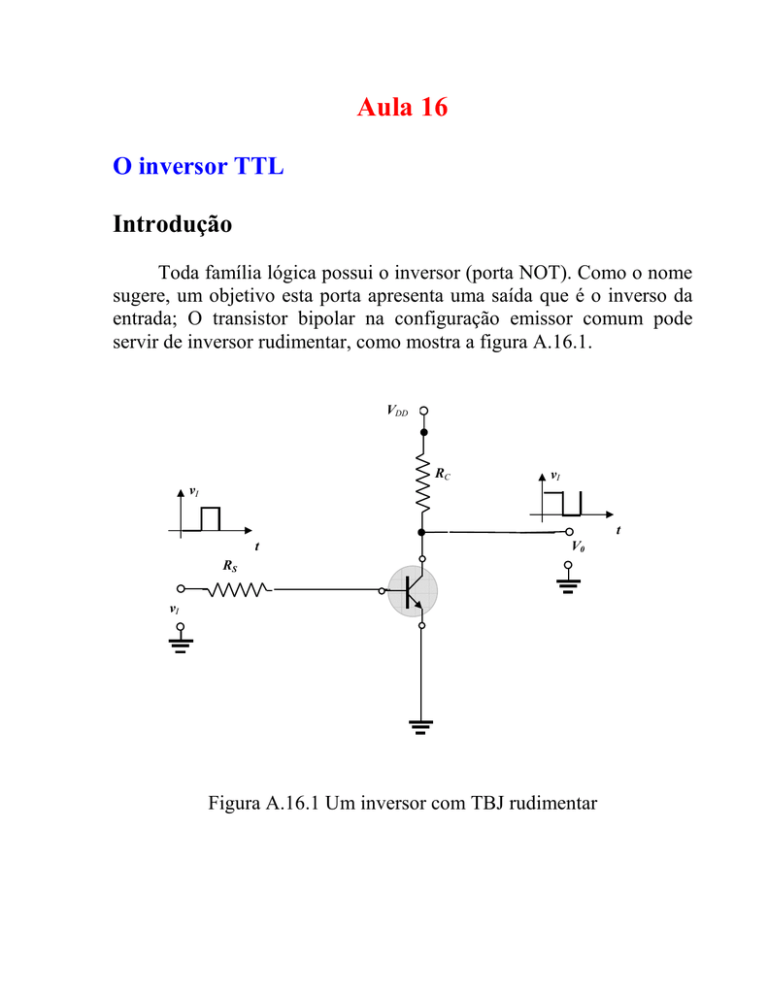

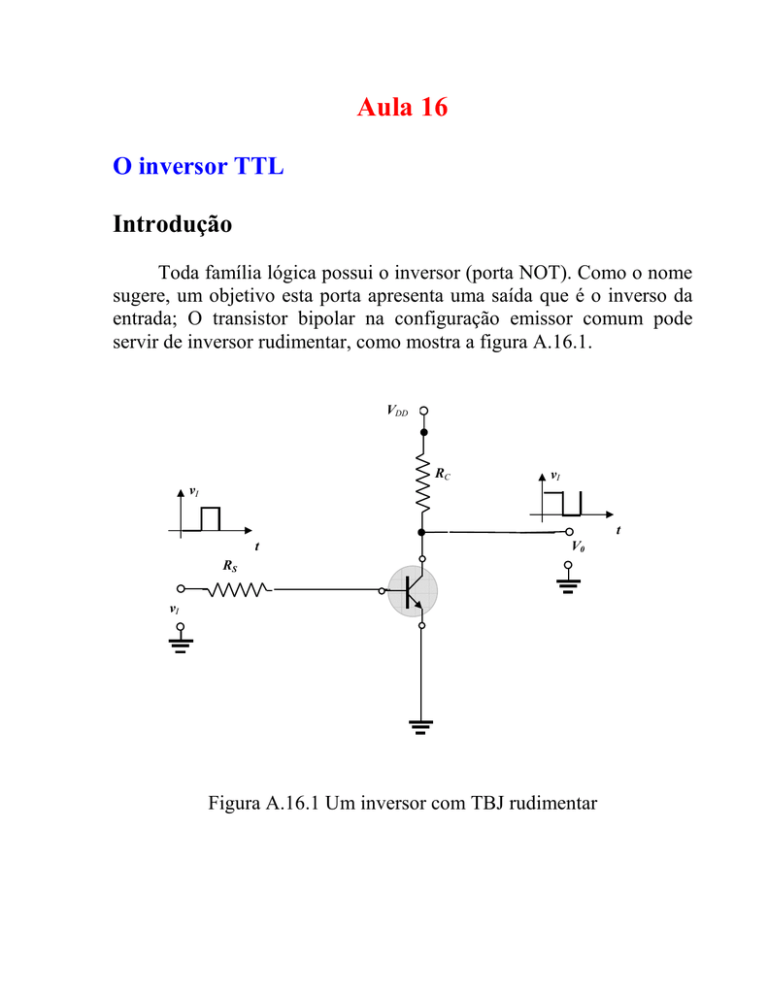

Toda família lógica possui o inversor (porta NOT). Como o nome

sugere, um objetivo esta porta apresenta uma saída que é o inverso da

entrada; O transistor bipolar na configuração emissor comum pode

servir de inversor rudimentar, como mostra a figura A.16.1.

VDD

RC

vI

vI

t

t

V0

RS

vI

Figura A.16.1 Um inversor com TBJ rudimentar

Na prática um circuito lógico TTL é um mais elaborado que esse

a fim de conseguirmos as características desejadas em uma porta

digital, como veremos adiante.

Lógica Transistor –Transistor (TTL)

O circuito básico da porta TTL, mostrado na figura A.16.2,

consiste de um transistor com múltiplos emissores de entrada T0 e de

um transistor de saída T1.

O transistor de entrada T0 contém de 2 a 8 emissores e é fabricado

da maneira mostrada na figura A.16.3 a). Verifica-se, na prática, que

este transistor de dois emissores comporta-se de forma muito próxima

com a de dois transistores cujas bases e coletores estejam conectados

como na figura A.16.3 b); entretanto, a configuração de dois emissores

ocupa área muito menor de chip que a ligação em paralelo.

VDD

R

RC

VB0

T0

V0

A

VB1

T1

B

VA

CL

VB

Cb1

Figura A.16.2 Porta TTL básica

Emissor B

Emissor A

N+

N+

Base P

Coletor N

Figura A.16.3 a) Transistor com múltiplo emissores

Coletor

Base

Emissor A

Emissor B

Figura A.16.3 b)equivalente com transistores em paralelo

Funcionamento da porta

Consideremos, inicialmente, que se o sinal de entrada VA estiver

em nível baixo (0,2 V), a junção base emissor de T0 ficará diretamente

polarizada e a corrente fornecida por VDD passará por R, pelar junção

base emissor, e saindo pelo terminal de entrada A. Assim, a tensão de

base do transistor T0 será

VB0 = VBE + VA = 0,7 V + 0,2 V = 0,9 V

Mostraremos que nessa situação T1 está cortado. Se T1 estivesse

conduzindo, a junção base coletor de T0 estaria diretamente polarizada,

de modo que pudesse ser fornecida corrente de base a T1. Para que esta

condição fosse válida seria necessário que a tensão de base fosse VB0 =

VBE1 + VBC0 = 0,7 V + 0,7 V = 1,4 V. Logo, a tensão real de VB0 = 0,9

V não é suficiente para polarizar diretamente as duas junções. Como T0

está saturado devido à sua grande corrente de base, sua tensão de

coletor emissor é de, aproximadamente, 0,2 V. A tensão na base de T1

é, pois, igual à soma da tensão coletor emissor de T0 com a tensão de

emissor VA.

VB1 = VCE0sat + VA = 0,2 V + 0,2 V = 0,4 V

Portanto, T1 está cortado e V0 ≅ VDD; ou seja, V0 está em nível

ALTO. Este resultado permanece válido enquanto qualquer uma das

entradas estiver em nível baixo.

Consideremos, agora, todas as entradas em nível alto (VDD). As

junções base emissor de T0 ficam reversamente polarizada e,

conseqüentemente, não há corrente entrando (ou saindo) no emissor A

nem no emissor B. A junção base coletor de T0, porém fica diretamente

polarizada, o mesmo acontecendo com a junção base emissor de T1.

Nessa situação VDD fornece corrente, através de R, para a base de T1.

Essa corrente é suficiente para saturá-lo, de modo que a tensão de saída

V0 assume o nível baixo (≅ 0,2 V).

A lógica implementada por esta porta é a de um NE (NAND) com

duas entradas, isto e,

V0 = VAVB

(A.16.1)

Outra consideração importante é, quando todas as entradas

passam de nível ALTO para BAIXO, o transistor T1 deve sair da

saturação. Isso é realizado removendo-se as cargas armazenadas na sua

base. A junção base emissor de T0 fica diretamente polarizada e a carga

armazenada na base de T1 flui para o coletor de T0. A remoção dessa

carga é rápida, pois ∆Q / ∆t = I C 0 , e essa corrente de coletor em T0 é

elevada.

Estágio de saída: O elevador ativo de nível

Da seção anterior, vimos que uma vantagem da porta TTL da

figura A.16.2 é a velocidade com que a carga da base do transistor de

saída é removida, quando da comutação da saída de nível BAIXO para

ALTO. Solucionado este problema, a principal limitação restante na

velocidade é o carregamento capacitivo do transistor de saída, indicado,

em linhas tracejadas na figura A.16.2, como CL. Essa capacitância

engloba as capacitâncias das portas alimentadas, a capacitância de saída

de T1 e as capacitância parasita do circuito.

Para reduzir o tempo de carregamento desse circuito substituímos

o resistor RC por uma carga ativa, denominada elevador ativo de nível.

O circuito de uma porta NE de duas entradas, que concretiza isso, está

mostrado na figura A.16.4.

VDD = 5 V

R= 4 kΩ

RC =130 Ω

R1 = 1,64 kΩ

T2

T0

T3

A

D1

B

VA

VB

V0

T1

CL

Cb1

R2 =1 kΩ

Figura A.16.4 Porta NE de duas entradas com estágio de saída totempole.

O transistor multiemissor T0 é o transistor de entrada. T3 atua

como separador de fase, T2 e T1 formam um amplificador totem-pole,

que além de possuir baixa resistência de saída age como préamplificador de potência ou como estágio separador (isolador) de saída.

A função de RC nesse circuito é limitar o pico transitório de

corrente, o qual ocorre quando V0 muda de estado, de BAIXO para

ALTO. Observe que, quando V0 está em nível BAIXO, T2 está cortado

e a corrente em RC é nula. Quando V0 está em nível ALTO, T2 conduz,

mas a corrente é suficiente apenas para alimentar uma carga de saída

típica de cerca de 0,5 mA. No entanto, V0 demora aproximadamente 0,5

a 0,9 ns para mudar de estado e, durante este tempo, a corrente atinge

um valor de pico de 30 mA.

O diodo D1 possibilita a margem de tensão necessária para

garantir que T2 estará cortado quando T3 e T1 estiverem conduzindo.

Os diodos ligados entre os terminais de entrada e o terra não

influem nas condições DC, mas minimizam os indesejáveis transitórios

negativos de ruído.

Exercício:

Para o circuito da figura A.16.4 determine a máxima corrente de

pico quando a saída passa do nível lógico BAIXO para ALTO.

Encontre também o nível lógico alto (VOH).

Lógica E por fio

Se a saída de duas ou mais portas TTL forem interligadas como

mostra a figura A.16.5, é possível implementar a função E (AND) por

fio.

A

X = AB

B

A

C

A

V0 = XY

Y = CD

D

A

Figura A.16.5 Porta E por fio.

Existem portas TTL com saídas em coletor aberto e que são

adequadas para este tipo de ligação. A figura A.16.6 mostra uma porta

NE de duas entradas e saída em coletor aberto. Na prática, todas as

saídas em coletor aberto são interligadas e compartilham um mesmo

resistor elevador RL, como indicado, em linhas tracejadas. O valor deste

resistor depende do número de coletores abertos, da margem de ruído

necessárias, etc.

VDD = 5 V

R= 4 kΩ

RL

R1 = 1,64 kΩ

T2

T0

T3

A

D1

B

VA

VB

T1

Cb1

R2 =1 kΩ

Figura A.16.6 Porta NE de duas entradas com saída em coletor aberto.

Característica de transferência da TTL

A característica de transferência típica da porta TTL da figura

A.16.3 está mostrada na figura A.16.7. A forma da curva é determinada

pela característica da saída em totem-pole e elevador ativo de nível.

Consideraremos, em primeiro lugar, que a entrada VB esteja em 5 V e

que a entrada VA seja menor que a tensão de entrada representada pelo

ponto a na característica, isto é, VA < 0,7 V. Nesse caso os transistores

T3 e T1 estão cortados, T2 conduzindo e a saída esta no nível lógico alto.

A tensão de saída é, aproximadamente, (desprezando-se a pequena

queda em R1)

VOH ≅ VDD – VBE2 – VD1 = 5,0 – 0,7 – 0,7 = 3,6 V

(A.16.2)

Para esta faixa de saída ALTA, há corrente saindo do emissor A

de T0, sendo seu valor determinado essencialmente por VDD e R. Em

nosso exemplo, com VA = 0,2 V,

IA =

VDD − VBE 0 − VA 5 − 0,7 − 0,2

=

≅ 1mA

R

4 x103

A saída da porta conectada ao emissor de A deve ser capaz de

absorver este nível de corrente.

A partir do ponto a começa a região de transição entre a saída alta

e a saída baixa, podendo-se perceber que há dois segmentos de reta com

declividades diferentes. Isso ocorre pelo seguinte motivo: quando VA <

0,7 V, IC = 0 e o transistor T0 está saturado; portanto, VCE0 ≅ 0,2 V.

Deste modo a tensão de base de T3 é VB3 ≅ VA + 0,2 V. Quando VA

cresce para cerca de 0,5 V, a tensão de base de T3 passa para VB3 ≅ 0,7

V e ele começa a conduzir, operando na região linear, com ganho de

base para coletor da ordem de AV ≅ -R1/R2 . T1 ainda está cortado e o

seguindo de emissor T2, conduzindo. Assim, a característica acompanha

a curva de ganho de T3 e apresenta uma declividade de R1/R2 = 1,6 até

atingir o ponto b. Neste ponto a tensão de entrada é VA ≅ 1,4 V, de

modo que há injeção de corrente na base de T1, colocando-o em

condução. Ao mesmo tempo, o coletor de T3 desce, cortando T2. À

medida que a corrente de coletor deste transistor decresce

simultaneamente com o aumento da corrente de base de T1, este é

levado rapidamente à saturação. No ponto c, VA ≅ 1,5 V, T2 está cortado

e a saída, baixa, isto é, na tensão de saturação de T1 (≅ 0,2 V). Além

disso, T0 opera agora no seu modo invertido, já que seu coletor está

grampeado em 1,4 V, enquanto sua tensão de emissor está em um

potencial mais positivo (1,5 V).

V0(V)

4

a

3,6

Declividade = -1,6

3,0

b

2,5

2,0

1,0

c

0,7

1,4 1,5

2,0

VI(V)= VA

Figura A.16.7 Característica de transferência da TTL