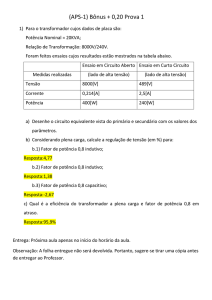

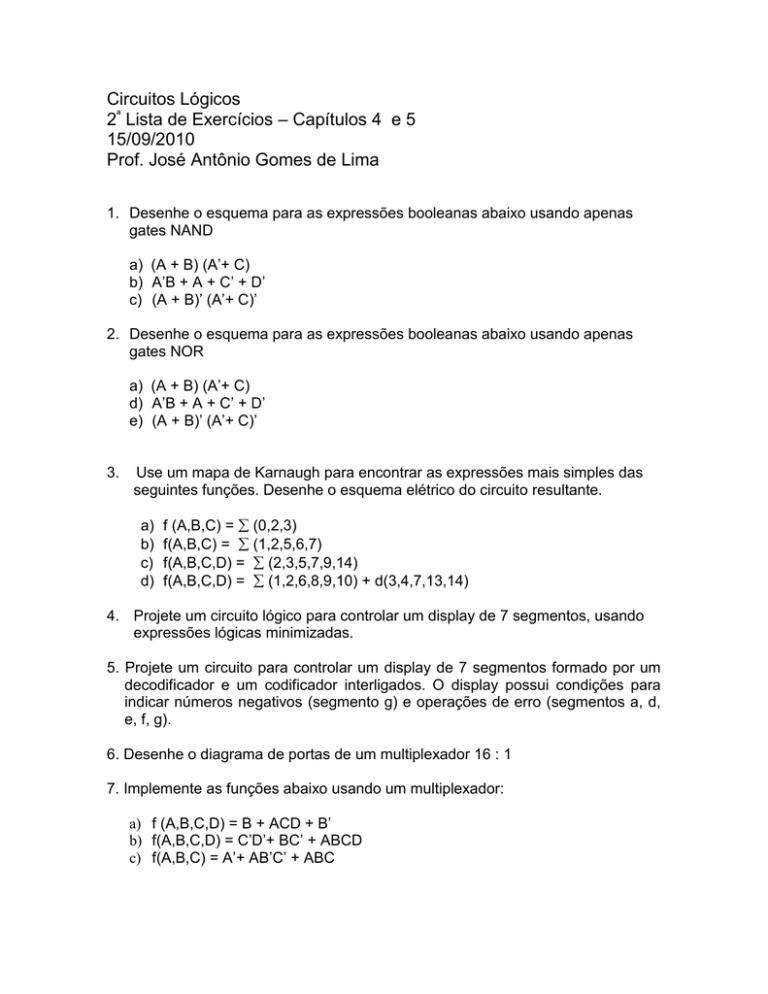

Circuitos Lógicos

2ª Lista de Exercícios – Capítulos 4 e 5

15/09/2010

Prof. José Antônio Gomes de Lima

1. Desenhe o esquema para as expressões booleanas abaixo usando apenas

gates NAND

a) (A + B) (A’+ C)

b) A’B + A + C’ + D’

c) (A + B)’ (A’+ C)’

2. Desenhe o esquema para as expressões booleanas abaixo usando apenas

gates NOR

a) (A + B) (A’+ C)

d) A’B + A + C’ + D’

e) (A + B)’ (A’+ C)’

3.

Use um mapa de Karnaugh para encontrar as expressões mais simples das

seguintes funções. Desenhe o esquema elétrico do circuito resultante.

a)

b)

c)

d)

f (A,B,C) = (0,2,3)

f(A,B,C) = (1,2,5,6,7)

f(A,B,C,D) = (2,3,5,7,9,14)

f(A,B,C,D) = (1,2,6,8,9,10) + d(3,4,7,13,14)

4. Projete um circuito lógico para controlar um display de 7 segmentos, usando

expressões lógicas minimizadas.

5. Projete um circuito para controlar um display de 7 segmentos formado por um

decodificador e um codificador interligados. O display possui condições para

indicar números negativos (segmento g) e operações de erro (segmentos a, d,

e, f, g).

6. Desenhe o diagrama de portas de um multiplexador 16 : 1

7. Implemente as funções abaixo usando um multiplexador:

a) f (A,B,C,D) = B + ACD + B’

b) f(A,B,C,D) = C’D’+ BC’ + ABCD

c) f(A,B,C) = A’+ AB’C’ + ABC

8. A tabela verdade de um subtrator de 1 bit é indicada abaixo:

A

0

0

1

1

B

0

1

0

1

D

0

1

1

0

BL

0

1

0

0

A e B são os bits a serem subtraídos, D é a diferença entre eles e BL indica o

Borrow

( o “vem 1”, análogo ao carry do somador).

Projete um circuito para executar a diferença entre as entradas A e B e descreva

o seu modelo VHDL.

9. Considere o circuito abaixo. Desenhe a forma de onda das saídas do circuito

para as entradas indicadas no diagrama de sinal abaixo. Considere um delay de

5 unidades de tempo para cada gate básico (observe o delay do xnor)

50

A

B

100

10. Considere o circuito abaixo. No tempo t0 a chave é fechada e no tempo t1,

aberta. Desenhe a forma de onda dos pontos internos B e C e da saída do

circuito. Assuma que o delay de cada gate é de uma unidade de tempo.

50

A

t0

100

t1

![1. [5] Desenhe um circuito rectificador de onda completa. Dispõe](http://s1.studylibpt.com/store/data/005153713_1-a81ffab7290038346cfda2c943fa496d-300x300.png)

![1. [2,5] Uma fonte de corrente tem uma intensidade nominal de 100](http://s1.studylibpt.com/store/data/004535512_1-c591a15ee860fabf69226bb4d8d623ed-300x300.png)