EPUSP — PCS 2011/2305/2355 — Laboratório Digital

CARACTERIZAÇÃO DE PORTAS LÓGICAS

Versão 2012

RESUMO

Esta experiência tem como objetivo um estudo dos elementos básicos do nosso universo de trabalho, ou

seja, as portas lógicas. Para isto serão efetuados estudos para determinar algumas características

elétricas destes componentes, como a curva de transferência de tensão, e características temporais,

como os atrasos de propagação. Serão estudados dispositivos TTL e CMOS.

1. PARTE TEÓRICA

1.1. Portas Lógicas e Circuitos Integrados Digitais

As funções lógicas podem ser implementadas de maneiras diversas, sendo que no passado, circuitos com

relés e válvulas a vácuo foram utilizados na execução destas funções. Atualmente, circuitos integrados

(CIs) digitais funcionam como portas lógicas. Esses CIs contêm circuitos formados por resistores, diodos

e transitores miniaturizados, diferenciando-se dos circuitos integrados ditos analógicos pelo fato de que

nos digitais os transistores só possuem dois modos estáveis de operação (corte e saturação), ficando

muito pouco tempo nas regiões de transição. Dizemos, idealmente, que os transistores operam como

chaves.

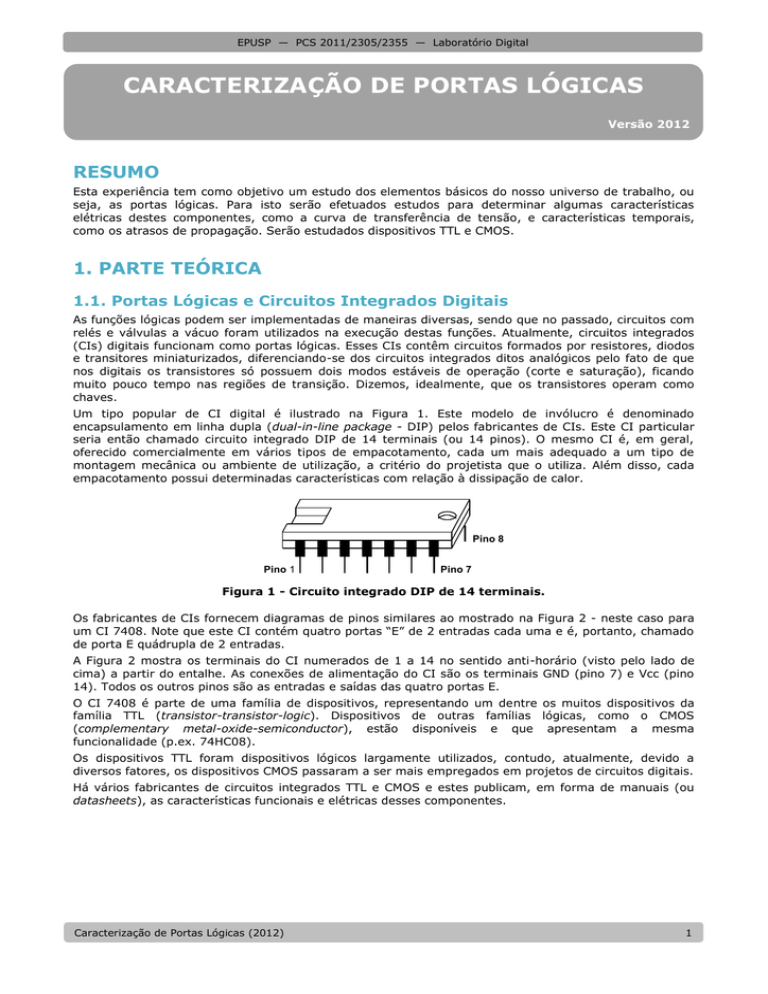

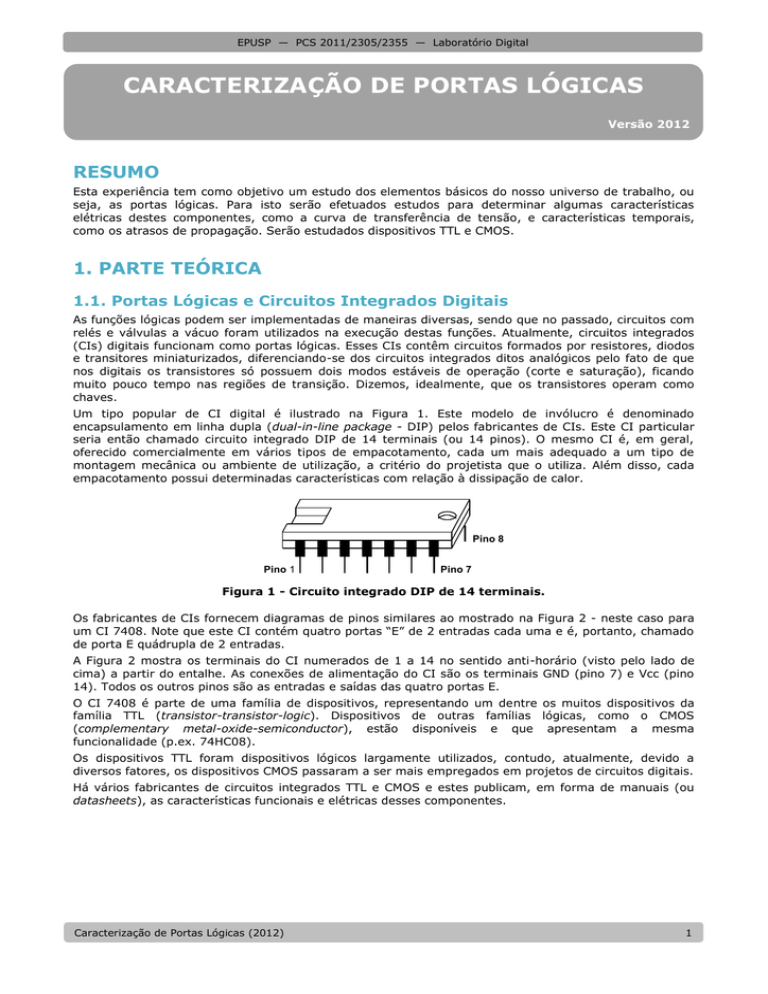

Um tipo popular de CI digital é ilustrado na Figura 1. Este modelo de invólucro é denominado

encapsulamento em linha dupla (dual-in-line package - DIP) pelos fabricantes de CIs. Este CI particular

seria então chamado circuito integrado DIP de 14 terminais (ou 14 pinos). O mesmo CI é, em geral,

oferecido comercialmente em vários tipos de empacotamento, cada um mais adequado a um tipo de

montagem mecânica ou ambiente de utilização, a critério do projetista que o utiliza. Além disso, cada

empacotamento possui determinadas características com relação à dissipação de calor.

Pino 8

Pino 1

Pino 7

Figura 1 - Circuito integrado DIP de 14 terminais.

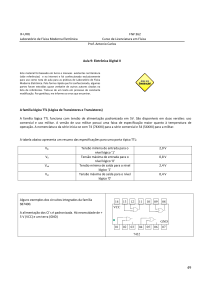

Os fabricantes de CIs fornecem diagramas de pinos similares ao mostrado na Figura 2 - neste caso para

um CI 7408. Note que este CI contém quatro portas “E” de 2 entradas cada uma e é, portanto, chamado

de porta E quádrupla de 2 entradas.

A Figura 2 mostra os terminais do CI numerados de 1 a 14 no sentido anti-horário (visto pelo lado de

cima) a partir do entalhe. As conexões de alimentação do CI são os terminais GND (pino 7) e Vcc (pino

14). Todos os outros pinos são as entradas e saídas das quatro portas E.

O CI 7408 é parte de uma família de dispositivos, representando um dentre os muitos dispositivos da

família TTL (transistor-transistor-logic). Dispositivos de outras famílias lógicas, como o CMOS

(complementary metal-oxide-semiconductor), estão disponíveis e que apresentam a mesma

funcionalidade (p.ex. 74HC08).

Os dispositivos TTL foram dispositivos lógicos largamente utilizados, contudo, atualmente, devido a

diversos fatores, os dispositivos CMOS passaram a ser mais empregados em projetos de circuitos digitais.

Há vários fabricantes de circuitos integrados TTL e CMOS e estes publicam, em forma de manuais (ou

datasheets), as características funcionais e elétricas desses componentes.

Caracterização de Portas Lógicas (2012)

1

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

1A

1

1B

14

VCC

2

13

4B

1Y

3

12

4A

2A

4

11

4Y

2B

5

10

3B

2Y

6

9

3A

GND

7

8

3Y

Figura 2 - Diagrama dos terminais de um CI 7408 visto por cima.

1.2. Parâmetros Elétricos Estáticos da Família TTL

Os circuitos TTL da série 74 foram projetados para operar com tensão de alimentação Vcc = 5,00V 5%,

numa faixa de temperatura de 0oC a 70oC. Para Vcc = 5,00 V, a 25o C, cada porta TTL da série 74

consome, em média, 10mW. Todos os parâmetros apresentados a seguir são garantidos pelos fabricantes

dos circuitos integrados da série 74, se as limitações acima mencionadas forem obedecidas.

Uma característica elétrica de um componente digital é dada pela sua curva de transferência de tensão

(Sedra e Smith, 2000). Esta característica é caracterizado por um gráfico tensão da saída X tensão de

entrada. A figura 3 apresenta um exemplo de uma curva de transferência de um inversor ideal. Repare

que por se tratar de um componente real, a tensão de saída apresenta valores V OL e VOH para os níveis

lógicos baixo e alto, respectivamente.

Figura 3 – Curva característica de transferência de tensão de um inversor ideal.

A figura 4 apresenta a característica de transferência de tensão de uma porta TTL inversora típica. Para

tensões de entrada inferiores a Vb a saída apresenta uma tensão de saída constante igual a 4 V (nível

lógico UM). A partir de Vb, a saída começa a apresentar uma queda de tensão. Quando a tensão de

entrada atinge Vx, a queda se torna mais acentuada, chegando a um nível mínimo em Va. A partir deste

valor, a saída permanece constante (nível lógico ZERO).

Os valores de tensão do gráfico de característica de tensão da figura 4 são, aproximadamente, os

seguintes (estes valores podem variar de dispositivo para dispositivo):

Vb 0,7 V

Vx 1,0 V

Va 1,3V

Nível "UM" 4,0 V

Nível "ZERO" 0,3 V

Caracterização de Portas Lógicas (2012)

2

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

Figura 4 – Característica de transferência típica de uma porta TTL inversora.

Os níveis de tensão garantidos pelos fabricantes e que realmente mostram a compatibilidade entre os

membros da família são apresentados na Tabela I.

Tabela I - Níveis de tensão para uma porta TTL.

PARÂMETRO

DESCRIÇÃO

VALOR

VIL

Máxima tensão na entrada reconhecida como nível ZERO

0,8V

VIH

Mínima tensão na entrada reconhecida como nível UM

2,0V

VOL

Máxima tensão fornecida na saída em nível ZERO

0,4V

VOH

Mínima tensão fornecida na saída em nível UM

2,4V

Analisando-se os valores de tensão constantes da Tabela I, pode-se concluir que os circuitos TTL

admitem, no pior caso, uma margem de ruído CC de 0,4V. Assim sendo, no pior caso, ao nível ZERO

fornecido por uma saída TTL pode-se somar um ruído de amplitude +0,4V, que o sinal resultante ainda é

reconhecido corretamente por uma entrada TTL; no nível UM fornecido por uma saída TTL, pode-se

somar um ruído de amplitude -0,4V, que o sinal resultante ainda se encontra dentro das especificações

de entrada para nível UM. Para valores de tensão compreendidos entre 0,8V e 2,0V, nada se garante com

relação aos níveis lógicos. A figura 5 resume estas considerações.

V OHMin

2,4

2,0

V IHMin

Níveis

Lógicos

V ILMax

0,8

0,4

VOLMax

4,75

5,00

5,25

Tensão de Alimentação

Figura 5 - Margens do ruído e de incerteza (TTL série 74).

Além da compatibilidade entre os níveis de tensão requeridos pelas entradas e fornecidos pelas saídas,

também é necessário examinar os valores das correntes absorvidas e fornecidas pelas entradas e saídas

dos circuitos integrados, tanto em nível UM como em nível ZERO. Para tanto considere o circuito de uma

porta lógica inversora TTL, apresentado na figura 6. Para analisar o circuito, notar que os transistores

apresentados trabalham somente nas regiões de corte e saturação e os valores de corrente contidos na

Tabela II seguem a seguinte convenção:

Corrente absorvida pela porta: positiva.

Corrente fornecida pela porta: negativa.

Caracterização de Portas Lógicas (2012)

3

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

Tabela II - Níveis de corrente (TTL série 74).

PARÂMETRO

DESCRIÇÃO

VALOR

IIL

Corrente máxima fornecida por entrada em nível ZERO

-1,6 mA

IOL

Corrente máxima absorvida por saída em nível ZERO

+16 mA

IIH

Corrente máxima absorvida por entrada em nível UM

+40 A

IOH

Corrente máxima fornecida por saída em nível UM

-400 A

No circuito do inversor lógico da figura 5, quando a entrada estiver em nível UM, o transistor de entrada

T1e está cortado e uma pequena corrente de coletor circula no circuito pela base de T 2e. Este valor é

suficiente para saturar este transistor. A saturação de T2e fornece uma corrente de base de T2s, levando-o

à também saturação e baixar a saída para um valor baixo (VCEsat). A tensão do coletor de T2e é igual a

VBE(T2s)+VCEsat(T2e) 0,9V. Isto garante que tanto o diodo como T1s fiquem cortados. Assim, o transistor

T2s saturado estabelece uma tensão baixa na saída do inversor.

Figura 6 - Análise simplificada do circuito da porta inversora TTL.

Quando a entrada estiver em nível ZERO, o transistor T 1e está saturado, uma vez que a junção baseemissor está diretamente polarizada. Desta forma, a tensão na base de T 1e é de aproximadamente 0,9V e

a tensão na base de T2e é de aproximadamente 0,3V, que é insuficiente para levá-lo à condução. Tem-se

então que o transistor T2e está cortado. Com T2e cortado, a tensão na base de T2s é igual a 0V e desta

forma, T2s também está cortado. Com T2e cortado, não há corrente no coletor de T2e, então a base do

transistor T1s tem um valor suficiente para polarizar diretamente o diodo e T 1s. Nesta situação, T1e está

conduzindo e a tensão na saída é basicamente igual a do emissor. Se a saída estiver em aberto, o valor

da ensão de saída será aproximadamente 3,6V, devido a duas quedas de tensão de 0,7V (pela junção

base-emissor de T1s e pelo diodo).

Para maiores informações sobre a análise do circuito da porta inversora TTL, recomenda-se a consulta

das referências (Sedra e Smith, 2000) e (Tocci, Widmer e Moss, 2007).

Os parâmetros de corrente, entretanto, são válidos somente para entradas e saídas típicas, semelhantes

às da porta analisada. Como existem alguns circuitos integrados TTL da série 74 que apresentam aquelas

correntes com valores diferentes e, também, para facilitar o projeto de sistemas que utilizam outras

séries da família TTL, foram definidos os seguintes parâmetros:

Carga Unitária TTL (UL):

UL = 40 A para nível UM;

UL = 1,6 mA para nível ZERO.

Fan-in - número de ULs requerido pela entrada.

Fan-out - número de ULs fornecido pela saída.

Caracterização de Portas Lógicas (2012)

4

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

Da Tabela II conclui-se que uma saída TTL pode excitar até 10 entradas da mesma família (fan-out).

Outra especificação importante fornecida pelos fabricantes dos circuitos TTL diz respeito à máxima tensão

que pode ser aplicada às entradas. Para a série 74, é recomendado não se colocar níveis de tensão

superiores a 5,5V, pois o circuito pode ser danificado se uma entrada receber uma tensão superior a este

valor.

1.3. Parâmetros Elétricos Estáticos da Família CMOS

Circuitos integrados CMOS (MOS Complementar) são componentes que apresentam as seguintes

características: apresentam as mesmas funções lógicas disponíveis em componentes da família TTL, são

mais rápidos e consomem menos energia (Tocci, Widmer e Moss, 2007). Atualmente, representa a

tecnologia dominante no mercado de semicondutores atual, sendo empregado em processadores,

memórias e outros dispositivos.

A figura 7 apresenta o circuito CMOS de um inversor. Os níveis lógicos CMOS são praticamente +VDD

(para o nível lógico 1) e GND (para o nível lógico 0), pois a saída do circuito está conectado às fontes de

tensão através dos transistores PMOS e NMOS, respectivamente. Por exemplo, a especificação dos

circuitos da série 74HC mostra os seguintes parâmetros: VOH(mín)=4,9V e VOL(máx)=0,1V.

Figura 7 – Inversor CMOS.

A curva de transferência de tensão de um inversor CMOS é apresentada na figura 8 abaixo. Quando os

dois transistores estão casados, ou sejam quando ambos são projetados com parâmetros de

transcondutância idênticos, esta curva é simétrica (Sedra e Smith, 2000). Desta forma, o limiar de

⁄ .

transição Vth do inversor está em

Figura 8 – Curva de transferência de tensão de um inversor CMOS

(fonte: Sedra e Smith, 2000).

Quando ocorre o casamento dos transistores em um inversor CMOS, as margens de ruído MRH e MRL

tornam-se iguais e podem ser de aproximadamente 0,4 VDD. Estas margens de ruído próximas à metade

da tensão de alimentação fazem com que o inversor CMOS tenha um comportamento estático bem

próximo do inversor ideal em relação à imunidade a ruídos.

Outras características elétricas dos componentes CMOS podem ser encontradas nas referências (Tocci,

Widmer e Moss, 2007) e (Sedra e Smith, 2000).

Caracterização de Portas Lógicas (2012)

5

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

1.4. Parâmetros de Tempo

Existem determinadas condições indesejáveis de funcionamento de projetos de sistemas digitais. O

equacionamento lógico obtido para a implementação de um projeto é uma ferramenta suficiente para a

validação lógica do circuito, mas não leva em conta características físicas dos dispositivos, que podem

alterar os resultados teóricos esperados. Uma destas condições diz respeito aos parâmetros de tempo em

circuitos digitais.

Alguns parâmetros de tempo dos dispositivos digitais são:

"Rise time" (tr) - intervalo de tempo necessário para que um sinal vá de 10% do seu valor em

tensão até 90% do seu valor em tensão (figura 9).

90%

10

%

tr

Figura 9 - Tempo de Subida.

"Fall time" (tf) - intervalo de tempo necessário para que um sinal vá de 90% de seu valor em tensão

até 10% do seu valor em tensão (figura 10).

tf

90

%

10

%

Figura 10 - Tempo de Descida.

"Delay time" (td) - intervalo de tempo decorrido entre uma variação de sinal na entrada e a

correspondente variação na saída; toma-se como referência o ponto de 50% do valor de tensão,

conforme mostrado na figura 11.

Entrad

a

50

%

50

%

Saíd

a

td

Figura 11 - Tempo de Atraso.

"Propagation time" (td) - intervalo de tempo decorrido entre uma variação de sinal na entrada e a

correspondente variação na saída; é calculado através da média aritmética dos tempos de

propagação para variação do sinal de saída de BAIXO para ALTO (t PLH) e de ALTO para BAIXO (tPHL),

definidos conforme mostrado na figura 12.

Caracterização de Portas Lógicas (2012)

6

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

Entrada

50%

50%

Saída

tPLH

tPHL

Figura 12 - Tempo de Propagação.

As características acima citadas, aliadas a fatores tais como, o não sincronismo de eventos, podem levar

à geração de sinais indesejáveis em projetos aparentemente corretos. Para que se possa contornar essa

situação deve-se conhecer profundamente todas as características dos componentes que serão utilizados.

1.5. Outras Famílias Lógicas de Circuitos Digitais

Há outras famílias de circuitos integrados digitais que se distinguem entre si pelos tipos de dispositivos

semicondutores que incorporam e pela maneira como os dispositivos são interligados para formar as

portas.

A própria família TTL apresenta várias séries distintas:

74 - série padrão, potência padrão.

74L - baixa potência (low power)

74S - Schottky - mais rápido que o padrão, potência maior que padrão.

74LS - Low Power Schottky - em alguns casos, mais rápido que o padrão, baixa potência.

74F - Fast, mais rápido que o Schottky.

74H - alta velocidade (high speed).

74AS - Advanced Schottky.

74ALS - Advanced Low Power Schottky.

Os dispositivos CMOS (complementary-metal-oxide-semiconductor) compõem o padrão atual. Algumas

famílias CMOS são as seguintes:

4000 – primeira família comercial.

74C – série padrão, componentes funcionalmente similares à família TTL 74.

74HC – High-speed CMOS.

74HCT – High-speed CMOS, TTL compatible, pode ser usada com componentes TTL.

74VHC – Very High-speed CMOS.

74VHCT – Very High-speed CMOS, TTL compatible.

74LVC – Low-voltage CMOS.

74ALVC – Advanced Low-voltage CMOS.

74AUP – Advanced Ultra-low Power CMOS – potência mais baixa e usada em aplicações portáteis.

Outras famílias também encontradas comercialmente são:

BiCMOS – lógica mista bipolar e CMOS.

ECL – lógica acoplada pelo emissor (emitter-coupled-logic).

GaAs – arseneto de gálio (gallium arsenide).

Estas outras famílias não serão tratadas nesta disciplina, mas os conceitos gerais desenvolvidos para os

CIs das famílias TTL e CMOS são prontamente utilizados para estas outras famílias.

Caracterização de Portas Lógicas (2012)

7

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

2. PARTE EXPERIMENTAL

2.1. Atividades Pré-Laboratório

Faça uma pesquisa bibliográfica sobre os componentes TTL e CMOS. Por exemplo, use os manuais dos

componentes 74LS00 (TTL) e 74HC00 (CMOS).

a) Com relação aos parâmetros elétricos:

Quais os valores dos parâmetros elétricos estáticos (V IL, VOL, VIH e VOH)? Monte uma tabela

semelhante à Tabela I.

Apresente a curva de transferência de tensão de um inversor CMOS. Qual a principal diferença

entre esta curva e a da Figura 3?

b) Com relação aos parâmetros relativos ao atraso de propagação:

Quais os valores para tPHL e tPLH?

Determine os valores para tr e tf para um inversor.

Prepare o planejamento de forma a ressaltar estes valores, pois serão usados na parte experimental a

ser executada no Laboratório Digital.

2.2. Característica de Transferência de Tensão

Estudo de Componente TTL

c)

No dispositivo de montagens experimentais, monte o circuito da Figura 13, usando um componente

TTL (por exemplo, 74LS00). Não se esqueça de conectar a alimentação do componente (pinos VCC e

GND).

Fonte de

alimentação fixa

+5Vcc

porta em análise

Vcc

A

Fonte de

alimentação

variável (0 a +5Vcc)

B

Y

7400

GND

7400

carga

Figura 13 - Ensaio de níveis da porta NAND 7400.

d) Com Vcc igual a 5,0V, varie a tensão da fonte ajustável conectada às entradas A e B, desde 0V até

5,0V e levante a curva característica de transferência de tensão como mostrada na figura 3.

[Dicas: elabore um gráfico com os dados medidos e anote o valor de Vcc (medido no pino do

componente) usado no procedimento experimental.]

e) Desconecte as entradas A e B, deixando-as sem ligação alguma. Realize a medida dos níveis de

tensão nas entradas A e B do componente com um multímetro digital. Medir também o valor da

tensão na saída Y. Qual é o nível lógico das entradas A e B correspondente ao nível lógico da saída Y

medida? Justifique no relatório os níveis obtidos (tome por base a figura 4).

f)

(OPCIONAL) Repita o item (d) para Vcc = 4,75V e para Vcc = 5,25V. Compare os resultados e

comente-os no relatório. (DICA: Use uma fonte de alimentação variável na entrada Vcc e uma das

entradas auxiliares F1 ou F2 do painel de montagens.)

Estudo de Componente CMOS

g) Substitua agora a porta lógica TTL por um componente CMOS (por exemplo, 74HC00 1) na montagem

da figura 10.

h) Repita os itens (c) a (f) com este componente CMOS.

Comparação e Análise de Resultados

i)

Compare os resultados experimentais obtidos com o componente TTL e o componente CMOS. Seus

resultados são semelhantes aos dados pesquisados da seção 2.1?

j)

Qual é o valor lógico correspondente a uma entrada em aberto em um componente TTL e um

componente CMOS?

1

Não usar o componente 74HCT00, pois ele pertence a uma família CMOS com níveis de tensão compatíveis com as

famílias TTL.

Caracterização de Portas Lógicas (2012)

8

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

2.3. Medida de Parâmetros de Tempo

Medida do Atraso de Propagação com o componente TTL

k) Para medir os parâmetros de tempo, execute a montagem com o componente TTL conforme a figura

14. A porta em análise tem a entrada X ligada em um gerador de pulsos (use saída TTL) e a saída Y

em outra porta lógica que serve como carga de saída. Ligue também os sinais de entrada X e de

saída Y no osciloscópio para efetuar as medidas de atraso de propagação.

Gerador

de pulsos

Y

X

7400

7400

carga

porta em análise

Figura 14 – Ensaio para medir o atraso de propagação.

l)

Efetuar a medida dos parâmetros tPLH e tPHL. Anote os valores obtidos.

m) Calcule o tempo de propagação tP da porta lógica estudada.

n) Compare os valores pesquisados e experimentais. Comente.

o) Baseado nos parâmetros de tempo pesquisado e medido, qual é o intervalo de valores de frequências

que pode ser usado na porta em análise? Justifique sua resposta.

Medida do Atraso de Propagação com o componente CMOS

p) Substitua agora a porta lógica TTL por um componente CMOS (por exemplo, 74HC00) na montagem

da figura 14.

q) Repita os itens (l) a (o) com este componente CMOS.

Análise dos Resultados

r)

Com base nos valores experimentais obtidos, qual é o maior valor de frequência que pode ser usado

na entrada das portas lógicas estudadas? Justifique sua resposta.

s)

Caso fosse necessário criar um bloco de retardo usando portas lógicas semelhantes aos estudados,

qual o número de portas necessário para se atrasar uma onda quadrada por pelo menos 45 ns?

Justifique sua resposta.

2.4. Interligação de componentes de famílias diferentes

t)

Para verificar o que acontece quando componentes de famílias lógicas diferentes são interligadas em

um circuito digital, execute a montagem com o componente TTL conforme a figura 15. A saída da

porta A deve ser ligada na entrada da porta lógica B. Ligue os sinais de entrada X da porta A na

chave C1, a saída Y da porta A no led L0 e a saída Z da porta B no led L1. Ligue também os sinais Y e

Z no osciloscópio para efetuar as medidas dos respectivos níveis de tensão.

Y

X

7400

porta A

Z

7400

porta B

Figura 15 – Ensaio para verificar a interligação de componentes.

Saída TTL ligada em entrada CMOS

u) Inicialmente use um componente TTL como a porta A e um componente CMOS como porta B. Varie a

chave C1 e anote os valores lógicos e tensões nos vários pontos do circuito.

v) Comente os resultados obtidos, tendo em vista os valores experimentais obtidos. Use os valores

pesquisados do item (a) para justificar seus comentários.

Saída CMOS ligada em entrada TTL

w) Inicialmente use um componente CMOS como a porta A e um componente TTL como porta B. Varie a

chave C1 e anote os valores lógicos e tensões nos vários pontos do circuito.

x) Comente os resultados obtidos, tendo em vista os valores experimentais obtidos. Use os valores

pesquisados do item (a) para justificar seus comentários.

Caracterização de Portas Lógicas (2012)

9

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

3. BIBLIOGRAFIA

FREGNI, Edson e SARAIVA, Antonio M. Engenharia do Projeto Lógico Digital: Conceitos e

Prática. Editora Edgard Blücher Ltda, 1995.

MORRIS, Robert L. e MILLER, JOHN, R. (eds.) Projeto de Circuitos Integrados TTL.

Editora Guanabara Dois, 1978.

SEDRA, Adel S. e SMITH, Kenneth C. Microeletrônica. 4ª edição, Makron Books, 2000.

SIGNETICS. TTL Logic Data Manual, 1982.

TEXAS INSTRUMENTS. The TTL Logic Data Book, 1994.

TOCCI, R. J.; WIDMER, N.S.; MOSS, G.L. Sistemas Digitais: Princípios e Aplicações.

Prentice-Hall, 11a ed., 2011.

WAKERLY, John F. Digital Design: Principles & Practices. 4th edition, Prentice Hall, 2006.

4. MATERIAL DISPONÍVEL

Circuitos Integrados TTL:

74LS00 (TTL) e 74HC00 (CMOS).

5. EQUIPAMENTOS NECESSÁRIOS

1 painel de montagens experimentais.

1 fonte de alimentação fixa, 5V 5%, 4A.

1 fonte de alimentação variável de 0 a 5V 5%, 4A.

1 osciloscópio digital.

1 multímetro digital.

1 gerador de pulsos.

Histórico de Revisões

E.T.M./2001 – revisão

R.C.S./2002 – revisão

E.T.M./2003 – revisão da parte experimental

E.T.M./2004 – revisão

E.T.M. e R.C.S./2005 – reorganização

E.T.M./2011 – revisão

E.T.M./2012 – revisão da parte experimental.

Caracterização de Portas Lógicas (2012)

10