Circuitos Integrados (CIs)

Sistemas Digitais

C.I.: Introdução

}

Conhecido comumente por chip

}

Coleção de resistores, diodos e transistores fabricados em um

pedaço de material semicondutor (geralmente silício) denominado

substrato

Circuito integrado (CI)

visto por dentro e por cima.

Chip

Fios finíssimos

de ligação do chip

aos terminais do CI

Terminais do CI

}

CIs digitais frequentemente são classificados de acordo com a

complexidade de seus circuitos, de acordo com o número de portas

lógicas no substrato

Surgiram na década de 1970 com interesse de miniat5rização dos circuitos 2

C.I.: Vantagens

}

Vantagens dos C.I.s em relação aos circuitos com

componentes discretos

}

Redução de custos, peso e tamanho

}

Aumento da fiabilidade

}

Maior velocidade de trabalho

}

Menor consumo de energia

}

Redução dos erros de montagem

}

Simplifica a produção industrial

A maior par;e do tamanho ex;er>o do CI deve-­‐se à caixa e às ligações do chip aos terFinais ex;er>os Operações em circuitos de baixa potência denominados processamento de inforFação 3

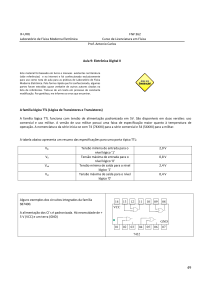

C.I.: Terminologia / Tensão

}

VIH(mín) – Tensão de entrada (input) de nível alto (high-level)

}

}

VIL(máx) – Tensão de entrada (input) de nível baixo (low-level)

}

}

Nível de tensão máximo requerido para um valor lógico 0 na entrada

VOH(mín) – Tensão de saída (output) de nível alto (high-level)

}

}

Nível de tensão mínimo requerido para valor lógico 1 na entrada

Nível mínimo de tensão na saída no estado lógico 1

VOL(máx) - Tensão de Saída (output) de Nível Baixo (low-level)

}

Nível máximo de tensão na saída no estado lógico 0

4

C.I.: Terminologia / Corrente

} IIH

}

} IIL

}

– Corrente de Entrada (input) de Nível Alto (high-level)

Corrente que flui para uma entrada ao aplicar uma tensão de nível alto

– Corrente de Entrada (input) de Nível Baixo (low-level)

Corrente que flui para uma entrada ao aplicar uma tensão de nível baixo

} IOH

}

Corrente que flui da saída no estado lógico 1

} IOL

}

– Corrente de Saída (output) de Nível Alto (high-level)

– Corrente de Saída (output) de Nível Baixo (low-level)

Corrente que flui da saída no estado lógico 0

5

C.I.: Fan-out (Fator de carga)

}

Geralmente, a saída de um circuito lógico precisa acionar várias entradas lógicas

}

}

Fan-out (fator de acionamento de carga)

}

}

Definido como o número máximo de entradas lógicas que uma saída pode acionar com

segurança

Uma porta lógica especificada com fan-out de 10 pode acionar 10 entradas lógicas

}

}

Às vezes todos os CIs em um sistema digital pertencem a uma mesma família lógica,

porém muitos sistemas fazem uso de diversas famílias

Se esse número for excedido, a tensão de nível lógico de saída não pode mais ser

garantida

Depende da natureza das entradas dos dispositivos conectados a uma saída

}

A menos que uma família lógica diferente seja especificada como dispositivo de carga, o

fan-out é relativo a dispositivos de carga da mesma família do dispositivo acionador

6

C.I.: Atraso de propagação

}

O sinal lógico sempre sofre atraso quando atravessa o circuito

}

Os dois tempos de atraso de propagação são definidos como:

}

tPLH: tempo de atraso de ida do estado lógico 0 para 1 (baixo para alto)

}

tPHL: tempo de atraso de ida do estado lógico 1 para 0 (alto para baixo)

Exemplo de atLaso de propagação para um inversor 7

C.I.: Data sheets (especificações técnicas)

}

Folha de dados para o CI TTL porta NAND 74ALS00

8

C.I.: Tipos de cápsulas

}

Utilizados para envolver e proteger os chips

}

}

}

}

Cápsulas com fila de pinos

Cápsulas planas (Flat-pack)

Cápsulas metálicas TO-5 (cilíndricas)

Cápsulas especiais

Cápsulas especiais TO-­‐5 Flat-­‐pack SIL – Single In Line 1

DIL – Dual In Line (DIP) QIL – Quad In Line 1

Enquanto TO-­‐5 são de material metálico, as demais podem ser plásticos ou cerâmico 9

C.I.: Tipos de cápsulas em SMT

}

Existem três tipos básicos de cápsulas de circuitos integrados

em SMT (Surface Mount Technology)

}

SOIC – Small-Outline Integrated Circuit

}

}

PLCC – Plastic-Leaded Chip Carrier

}

}

Semelhante ao DIP em miniatura e com os pinos dobrados

Tem os terminais dobrados para debaixo do corpo

LCCC – Leadless Ceramic Chip Carrier

}

1

Não tem pinos, no lugar existem contatos metálicos moldados na cápsula

cerâmica

10

C.I.: Encapsulamento GA

}

Grid Array (GA)

}

Ball Grid Array (BGA)

}

}

BGA Pin Grid Array (PGA)

}

}

Esferas de contato em grade

Pinos no local de esferas

Land Grid Array (LGA)

}

BGA sem esferas de soldas

LGA 11

C.I.: Encapsulamento / Exemplos

DIP PLCC PGA LGA 12

C.I.: Bases para os chips

}

A base ou soquete, em termos práticos, além de facilitar a

eventual manutenção do circuito, evita o aquecimento do

circuito integrado quando se solda

13

C.I.: Classificação / Aplicação

}

Lineares ou analógicos

}

}

}

Produzem sinais contínuos em função dos sinais que lhe são

aplicados nas suas entradas.

A função principal é a amplificação. Podem destacar-se neste grupo

de CIs os amplificadores operacionais (AmpOp)

Digitais

}

Só funcionam com um determinado número de valores ou estados

lógicos, que geralmente são dois (0 e 1)

Nível lógico 1

Nível lógico 0

Sinal analógico: sinal que tem uma

variação contínua ao longo do tempo.

t

Sinal digital: sinal que tem uma variação por

saltos de uma forma descontínua.

14

C.I.: Classificação / Integração

}

SSI - Small Scale Integration (Integração em pequena escala)

}

}

MSI - Medium Scale Integration (Integração em média escala)

}

}

Número de portas lógicas por CI compreendido entre 10.000 e 99.999

(microprocessadores)

ULSI - Ultra Large Scale Integration (Integração em escala ultra larga)

}

}

Entre 100 e 9.999 portas lógicas por CI (funções lógicas complexas, parte aritmética da

calculadora, relógio digital, etc.)

VLSI - Very Large Scale Integration (Integração em muito larga escala)

}

}

Podem possuir de 12 a 99 portas por CI (decodificadores, contadores, etc)

LSI - Large Scale Integration (Integração em grande escala)

}

}

Possui menos componentes, menos de 12 portas lógicas por CI

Podem possuir entre 100.000 e 999.999 portas lógicas por CI

GSI - Giga Scale Integration (Integração em escala giga)

}

CIs com mais de 1 milhão de portas lógicas por CI

Os níveis de integLação refere-­‐se ao número de por;as lógicas que o CI contém 15

C.I.: Classificação / Família

}

Os C.Is. estão agrupados em famílias lógicas

}

}

Famílias lógicas bipolares

}

}

}

}

}

}

}

Quanto ao tipo de transistores utilizados : bipolar e MOSFET

TTL: Transistor Transistor Logic (Lógica transístor-transístor)

RTL: Resistor Transistor Logic (Lógica de transístor e resistência)

DTL: Díode Transistor Logic (Lógica de transístor e díodo)

HTL: High Threshold Logic (Lógica de transístor com alto limiar)

ECL: Emitter Coupled Logic (Lógica de emissores ligados)

I2L: Integrated-Injection Logic (Lógica de injecção integrada)

Famílias lógicas MOS

}

}

}

CMOS: Complementary MOS (par complementar NMOS/PMOS)

NMOS: Utiliza só transístores MOS-FET canal N

PMOS: Utiliza só transístores MOS-FET canal P

As famílias mais utilizadas são a TTL e CMOS 16

C.I.: Família TTL

}

Subfamílias

}

Limitam-se a características elétricas, tais como a dissipação de

energia e a velocidade de comutação

}

Pinagem e operações lógicas são as mesmas

Velocidade das por;as TTL padrão é limitada pois os TJB sat5rados tem tempo de desligamento considerável. Inclusão do diodo Schoeky evita a sat5ração, aumentando a velocidade 17

C.I.: Família CMOS

}

Consiste de várias séries

}

Executam a mesma função, mas não são necessariamente compatíveis

pino a pino com dispositivos TTL

18

C.I.: Características

TTL CMOS Devido a alta resistência e a capacitância de entLada, o fan-­‐out do CMOS é limitado 19

C.I.: Alimentação e terra

}

Níveis lógicos para dispositivos TTL e CMOS

}

Tensões na faixa indeterminada fornecem resultados imprevisíveis e

devem ser evitadas

* Mais utilizado quando junto ao TTL, mas faixa Vdd varia entLe 3 e 18V CC (corLente contínua) é Vcc em TTL e Vdd no CMOS. O terLa é chamado de GND 20

C.I.: Inversor TTL

INVERSOR TTL

VCC para dispositivos TTL normalmente é +5 V.

Alimentação (VCC) e conexões

de aterramento são necessárias

para a operação de chip.

21

C.I.: Inversor CMOS

VDD para dispositivos CMOS

podem ser +3 até +18 V.

Alimentação (VDD) e conexões

de aterramento são necessárias

para a operação de chip.

INVERSOR CMOS

22

C.I.: Entradas flutuantes (não conectadas)

}

As entradas TTL flutuantes funcionam como uma lógica 1

}

}

A medição da tensão pode parecer indeterminada, mas o dispositivo

se comporta como se houvesse um na entrada flutuante

Entradas flutuantes CMOS podem causar superaquecimento e

danos ao aparelho

}

Alguns CIs têm circuitos de proteção construídos dentro de si

}

A melhor prática é “amarrar” todas as entradas não utilizadas em

nível alto ou baixo

23

C.I.: Diagrama de conexão de circuitos

}

Um diagrama de ligação mostra

}

Todas as conexões elétricas, os números de pinos, os números de

Cis, os valores dos componentes, os nomes de sinais e as tensões de

alimentação

Esse circuito usa por;as lógicas de dois Cis diferentes 24

Resumo

25