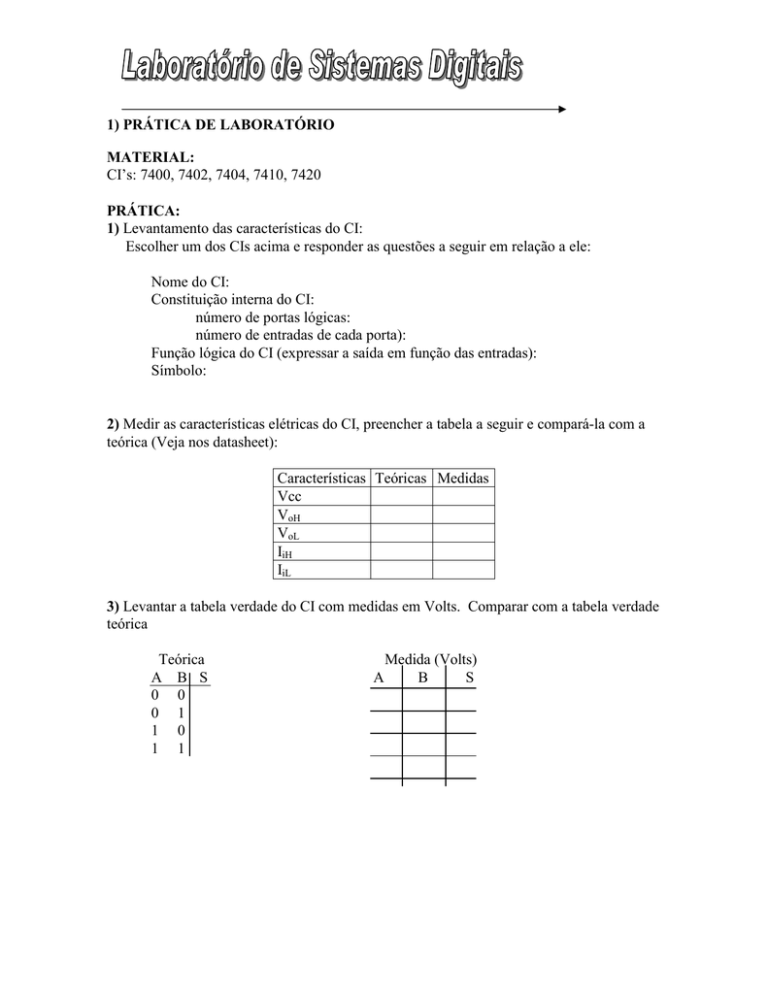

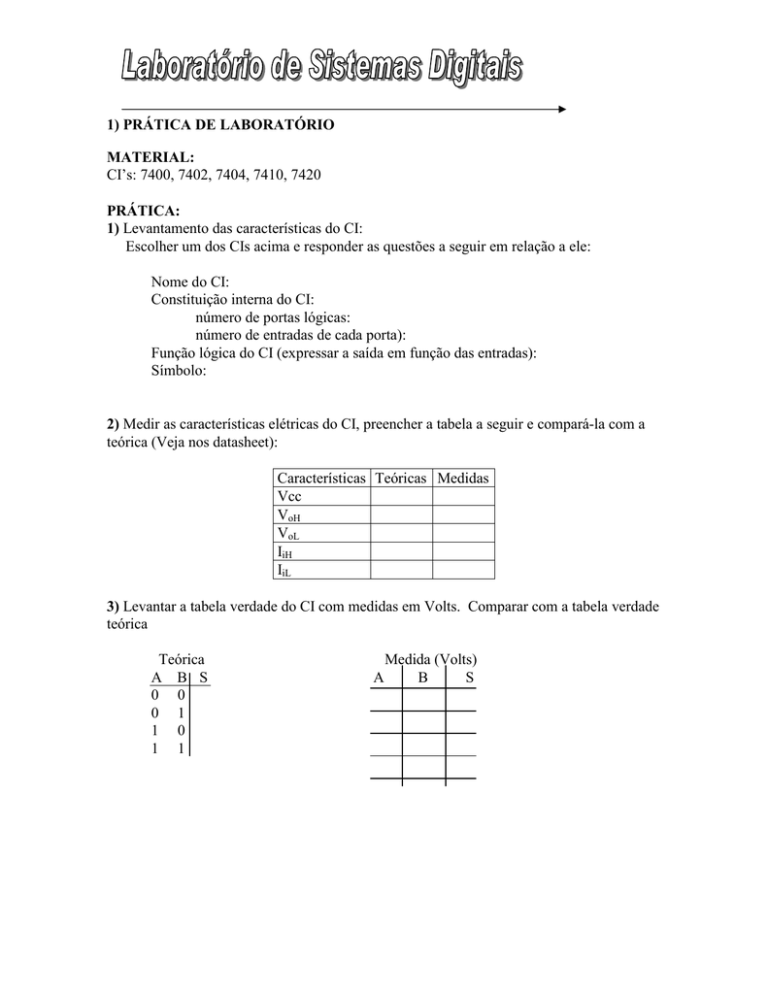

1) PRÁTICA DE LABORATÓRIO

MATERIAL:

CI’s: 7400, 7402, 7404, 7410, 7420

PRÁTICA:

1) Levantamento das características do CI:

Escolher um dos CIs acima e responder as questões a seguir em relação a ele:

Nome do CI:

Constituição interna do CI:

número de portas lógicas:

número de entradas de cada porta):

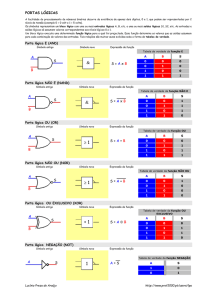

Função lógica do CI (expressar a saída em função das entradas):

Símbolo:

2) Medir as características elétricas do CI, preencher a tabela a seguir e compará-la com a

teórica (Veja nos datasheet):

Características Teóricas Medidas

Vcc

VoH

VoL

IiH

IiL

3) Levantar a tabela verdade do CI com medidas em Volts. Comparar com a tabela verdade

teórica

Teórica

A B S

0 0

0 1

1 0

1 1

A

Medida (Volts)

B

S

Teoria: FAN-OUT

Ao serem ligadas várias portas lógicas à saída de uma única porta (prática 4), todas

da mesma família, a impedância vista pela porta lógica de entrada será menor, acarretando

um aumento da corrente fornecida por esta porta de entrada e, conseqüentemente, uma

alteração das características de limites de tensão de saída. Os fabricantes fornecem então

um número que expressa qual a quantidade máxima de portas da mesma família lógica que

poderá ser conectada à saída de uma porta; esse número é o Fan-out e pode ser obtido pela

expressão:

Fan-out = min(nH, nL)

onde:

nH = IoH/IiH

nL = IoL/IiL

4) Ligue a saída de uma porta NAND (NÃO E) à entrada de quatro outras portas NAND

(NÃO E) como mostra a figura 1.1 e preencha a tabela abaixo. Acrescente mais 4 portas

NAND (NÃO E), e refaça as medidas colocando na tabela abaixo:

Número de

portas

3

7

IoL

IoH

VoL

Figura 1.1 - Esquema de ligação das portas NAND.

VoH

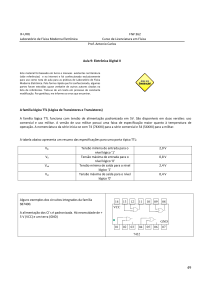

Teoria: Interface TTL e CMOS

Geralmente quando se trabalha com famílias de circuitos lógicos diferentes (TTL e

CMOS), haverá necessidade de se fazer uma interface entre os dois circuitos para torná-los

compatíveis um com o outro, ou seja, temos de assegurar que a característica de saída de

uma porta, que estará acionando outra porta, case com as características de entrada da porta

que está sendo acionada.

Os parâmetros dos dispositivos que precisam ser considerados são: ViH, ViL, VoH,

VoH, IiH, IiL, IoH e IoL, os quais são obtidos dos manuais do fabricantes. A Tabela II mostra os

valores desses parâmetros para as famílias TTL e CMOS.

Tabela II

Parâmetros

ViH (min) (V)

ViL (máx) (V)

VoH (min) (V)

VoL (máx) (V)

IiH (máx) (µ

µA)

IiL (máx) (mA)

IoH (máx) (µ

µA)

IoL (máx) (mA)

74

HCMOS

3,5

1,0

4,9

0,1

1,0

-1,0

-400,0

4,0

74

TTL

2,0

0,8

2,4

0,4

40

-1,6

-400

16

CMOS acionando TTL

Pela tabela II: quando a saída de uma porta lógica CMOS está em nível 1, a tensão

de saída mínima é 4,9 V. Isto é aceitável para acionar circuitos TTL que exigem qualquer

tensão acima de 2,0 V para o nível lógico 1.

Quando a saída da porta CMOS está no nível 0, a tensão de saída máxima sera 0,1

V, que também é aceitável para as portas TTL que necessitam de qualquer tensão de entrada

menor do que 0,8 V para reconhecer o nível lógico zero.

Fan-out da ligação CMOS-TTL

nH = 400 µA/ 40 µA = 10 portas

nL = 4 mA/ 1,6 mA = 2 portas

=> 2 portas no máximo.

(Desenho da figura 1.2(a))

TTL acionando CMOS

Quando a saída da porta TTL está no nível lógico 0, a tensão de saída máxima é 0,4

V, sendo aceitável para a porta CMOS, uma vez que a tensão de entrada para o nível lógico

zero dessa porta é de 1,0 V no máximo.

Quando a saída da porta TTL está no nível lógico 1, a tensão de saída mínima será

de 2,5 V e a porta CMOS necessita no mínimo de 3,5 V. Portanto aqui surge uma

incompatibilidade, que pode ser resolvida usando um resistor Ri como interface como

mostrado no desenho da figura 1.2(b):

Figura 1.2 - Interfaces

CÁLCULO DE Ri:

Ri(min) = [Vcc – VoL(máx)] / IoL(máx)

5) Use um inversor CMOS (CI 74HC04) para acionar um inversor TTL. Varie a tensão na

entrada do CMOS e verifique a tensão na saída do TTL. Monte uma tabela.

6) Use um inversor TTL para acionar um inversor CMOS. Use R=8,2kΩ. Varie a tensão na

entrada do TTL e verifique a saída do CMOS. Monte uma tabela.

2) PRÁTICA DE LABORATÓRIO

Um estacionamento possui duas portas, sendo uma para a entrada dos carros e a outra

para a saída, conforme planta abaixo:

Projete um sistema para automatizar a porta de entrada do estacionamento. Para

controlar o sistema, no estacionamento existem:

- um sensor A que estando em nível alto (A=1) indica que há um automóvel querendo

entrar.

- Um sensor B que estando em nível alto (B=1) indica que existe um automóvel

querendo sair.

- Um sensor C que estando em nível alto (C=0) indica que o estacionamento está

cheio e portanto nenhum carro pode entrar (exceção se houver ao mesmo tempo um

carro querendo sair).

- Saída: Um motor (S=1) para abrir a porta do estacionamento para a entrada dos

carros.

Considere a seguinte interface de potência: