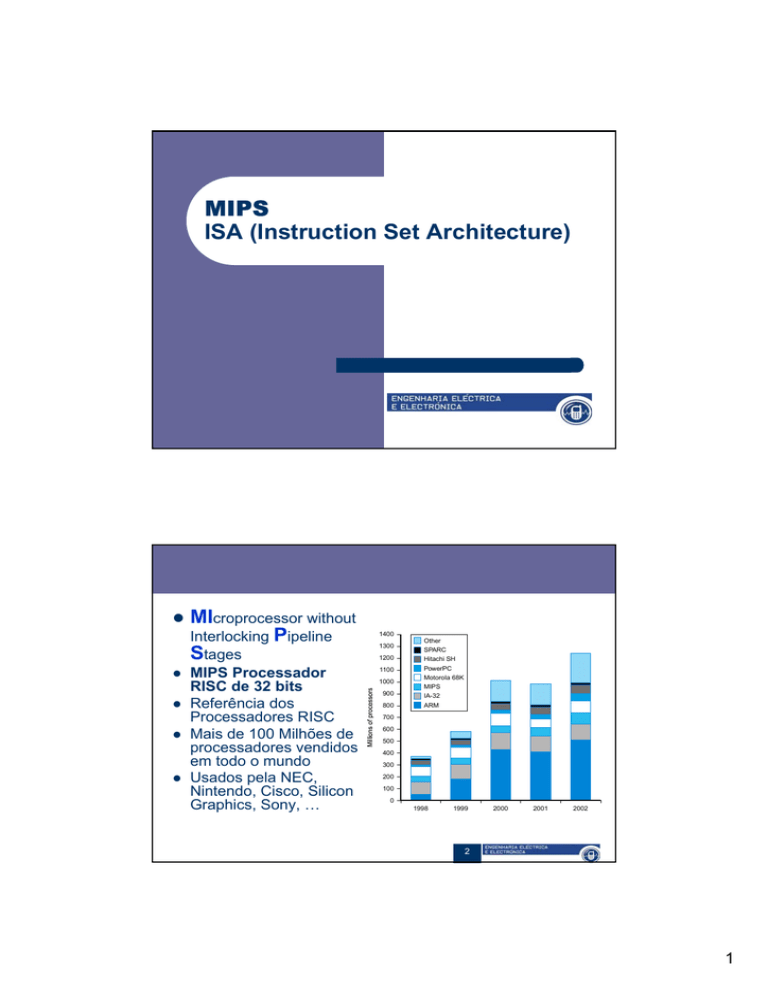

MIPS

ISA (Instruction Set Architecture)

z

z

z

z

z

2

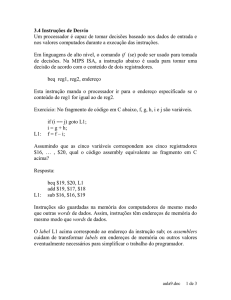

MIcroprocessor without

Interlocking Pipeline

Stages

MIPS Processador

RISC de 32 bits

Referência dos

Processadores RISC

Mais de 100 Milhões de

processadores vendidos

em todo o mundo

Usados pela NEC,

Nintendo, Cisco, Silicon

Graphics, Sony, …

1400

1300

1200

1100

1000

900

800

Other

SPARC

Hitachi SH

PowerPC

Motorola 68K

MIPS

IA-32

ARM

700

600

500

400

300

200

100

0

1998

1999

2000

2001

2002

2

1

MIPS aritmética

z

z

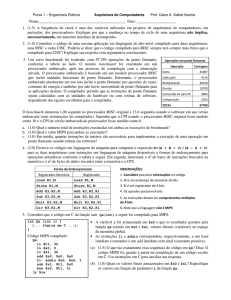

Todas as instruções têm 3 operandos

A ordem dos operandos é fixa,

Mnemónica

Mnemónica

operando3, operando2, operando1

resultado, fonte2, fonte1

Exemplo:

em C:

a = b + c

em MIPS: add a, b, c

3

3

MIPS aritmética

z

z

z

z

4

Principio de funcionamento: a simplicidade favorece a

regularidade.

Em certos casos fica mais complexo:.

C:

a = b + c + d;

MIPS :

add a, b, c

add a, a, d

Operandos são guardados em registos, existem 32

registos.

Os registos são todos de 32 bits.

4

2

Exemplo

z

Em linguagem C, f = (g + h) – (i + j), em que as

variáveis f, g, h, i e j são atribuídas

respectivamente aos registos $s0, $s1, $s2, $s3,

$s4. Qual o correspondente código MIPS?

Resposta:

add

add

sub

$t0, $s1, $s2

$t1, $s3, $s4

$s0, $t0, $t1

5

5

Registos versus Memória

z

Os operandos das

instruções aritméticas

devem ser guardados

nos registos

z

Os compiladores

associam as variáveis

com os registos do

processador

z

6

O que acontece com

os programas com

muitas variáveis?

Control

Input

Memory

Datapath

Output

Processor

I/O

6

3

Organização da Memória

z

z

z

A memória é vista como

uma matriz

unidimensional

Um endereço de

memória é um índice

para a tabela

"Byte addressing"

significa que o índice

aponta para um byte na

memória

0

8 bits of data

1

8 bits of data

2

8 bits of data

3

8 bits of data

4

8 bits of data

5 ...

8 bits of data

6

8 bits of data

7

7

Organização da Memória (cont.)

z

z

z

z

z

8

Bytes e words

No MIPS, uma word é 32 bits ou 4

bytes.

232 bytes com byte address de 0

to 232-1 (4 G bytes)

230 words com word address 0,

4, 8, ... 232-4 (1 G word)

Palavras são alinhadas

i.e., a que correspondem os 2

bits menos significativos de uma

word address ?

0

32 bits of data

4

32 bits of data

8

32 bits of data

12

32 bits of data

...

8

4

Organização Física da Memória

z

z

Determina a ordem como são endereçados os

bytes numa palavra

Existem 2 tipos de alinhamento:

–

Big Endian associa ao endereço mais significativo o

byte da palavra menos significativo.

–

Little end associa ao endereço menos significativo o

byte da palavra menos significativo.

9

9

Exemplo Little e Big Endian

double word

word

byte

byte

byte

word

byte

byte

byte

byte

byte

Quais os endereços para Little e Big Endian?

10

10

5

Exemplo Little e Big Endian

Exemplo para: 08AABB10h na memória 100h

Little end

Big endian

100

10

100

08

101

BB

101

AA

102

AA

102

BB

103

08

103

10

104

104

105

105

106

106

11

11

Instruções de acesso Memória

z

z

z

z

z

Instruções de load e store

Exemplo:

C code:

A[12] = h + A[8];

MIPS code:

lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3)

Os registos podem ser referidos pelo nome (i.e., $s2, $t2) em vez de

um numero

As instruções de store têm como destino o primeiro operando (ao

contrário das outras instruções)

Os operandos das instruções aritméticas são em registos e não em

memória!

Não é possível: add 48($s3), $s2, 32($s3)

12

12

6

Exemplo

swap(int v[], int k);

{ int temp;

temp = v[k]

v[k] = v[k+1];

v[k+1] = temp;

}

13

swap:

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

13

z

As instruções aritméticas só em registos

z

Instrução

Significado

add $s1, $s2, $s3

sub $s1, $s2, $s3

lw $s1, 100($s2)

sw $s1, 100($s2)

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 =Memory[$s2+100]

Memory[$s2+100] =$s1

14

14

7

MAPA dos Registos Internos

Nome

Número

Utilização

$zero

0

Constante zero

$at

1

Assembler Temporary

$v0-$v1

2-3

Para resultados de expressões

$a0-$a3

4-7

Argumentos

$t0-$t7

8-15

Temporários

$s0-$s7

16-23

Temporários

$t8-$t9

24-25

Temporários

$k1-$k2

26-27

Reservado para OS Kernel

$gp

28

Ponteiro global

$sp

29

Ponteiro de pilha

$fp

30

Ponteiro de quadro

$ra

31

Endereço de retorno

O Registo PC (Program Counter) não é acessível !!!

15

15

Sintaxe das instruções

z

A instruções são especificadas a:

–

–

–

–

–

16

Nome

Mnemónica

Formato

Operação

Opcode/funct

Nome

Mnemónica

Form

ato

Operação

Opcode/f

unt

add

Add

R

R[rd]=R[rs]+R[rt]

0/20h

16

8

Linguagem Máquina - Formato R

Mnemónica

op

6

Resultado, Operando 1, Operando 2

rs

rt

rd

5

5

5

shamt

5

Funct

6

op: Opcode da Instrução

rs: Primeiro operando (registo)

rt: Segundo operando (registo)

rd: Operando destino. Registo onde fica o resultado da

operação

shamt: (Shift Amount) valor de deslocamento em operações

de deslocamento

funct:Function, seleciona a variação do opcode

17

17

Linguagem Máquina

z

Exemplo: add

–

–

z

$t1, $s1, $s2

registos tem números, $t1=9, $s1=17, $s2=18

add tem opcode=0 e funct= 20h

Formato das instruções:

000000 10001 10010

op

18

rs

rt

01001 00000 100000

rd

shamt

funct

18

9

Linguagem Máquina - Formato I

mnemónica

mnemónica

op

operando 2, operando 1, constante

operando 2, endereço (operando 1)

rs

rt

5

5

6

constante ou endereço

16

op: Opcode da Instrução

rs: Primeiro operando (registo)

rt: Segundo operando (registo)

Constante/endereço: indica uma posição de memória

relativa ou uma constante

19

Formato usado pelas instruções de:

- transferência de dados,

- endereçamento imediato

- salto condicional

19

Linguagem Máquina

z

Para as instruções de load-word e store-word,

Qual o principio que deve ser preservado?

Introduz um novo tipo de formato de instruções:

– Tipo-I, para as instruções de transferência de dados e imediato

–

z

Exemplo: lw $t1, 32($s2)

100011 10010 01001 0000 0000 0010 0000

op

rs

rt

16 bit number

Onde está o compromisso?

20

20

10

Exemplo: Instrução Load

op

z

rs

rt

constante ou endereço

Exemplo: lw $t1, 32($s2)

35

18

9

op

rs

rt

32

16 bit number

21

21

Exemplo: adição imediata

op

z

rs

rt

constante ou endereço

Exemplo: addi $s1, $s2, 100

($s1=17, $s2=18, addi opcode=8)

8

18

17

op

rs

rt

001001 10010 10001

22

100

16 bit number

0000 0000 0110 0100

22

11

Instruções Lógicas

z

z

z

z

z

sll

srl

and, andi

or, ori

nor

deslocamento à esquerda

deslocamento à direita

‘e’ lógico

‘ou’ lógico

complementa bits

Exemplo:

sll

$t2, $s0, 4

op

rs

rt

rd

0

0

16

10

23

shamt

funct

4

0

23

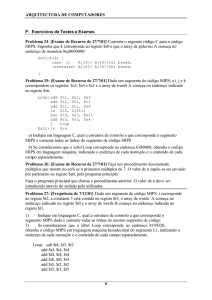

Controlo

z

Instruções que tomam decisões

–

–

altera a sequência de execução,

i.e., muda a próxima instrução a ser executada

Instruções de saltos condicionais:

bne

beq

slt

branch not equal

branch equal

set on less then

Instruções de saltos incondicionais:

j

Jr

Jal

24

jump

jump register

jump and Link

24

12

z

z

bne

beq

slt

slt

j

$t0, $t1,

$t0, $t1,

$t0, $t1,

$t0, $t1,

label

Label

Label

$t2

100

Exemplo: if (i==j) h = i + j;

bne $s0, $s1, Label

add $s3, $s0, $s1

Label:

....

25

z

25

Exemplo:

If ($s2 < $s3)

$s1=1;

else

$s1=0

slt $s1, $s2, $s3

If ($s2 < 100)

$s1=1;

else

$s1=0

slt $s1, $s2, 100

26

26

13

Controlo (cont.)

z

z

MIPS instruções de salto incondicional:

j label

Exemplo:

if (i!=j)

h=i+j;

else

h=i-j;

z

beq $s4, $s5, Lab1

add $s3, $s4, $s5

j Lab2

Lab1:sub $s3, $s4, $s5

Lab2:...

Como fazer um ciclo simples?

27

z

z

27

Instrução

Significado

add $s1,$s2,$s3

sub $s1,$s2,$s3

lw $s1,100($s2)

sw $s1,100($s2)

bne $s4,$s5,L

beq $s4,$s5,L

j Label

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 = Memory[$s2+100]

Memory[$s2+100] = $s1

Next instr. is at Label if $s4 ≠ $s5

Next instr. is at Label if $s4 = $s5

Next instr. is at Label

Formatos:

op

rs

rt

rd

op

rs

rt

16 bit address

op

28

shamt

funct

26 bit address

28

14

Controlo de Fluxo de Programa

z

z

z

BEQ, Branch if Equal

BNE, Branch Not Equal

Nova instrução: SLT, Set Less Then

if

slt $t0, $s1, $s2

z

$s1 < $s2 then

$t0 = 1

else

$t0 = 0

Podemos usar esta instrução para construir "blt

$s1, $s2, Label"

— podem ser construídas estruturas gerais de

controlo

29

29

Endereços em Instruções de saltos

z

Instruções:

bne $t4,$t5,Label

beq $t4,$t5,Label

j Label

z

z

30

Next instruction is at Label if $t4 ≠ $t5

Next instruction is at Label if $t4 = $t5

Next instruction is at Label

Formatos:

I

op

J

op

rs

rt

16 bit address

26 bit address

Os endereços não são de 32 bits

— Como é feito o seu endereçamento com as

instruções load e store?

30

15

SALTOS RELATIVOS

Formato I

6

5

5

16

op

rs

rt

constante ou endereço

beq

$s0, $s1, exit

6

5

5

5

16

15

17

exit

PC= PC+ endereço relativo= PC ± 215

31

31

SALTOS ABSOLUTOS

Formato J

6

26

op

endereço

j L1

6

5

5

5

16

L1

PC= CONCATENAÇÃO (PC : endereço)

32

32

16

Constantes

z

z

Pequenas constantes são usadas muitas frequentemente (50% dos

operandos)

e.g.,

A = A + 5;

B = B + 1;

C = C - 18;

Soluções? Porque não?

–

–

z

Coloca ‘constantes típicas em memoria em carrega-as.

Criação de registos hard-wired (como $zero) para a constante zero.

MIPS Instruções:

addi $29, $29, 4

slti $8, $18, 10

andi $29, $29, 6

ori $29, $29, 4

z

Design Principle: Make the common case fast.

33

Which format?

33

Constantes maiores (32 bits)

z

z

z

Como conseguir carregar um registo de 32 bits com uma

constante.

Devem ser usadas duas instruções

Nova instrução "load upper immediate"

lui $t0, 1010101010101010

1010101010101010

z

filled with zeros

0000000000000000

Falta completar com os bits menos significativs, i.e.,

ori $t0, $t0, 1010101010101010

1010101010101010

0000000000000000

0000000000000000

1010101010101010

1010101010101010

1010101010101010

ori

34

34

17

Sumário MIPS

z

z

z

Todas as instruções têm 32 bits de tamanho

Muito estruturada

Só três formatos de instruções

op

op

rs

rs

op

z

rt

rt

rd

shamt funct

16 bit address

26 bit address

O bom sucesso de uma plataforma depende da

optimização dos compiladores

35

35

MIPS Operandos

MIPS operands

Name

Example

$s0-$s7, $t0-$t9, $zero,

32 registers $a0-$a3, $v0-$v1, $gp,

$fp, $sp, $ra, $at

Memory[0],

230 memory Memory[4], ...,

words

36

Memory[4294967292]

Comments

Fast locations for data. In MIPS, data must be in registers to perform

arithmetic. MIPS register $zero alw ays equals 0. Register $at is

reserved for the assembler to handle large constants.

Accessed only by data transfer instructions. MIPS uses byte addresses, so

sequential w ords differ by 4. Memory holds data structures, such as arrays,

and spilled registers, such as those saved on procedure calls.

36

18

MIPS- Linguagem Asssembly

add

MIPS assembly language

Example

Meaning

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; data in registers

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; data in registers

add immediate

$s1 = $s2 + 100

Used to add constants

load word

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

Word from memory to register

Category

Arithmetic

Instruction

addi $s1, $s2, 100

lw $s1, 100($s2)

sw $s1, 100($s2)

lb $s1, 100($s2)

load byte

sb $s1, 100($s2)

store byte

load upper immediate lui $s1, 100

store word

Data transfer

Conditional

branch

Unconditional jump

37

$s1 = 100 * 2

16

Comments

Word from register to memory

Byte from memory to register

Byte from register to memory

Loads constant in upper 16 bits

branch on equal

beq

$s1, $s2, 25

if ($s1 == $s2) go to

PC + 4 + 100

Equal test; PC-relative branch

branch on not equal

bne

$s1, $s2, 25

if ($s1 != $s2) go to

PC + 4 + 100

Not equal test; PC-relative

$s1, $s2, $s3

if ($s2 < $s3) $s1 = 1;

else $s1 = 0

Compare less than; for beq, bne

set on less than

slt

set less than

immediate

slti

jump

j

jr

jal

jump register

jump and link

$s1, $s2, 100 if ($s2 < 100) $s1 = 1;

Compare less than constant

else $s1 = 0

2500

$ra

2500

Jump to target address

go to 10000

For switch, procedure return

go to $ra

$ra = PC + 4; go to 10000 For procedure call

37

Modos de endereçamento

1.

2.

38

Registo: os operandos são registos

Base ou deslocamento endereçado:

38

19

MIPS – Modos de endereçamento

1. Immediate addressing

op

rs

rt

Immediate

2. Register addressing

op

rs

rt

rd

...

funct

Registers

Register

3. Base addressing

op

rs

rt

Memory

Address

+

Register

Byte

Halfword

Word

4. PC-relative addressing

op

rs

rt

Memory

Address

PC

+

Word

5. Pseudodirect addressing

op

Address

PC

39

Memory

Word

39

20