Prova 1 – Engenharia Elétrica

Arquitetura de Computadores

Prof. Celso A. Saibel Santos

Nome:____________________________________________ Data: ____________________

1. (1.5) A frequência do clock é uma das variáveis utilizadas em projetos de arquiteturas de computadores, em

particular, dos processadores. Explique por que a mudança no tempo de ciclo de uma arquitetura não implica,

necessariamente, em aumento imediato de desempenho.

2. (1.0) Considere o código de uma mesma aplicação em linguagem de alto-nível compilado para duas arquiteturas,

uma RISC e outra CISC. Poderia se dizer que o código compilado para RISC sempre terá sempre mais bytes que o

compilado para CISC? Explique sua resposta com argumentos convincentes.

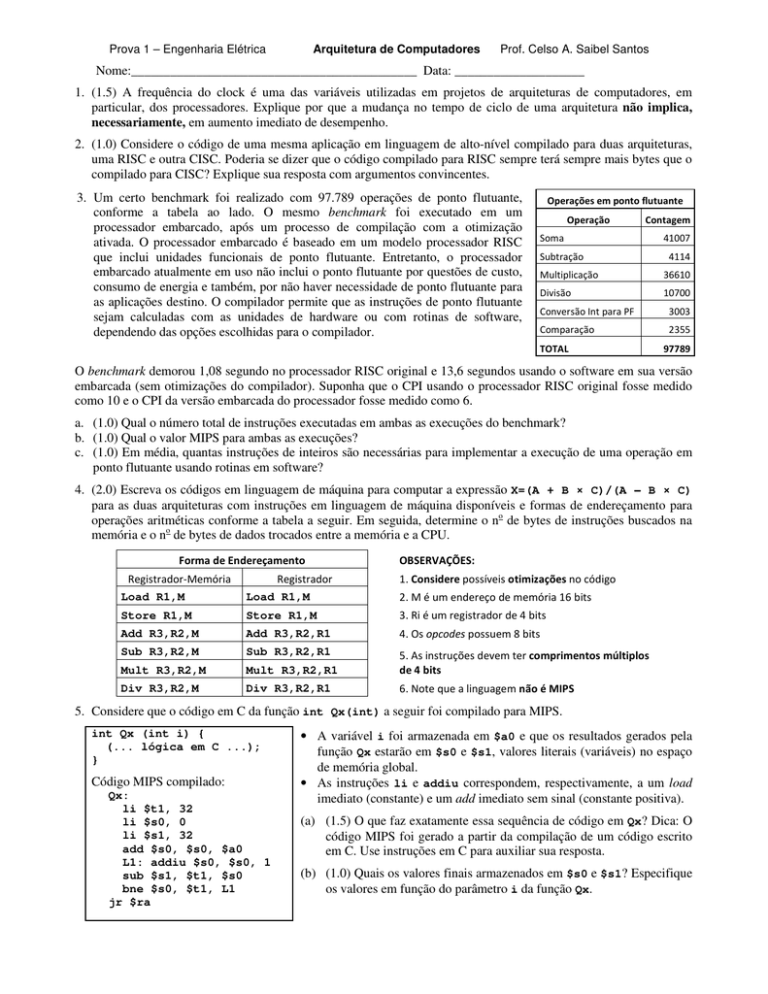

3. Um certo benchmark foi realizado com 97.789 operações de ponto flutuante,

conforme a tabela ao lado. O mesmo benchmark foi executado em um

processador embarcado, após um processo de compilação com a otimização

ativada. O processador embarcado é baseado em um modelo processador RISC

que inclui unidades funcionais de ponto flutuante. Entretanto, o processador

embarcado atualmente em uso não inclui o ponto flutuante por questões de custo,

consumo de energia e também, por não haver necessidade de ponto flutuante para

as aplicações destino. O compilador permite que as instruções de ponto flutuante

sejam calculadas com as unidades de hardware ou com rotinas de software,

dependendo das opções escolhidas para o compilador.

Operações em ponto flutuante

Operação

Contagem

Soma

Subtração

41007

4114

Multiplicação

36610

Divisão

10700

Conversão Int para PF

3003

Comparação

2355

TOTAL

97789

O benchmark demorou 1,08 segundo no processador RISC original e 13,6 segundos usando o software em sua versão

embarcada (sem otimizações do compilador). Suponha que o CPI usando o processador RISC original fosse medido

como 10 e o CPI da versão embarcada do processador fosse medido como 6.

a. (1.0) Qual o número total de instruções executadas em ambas as execuções do benchmark?

b. (1.0) Qual o valor MIPS para ambas as execuções?

c. (1.0) Em média, quantas instruções de inteiros são necessárias para implementar a execução de uma operação em

ponto flutuante usando rotinas em software?

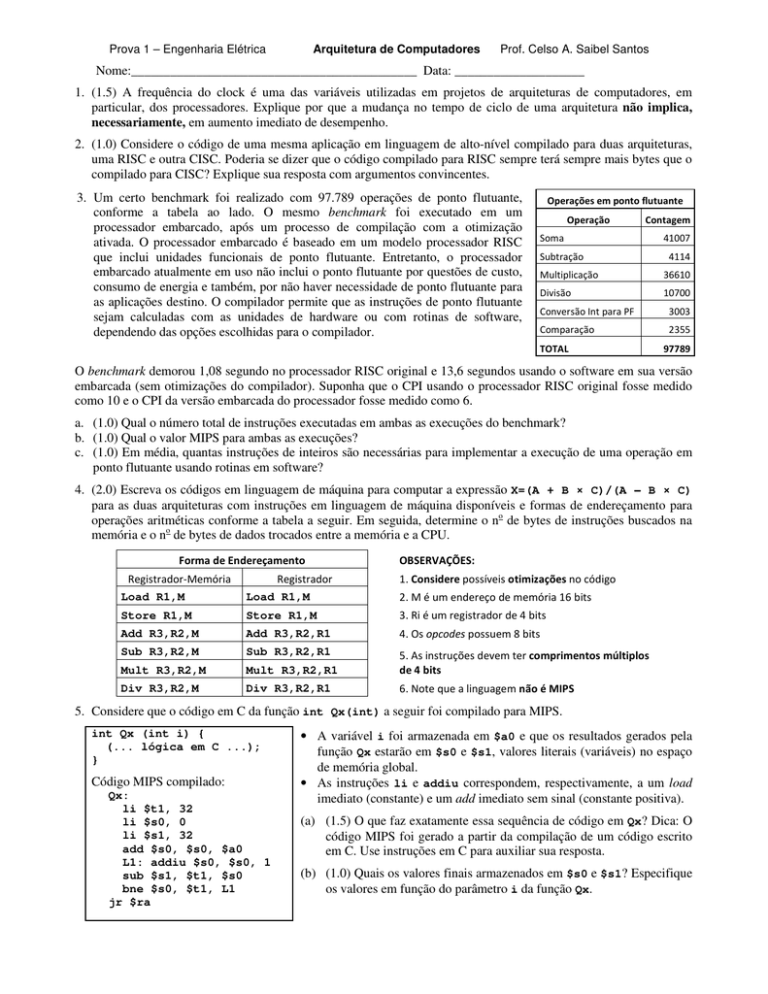

4. (2.0) Escreva os códigos em linguagem de máquina para computar a expressão X=(A + B × C)/(A − B × C)

para as duas arquiteturas com instruções em linguagem de máquina disponíveis e formas de endereçamento para

operações aritméticas conforme a tabela a seguir. Em seguida, determine o no de bytes de instruções buscados na

memória e o no de bytes de dados trocados entre a memória e a CPU.

Forma de Endereçamento

Registrador-Memória

Registrador

OBSERVAÇÕES:

1. Considere possíveis otimizações no código

Load R1,M

Load R1,M

2. M é um endereço de memória 16 bits

Store R1,M

Store R1,M

3. Ri é um registrador de 4 bits

Add R3,R2,M

Add R3,R2,R1

4. Os opcodes possuem 8 bits

Sub R3,R2,M

Sub R3,R2,R1

Mult R3,R2,M

Mult R3,R2,R1

5. As instruções devem ter comprimentos múltiplos

de 4 bits

Div R3,R2,M

Div R3,R2,R1

6. Note que a linguagem não é MIPS

5. Considere que o código em C da função int Qx(int) a seguir foi compilado para MIPS.

int Qx (int i) {

(... lógica em C ...);

}

Código MIPS compilado:

Qx:

li $t1, 32

li $s0, 0

li $s1, 32

add $s0, $s0, $a0

L1: addiu $s0, $s0, 1

sub $s1, $t1, $s0

bne $s0, $t1, L1

jr $ra

• A variável i foi armazenada em $a0 e que os resultados gerados pela

função Qx estarão em $s0 e $s1, valores literais (variáveis) no espaço

de memória global.

• As instruções li e addiu correspondem, respectivamente, a um load

imediato (constante) e um add imediato sem sinal (constante positiva).

(a) (1.5) O que faz exatamente essa sequência de código em Qx? Dica: O

código MIPS foi gerado a partir da compilação de um código escrito

em C. Use instruções em C para auxiliar sua resposta.

(b) (1.0) Quais os valores finais armazenados em $s0 e $s1? Especifique

os valores em função do parâmetro i da função Qx.

Prova 2 – Ciência e Engenharia Computação

Arquitetura de Computadores

Prof. Celso A. Saibel Santos

Nome:____________________________________________ Data: ____________________

1. (6.0) Considere a arquitetura básica de uma CPU monociclo conforme esquema abaixo:

1,3ns

1,3ns

0 M

U

1 X

D

S1

S2

1ns

2,5ns

1,5ns

2,5ns

0 M

U

1 X

A

0 M

U

1 X

C

0 M

U

1 X

B

Suponha que a seguinte sequência de instruções deve ser executada nesta arquitetura:

Endereço

1000:0000

1000:0004

1000:0008

Instrução

sub $s0,$s1,$s2

sw $s0,64($t0)

sw $s1,0($t0)

Observações

Os registradores $t0-$t7 são numerados de 8 a 15 (temporários) e os de $s0$s7 de 16 a 23 (valores salvos/armazenados).

O opcode de sw é 101011 e o de sub é o 000000, com os bits [5-0] 100010.

(a) (2.0) Acrescente os caminhos de dados e sinais de controle que forem necessários para o funcionamento da

instrução slt $s1, $s2, $s3 (significado: if ($s2<$s3) $s1=1; else $s1=0;). Mostre e explique

as modificações na arquitetura da CPU anterior.

Existem várias soluções para a questão. Vamos apresentar duas:

a.1) Na primeira solução, a ULA foi implementada para executar a instrução slt $s1, $s2, $s3. A função

slt é definida como:

000 … 001 se A < B, i.e. if A – B < 0

A slt B =

000 … 000 se A ≥ B, i.e. if A – B ≥ 0

Neste caso, precisamos apenas conectar a saída da ULA (Resultado) ao registrador destino ($s1) na via de

dados. Todos os bits do valor Resultado serão “0”, exceto o último (bit mais significativo) que terá como valor

o sinal de A – B. Assim, não há modificações no circuito e o controle MemparaReg será “1” no

multiplexador MUXB para permitir a escrita de Resultado em $s1.

a.2) Na outra solução, a ULA trata a execução da instrução slt $s1, $s2, $s3 como uma subtração (sub),

supondo que a operação slt não foi implementada. Se a saída da ULA tiver um valor negativo após a

execução, então o bit mais significativo (MSB) do resultado estaria “setado” (valor=1) e, portanto, $s2-$s3<0

(ou seja, $s2<$s3) fazendo com que $s1=1. Se o MSB do resultado for 0, o resultado é positivo, então

$s1=0. Assim, bastaria usar o bit mais significativo de Resultado para se definir o valor do bit menos

significativo de $s1. Ou seja, $s1 será:

31

0

30

0

29

0

28

0

…

…

2

0

1

0

0

Resultado_31

(b) (1.5) Calcule o tempo de execução total para as três instruções anteriores na CPU monociclo dada. Lembre-se

de calcular inicialmente o valor do clock (fixo) para resolver a questão.

O valor do clock é definido como sendo aquele necessário para a execução da instrução mais lenta, em nosso

caso, a instrução lw. Assim, o valor do período de clock deve ser, no mínimo, de 8,5 ns. Supondo uma

instrução lw rd, imediato(rs)

Tempo de busca da instrução na memória de instruções: 2,5 ns

Tempo de acesso ao registrador de base no banco de registradores: 1 ns

Tempo de execução da operação na ULA para cálculo do endereço: 1,5 ns

Tempo de execução da leitura do dado na memória de dados: 2,5 ns

Tempo de escrita do dado no banco de registradores: 1 ns

Tempo total = período de clock = 8,5 ns

Assim, o tempo total de execução é de 25,5 ns, equivalente a 3 clocks, 1 para cada instrução.

OBS: Considera-se que o pulso de clock é instantâneo para efeitos práticos, isto é, assim que o pulso é emitido,

todos os sinais dependentes dele mudam de valor instantaneamente.

(c) (2.5) Para essas mesmas 3 instruções, mostre no gráfico abaixo em que instantes devem ser emitidos os sinais

pela parte de controle da CPU e os sinais de clock de forma que as instruções sejam realizadas corretamente.

sub <10>

add <10>

add <10>

clock

ULAOp

ULAFonte

LerMem

EscReg

EscMem

FontePC

MemParaReg

RegDest

0ns

5ns

2. (3.0) Considere a arquitetura de uma CPU Multiciclo conforme ilustrado a seguir. Quais os valores (bits) e

ordem cronológica dos clocks envolvidos e de todos os sinais acionados na máquina de estados do controle da

CPU para execução de uma instrução tipo R? Considere que os sinais de habilitação são ativados com nível 1

(isto é, se EscReg=1, o banco de registradores está habilitado para a escrita de um valor). Considere ainda que

ULAOp={soma→00; subtração→01; depende de funct (tipo R)→10}.

jump[31-0]

3. (1.0) Discuta a afirmação: Já que a instrução jump não usa registradores, nem computa valores para definir o

desvio, ela poderia, em tese, estar concluída já no segundo estágio da execução multiciclo. Isso poderia ser feito?

Explique.

Sim, poderia. O endereço do salto é um operador imediato na instrução, fazendo com que não seja necessário usar

a ULA para calcular o endereço do desvio. Por outro lado, um tratamento específico para a instrução jump, que não

é tão frequente nos códigos de aplicação acarretaria um aumento da complexidade da lógica de decodificação, indo

de encontro ao conceito RISC de fazer mais rápido o que é mais frequente. Dessa maneira, a execução das

instruções do tipo jump também acaba sendo feita em 3 estágios de forma a manter inalterado o estágio de

decodificação para todas as instruções.

4. (EXTRA 20% a mais na nota)

a. (10%) Explique com argumentos convincentes, as afirmações: (i) “Não há overflow quando se soma um

número positivo com um negativo” e (ii) “Não há overflow se os sinais são os mesmos numa subtração”.

b. (10%) Considere a representação a seguir para uma implementação “otimizada” do algoritmo de

multiplicação de inteiros binários. Mostre a evolução passo-a-passo da multiplicação de

0000011001000000 * 0000000000101000 (isto é, 1600 * 40 =64000) usando o esquema apresentado

Start

Product0 = 1

1. Test

Product0

Produ ct0 = 0

1a. Add multiplicand to the left half of

the product and place the resul t in

the left half of the Product register

2. Shift the Product register right 1 bit

Multiplic and

16 bits

16nd repetition?

No: < 1 6 repetitions

16-bit A LU

Yes: 16 repeti tions

Done

P roduct

32 bits

S hift right

Write

C ontrol

tes t

Prova 3 – Ciência e Engenharia da Computação

Arquitetura de Computadores

Prof. Celso A. Saibel Santos

Nome:____________________________________________ Data: ____________________

1. (1.5) Implemente os adiantamentos que forem necessários para que o código a seguir não gere bolhas no

pipeline. Considere que nos códigos MIPS indicados na tabela, X é um endereço de memória e Rx é o registrador

que armazena o valor de X. Use a tabela para descrever os estágios de execução de cada uma das instruções a fim

de detectar os conflitos. Insira as conexões necessárias para que seja feito o adiantamento de dados no esquema

de execução do pipeline logo abaixo da tabela.

y ← x + z;

h ← y + x;

lw Rx,x

lw Rz,z

add Ry,Rx,Rz

sw y,Ry

add Rh,Ry,Rx

sw h,Rh

CICLO

0

1

2

3

4

5

6

7

8

9

10

2. (1.5) Um esquema para minimizar os efeitos dos “conflitos de controle” (causados por mudanças no fluxo de

controle durante a execução das instruções) é baseado na predição da ocorrência de desvios. Um esquema

sofisticado de predição trabalha com a hipótese de que desvios para endereços anteriores sempre se realizam e

que desvios para endereços posteriores nunca se realizam. Explique como isso é feito e por que o esquema tem

predição tem uma taxa de acerto tão elevada (benchmarks mostraram taxas de acerto da ordem de 90%).

3. (1.0) Explique como funcionam as políticas do tipo write-through e write-back para garantir a integridade dos

dados em um sistema de memória.

4. (4.5) Considere a representação de uma memória cache conforme esquema abaixo:

(A)

(E)

(D)

(C)

(B)

entradas

a. (2.5) Explique o funcionamento da cache, mencionando obrigatoriamente, os componentes indicados

(A, B, C, D e E) indicados no esquema.

b. (1.0) Mostre qual é o tamanho (em bits) dessa cache.

c. (1.0) Explique por que essa estrutura permite explorar tanto da localidade temporal quanto da espacial.

5. (1.5) A técnica de memória virtual permite que a quantidade de memória necessária para a execução de um único

processo exceda a quantidade total de memória física disponível. Explique como isso é feito.