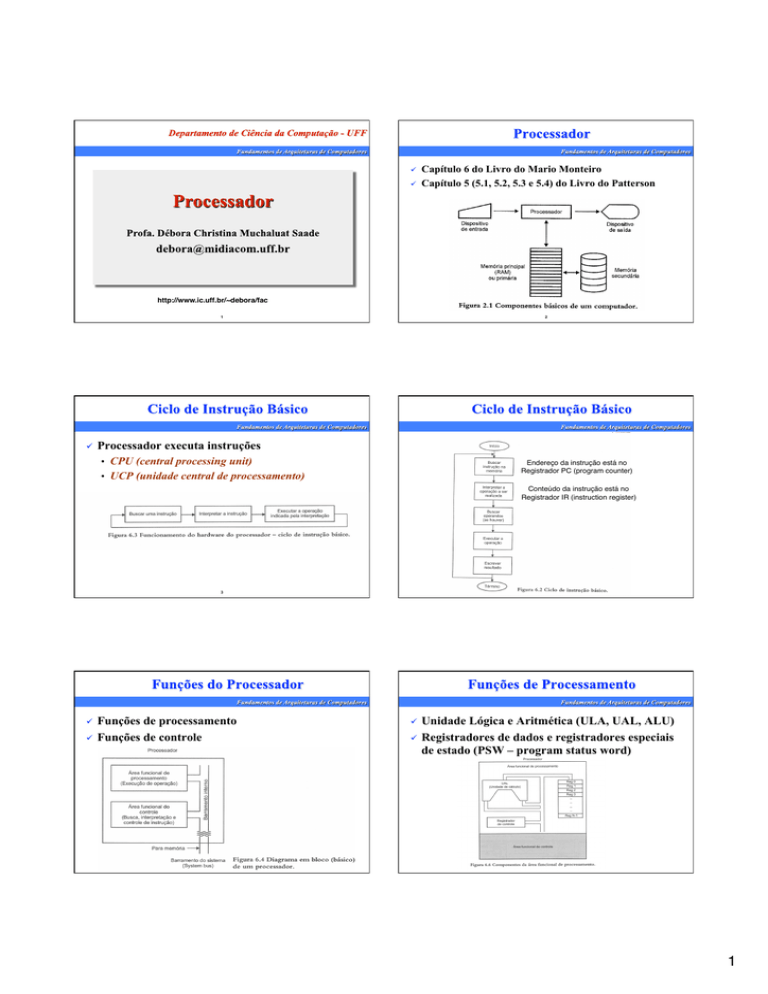

Capítulo 6 do Livro do Mario Monteiro

Capítulo 5 (5.1, 5.2, 5.3 e 5.4) do Livro do Patterson

http://www.ic.uff.br/~debora/fac!

1

2

Processador executa instruções

• CPU (central processing unit)

Endereço da instrução está no !

Registrador PC (program counter)!

• UCP (unidade central de processamento)

Conteúdo da instrução está no !

Registrador IR (instruction register)!

3

Funções de processamento

Funções de controle

5

4

Unidade Lógica e Aritmética (ULA, UAL, ALU)

Registradores de dados e registradores especiais

de estado (PSW – program status word)

6

1!

Unidade de controle, relógio

(clock)

Registradores especiais

• PC – program counter (CI

– contador de instruções)

• IR – instruction register

(RI – registrador de

instrução)

• REM – registrador de

endereços de memória

(MAR)

• RDM – registrador de

dados de memória (MDR)

7

8

MP!

MP!

9

10

MP!

11

Construção do caminho de dados

Controle

Implementação monociclo

12

2!

Conceito de caminho de dados e controle

Caminho dos bits de instrução e dados

Utilização de clock, lógica combinacional e

seqüencial

Começa com uma implementação simples e

iterativamente vai melhorando

Medida de performance baseada em:

• número de instruções

• período do clock

• ciclos de clock por instrução (CPI)

O primeiro é um fator do programa, mas os dois

últimos são baseados na implementação do

processador

13

14

Para simplificar o estudo do projeto do

processador, o foco será dado em um

subconjunto de instruções do MIPS:

• add regA regB destreg

• Memória: lw e sw

31

• Aritmética: add e addi

7 bits

• lw regA regB imm

• sw regA regB imm

• beq regA regB imm

• addi regA regB imm

Desvio utiliza endereço PC relativo (PC + 1 +

imm)

25 24

22 21

0

op

7 bits

3 bits

3 bits

19 18

16 15

3 2

regA

regB

0

3 bits

3 bits

13 bits

0

destreg

3 bits

16

I-Format (tipo I – imediato)

31

22 21

rd op

op: código de operação

regA: registrador com primeiro operando fonte

regB: registrador com segundo operando fonte

destreg: registrador que guarda resultado da operação

15

25 24

0

• Desvio: beq

R-FORMAT (tipo R – registrador)

19 18

16 15

regA regB

3 bits

0

imm

16 bits

3 bits

17

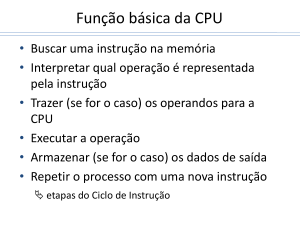

Buscar uma instrução na memória

Interpretar qual operação é representada pela

instrução

Trazer (se for o caso) os operandos para a CPU

Executar a operação

Armazenar (se for o caso) os dados de saída

Repetir o processo com uma nova instrução

etapas do Ciclo de Instrução

18

3!

Duas definições importantes

• Elemento Combinacional - saída depende somente

das entradas

Se le ct

– Exemplo: ALU

Somador

• Elemento Seqüencial: elementos contêm

A

Soma

B

informações de estado

32

32

M

u

x

32

C

Controle da UAL

– Exemplo: Registradores

3

Zero

UAL

19

20

Contém 8 registradores

• Dois barramentos de 32 bits de saída

– Dado lido #1 e Dado lido #2

• Um barramento de 32 bits de entrada

3

Número dos

registradores

• Registrador selecionado por

– Reg a ser lido #1

3

3

Dado

– Reg a ser lido #2

Um barramento de entrada: Dado a ser escrito

Um barramento de saída: Dado lido

Seleção de endereço

EscMem

Endereço

• Endereço seleciona a palavra a ser

– Dado a ser escrito

• Registrador 0 tem o valor 0

Resultado

da UAL

32

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

Dado

lido #1

32

Dado a ser

escrito

colocada em Dado lido

Dados

Dado

lido

LerMem

• Para escrever no endereço, seta EscMem para 1

Dado 32

lido #2

• Para ler do endereço, seta LerMem para 1

EscReg

– Reg a ser escrito seleciona registrador que recebe Dado a ser

escrito quando EscReg=1

21

De acordo com a arquitetura do conjunto de

instruções, define-se uma estrutura

organizacional macro (número de unidades

funcionais, por exemplo)

Essa estrutura é refinada para definir os

componentes do caminho de dados, sua

interconexão e pontos de controle

Estrutura de controle é definida

O projeto do caminho de dados e controle é

refinado para projeto físico e validação

funcional

23

22

Busca a instrução na memória, cujo endereço

está no contador de programa PC

Incrementa o contador de programa PC de 1

1

Somador

PC

Endereço de

leitura

Instrução

Memória de

Instruções

24

4!

add regA regB destreg

• Mem[PC]

Obtém instrução da memória

R[regA] + R[regB] Executa operação

• R[destreg]

de soma

PC + 1

R[destreg]

R[regA] op R[regB]

• Controle da UAL e de EscReg baseado na

instrução decodificada

• PC

Calcula próximo endereço

• Reg a ser lido #1, Reg a ser lido #2, Reg a

ser escrito são regA, regB, destreg

Registradores

3

3

3

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

Operação da UAL

3

Dado

lido #1

Dado

lido #2

Zero

UAL

Resultado

da UAL

EscReg

25

26

lw regA regB imm

• mem[PC]

Busca instrução na

memória

• End

R[regA]+SignExt(imm) Calcula o endereço da

memória

• R[regB] Mem[End]

Carrega os dados no

registrador

• PC PC+1

Calcula o próximo

endereço

Registradores

3

Instrução

Operação da UAL

EscMem

Reg a ser

Dado

lido #1

lido #1

Reg a ser

lido #2

Reg a ser Dado

escrito lido #2

Dado de

escrita

3

3

16

EscReg

Exten16

são

de

sinal

3

Zero Memória

de dados

Resultado

Endereço

Dado

da UAL

lido

UAL

Dado a

ser escrito

32

LerMem

EscReg

3 bits

regA

3 bits

op

7 bits

0

3 bits

regB

16 bits

imediato

27

28

sw regA regB imm

• mem[PC]

Busca instrução na memória

R[regA]+SignExt(imm) Calcula o endereço da

• End

memória

• Mem[End]

memória

• PC PC+1

7 bits

0

Registradores

3

R[regB]

3 bits

op

Carrega os dados na

Instrução

3

3

Calcula o próximo endereço

3 bits

regA

3 bits

regB

29

Reg a ser

Dado

lido #1

lido #1

Reg a ser

lido #2

Reg a ser Dado

escrito lido #2

Dado de

escrita

EscReg

Exten- 32

16

são

de

sinal

Operação da UAL

EscMem

3

Zero Memória

de dados

Resultado

Endereço

Dado

da UAL

lido

UAL

Dado a

ser escrito

LerMem

16 bits

imediato

30

5!

beq regA regB imm

• mem[PC]

Busca instrução na

memória

• Cond

R[regA]-R[regB]

desvio

• if (Cond eq 0)

– PC

PC+1 vindo do caminho de dados de busca de uma instrução

Calcula a condição de

Soma

3

PC+1 + SignExt(imm)

Calcula endereço PC relativo

Instrução

PC+1

3

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

3

• else

– PC

Extensão

de

sinal

16

3 bits

regB

Para a lógica de

controle do desvio

condicional

UAL Zero

Ddo

lido #2

EscReg

3 bits

regA

Operação da UAL

Dado

lido #1

Dado de

escrita

Calcula o próximo endereço

3 bits

op

7 bits

0

Endereço alvo

do desvio condicional

Somador

Registradores

16 bits

imediato

31

32

32

FontePC

32

32

32

32

32

1

PC

Somador

3

M

U

X

Memória

de Instruções

Somador

32

Registradores

3

RegDst

EscReg

16

Registradores

Operação da UAL

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

3

Endereço

de leitura

Instrução

1

UAL fonte

32

EscMem

3

32

Extensão

de

sinal

M

u

x

Zero

Resultado

da UAL

32

UAL

Memória

de dados

Endereço Dado

lido

ULAparaReg

M

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

u

x

32

3

M

3

U

X

RegDst

Dado a

ser escrito

32

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

3

16

32

EscReg

LerMem

33

Resultado

da UAL

Somador

Operação da UAL

EscMem

3

32

UAL fonte

32

M

u

x 32

Extensão

de

sinal

M

u

x

32

Zero

Resultado

da UAL

32

UAL

ULAparaReg

Memória

de dados

Endereço Dado

lido

32

M

u

x

Dado a

ser escrito

32

32

LerMem

34

PC incrementado normalmente

Se instrução for beq

32

• pode adicionar imm a PC + 1

PC +1

32

0

1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

PC

Memória

de Instruções

3

M

u

x

Extensão

de

sinal

35

32

Zero

Resultado

da UAL

UAL

Endereço

de leitura

Instrução

DvC

Resultado

da UAL

32

Registradores

Somador

Operação da UAL

UAL fonte

Somador

M

u

x

32

M

u

x

32

Reg a ser

lido #1

Reg a ser

lido #2

3

Reg a ser

escrito

Dado de

escrita

RegDst

EscReg

3

32

UAL fonte

32

M

U

X

16

M

u

x

Extensão

de

sinal

32

Somador

Operação da UAL

3

32

3

Zero

Resultado

da UAL

UAL

32

1

DvC

EscMem

Memória

de dados

32

Endereço Dado

lido

32

Dado a

ser escrito

ULAparaReg

M

u

x

32

32

LerMem

36

6!

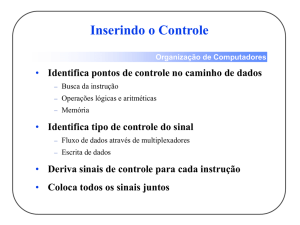

Identifica pontos de controle no caminho de

dados

• Busca da instrução

PC +1

• Operações lógicas e aritméticas

Registradores

• Memória

Endereço

de leitura

Instrução

PC

Identifica tipo de controle do sinal

M

U

X

Memória

de Instruções

• Fluxo de dados através de multiplexadores

RegDst

Deriva sinais de controle para cada instrução

Coloca todos os sinais juntos

37

Registradores

Endereço

de leitura

Instrução

PC

Memória

de Instruções

Somador

Operação da UAL

=op

3

Reg a ser

lido #1

UAL fonte

Reg a ser

=0

Zero

lido #2

Reg a ser

Resultado

M

escrito

da UAL

u

x

Dado de

UAL

escrita

EscReg

=1 16 Exten- 32

são

de

sinal

M

U

X

RegDst

=1

1

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

=X

Reg a ser

lido #1

Reg a ser

UAL fonte

lido #2

=1

0

Reg a ser

M

escrito

u

x

Dado de

1

escrita

EscReg

=0 16 Exten- 32

são

de

sinal

41

DvC= 0

UAL

Resultado

da UAL

Registradores

EscMem =0

DvC

=0

Memória

de dados

Endereço Dado

lido

ULAparaReg

=1

PC

0

M

U

X

Memória

de Instruções

M

u

x

1

Dado a

ser escrito

Endereço

de leitura

Instrução

RegDst

=0

LerMem

=0

Reg a ser

lido #1

Reg a ser

UAL fonte

lido #2

=1

Reg a ser

0

M

escrito

u

x

Dado de

1

escrita

EscReg

=1 16 Exten- 32

são

de

sinal

M

u

x

Somador

Operação da UAL

3

=Add

DvC

=0

Zero

Resultado

da UAL

Memória

de dados

Endereço Dado

lido

UAL

EscMem =0

Dado a

ser escrito

ULAparaReg

=0

0

M

u

x

1

LerMem

=1

40

PC+1

Resultado

da UAL

Registradores

PC

Don’t care

(X)

32

Somador

PC +1

Somador

Extensão

de

sinal

Zero

Resultado

da UAL

M

u

x

39

1

M

u

x

PC +1

Resultado

da UAL

Somador

Somador

Operação da UAL

UAL fonte

38

PC +1

1

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

• Escrita de dados

M

u

x

Resultado

da UAL

Somador

1

M

u

x

1

Registradores

Somador

Operação da UAL

3

=Add

DvC

=0

Zero

Resultado

da UAL

Memória

de dados

Endereço Dado

lido

UAL

Resultado

da UAL

Somador

EscMem =1

Dado a

ser escrito

LerMem

=0

ULAparaReg

=X

M

u

x

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

=X

Reg a ser

lido #1

Reg a ser

UAL fonte

lido #2

=0

Reg a ser

M

escrito

u

x

Dado de

escrita

EscReg

=0 16 Exten- 32

são

de

sinal

M

u

x

Somador

Operação da UAL

3

=Sub

DvC

=1

Zero

Resultado

da UAL

Memória

de dados

Endereço Dado

lido

UAL

EscMem =0

ULAparaReg

=X

M

u

x

Dado a

ser escrito

LerMem

=0

42

7!

PC +1

Resultado

da UAL

Somador

1

Registradores

PC

Endereço

de leitura

Instrução

M

U

X

Memória

de Instruções

RegDst

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

Somador

Operação da UAL

3

UAL fonte

M

u

x

Extensão

de

sinal

Zero

Resultado

da UAL

UAL

M

u

x

DvC

EscMem

Memória

de dados

Endereço Dado

lido

ULAparaReg

M

u

x

Dado a

ser escrito

32

LerMem

43

44

45

46

Vantagens

Desvantagens

• Um ciclo de relógio por instrução torna lógica mais simples

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Instr [24:22] op

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

RegDst

Controle

Principal

UALfonte

ULAparaReg

EscReg

LerMem

EscrMem

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

Somador

Operação da UAL

UAL fonte

M

u

x

Extensão

de

sinal

Zero

Resultado

da UAL

UAL

• Ciclo de clock determinado pela instrução que leva maior

M

u

x

tempo

DvC

– Instrução de carga utiliza cinco unidades funcionais em série

EscMem

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

32

LerMem

ULAparaReg

M

u

x

tempo de acesso à memória de instruções +

• tempo de acesso ao banco de registradores +

• retardo da UAL +

• tempo de acesso à memória de dados +

• tempo de estabilidade dos dados para o banco de registradores

• Duplicação de unidades funcionais

DvC

UAL Op2

48

49

8!

Um programa é escrito em uma linguagem que a

máquina não entende

• Linguagem de alto nível

É necessário traduzir o programa para a

linguagem binária

http://www.ic.uff.br/~debora/orgcomp!

50

51

Programa Fonte em C!

compilador!

Programa em Assembly!

montador!

Código objeto em linguagem binária!

Módulo!

...!

Código objeto em linguagem binária!

Rotina de biblioteca!

Link-editor!

Programa executável!

52

Compilador traduz o programa escrito em linguagem de alto nível

para linguagem de montagem

Compilador executa três funções:

• Análise léxica:

– decompõe o programa fonte em seus elementos individuais distintos

(comandos, operadores, variáveis) e verifica se estão de acordo com as

regras da linguagem

• Análise sintática:

– cria as estruturas para os comandos e verifica a correção das estruturas

(por exemplo, tem int antes de main, tem abre e fecha parênteses)

• Análise semântica:

– verifica as regras semânticas estáticas da linguagem (por exemplo,

estar atribuindo valores do tipo correto para uma variável)

• Ex.: Parcela1=1.5, poderia dar erro pois variável Parcela1 é do tipo int

54

loader!

Memória!

53

Montador realiza a tradução de um programa em

linguagem de montagem (código fonte) para linguagem

binária (código objeto)

Funções básicas:

• Substituir códigos de operações simbólicos por valores

numéricos

• Substituir nomes simbólicos de endereços por valores

numéricos

• Reservar espaço de memória para armazenamento de

instruções e dados

• Converter valores de constantes para binários

• Examinar a correção de cada instrução

55

9!

Link-editor ou ligador

Algumas rotinas já existem codificadas no sistema, por exemplo, rotinas para

entrada e saída de dados, de modo que o programador não precisa codificálas.

Exemplo:

• printf(),

• readln(),

• rotinas matemáticas como seno e cosseno.

Estas rotinas são armazenadas em bibliotecas que são incluídas no código

objeto gerado pelo compilador.

Para que o código da subrotina externa seja anexado ao código objeto utilizase o processo de ligação.

Linguagem interpretada

Realiza as três fases (compilação, ligação e

execução) comando a comando do programa

fonte.

Um programa fonte é executado pelo programa

interpretador.

• Este processo examina todo o código objeto e procura por referências externas

não resolvidas assinaladas pelo compilador.

• Ele procura pela rotina no sistema e, se a encontra, inclui seu código no código

objeto, caso contrário, gera uma mensagem de erro.

56

57

Erros são detectados de forma mais fácil na

interpretação

Utiliza-se mais memória na interpretação porque

interpretador tem que estar na memória

Na interpretação, loop tem que ser traduzido em

todas as iterações

Programas muito utilizados são traduzidos toda

vez que são executados na interpretação

58

10!