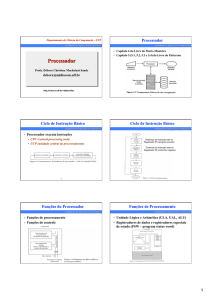

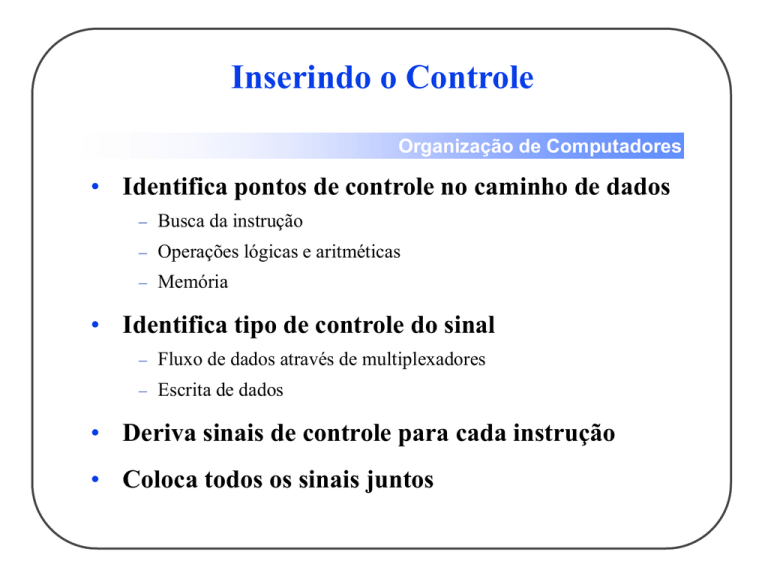

Inserindo o Controle

Organização de Computadores

• Identifica pontos de controle no caminho de dados

– Busca da instrução

– Operações lógicas e aritméticas

– Memória

• Identifica tipo de controle do sinal

– Fluxo de dados através de multiplexadores

– Escrita de dados

• Deriva sinais de controle para cada instrução

• Coloca todos os sinais juntos

Busca da Instrução

Organização de Computadores

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

Somador

Operação da UAL

UAL fonte

M

u

x

Zero

Resultado

da UAL

UAL

Exten- 32

são

de

sinal

M

u

x

Don’t care

(X)

DvC= 0

Controle para Operação Aritmética

Organização de Computadores

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

=1

Somador

Operação da UAL

=op

3

Reg a ser

lido #1

UAL fonte

Reg a ser

=0

Zero

lido #2

Reg a ser

Resultado

M

escrito

da UAL

u

x

Dado de

UAL

escrita

EscReg

=1 16 Exten- 32

são

de

sinal

M

u

x

DvC

=0

EscMem =0

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

LerMem

=0

ULAparaReg

=1

0

M

u

x

1

Controle para Operação de Carga

Organização de Computadores

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

=0

Reg a ser

lido #1

Reg a ser

UAL fonte

lido #2

=1

Reg a ser

0

M

escrito

u

x

Dado de

1

escrita

EscReg

=1 16 Exten- 32

são

de

sinal

Somador

Operação da UAL

3

=Add

Zero

Resultado

da UAL

UAL

M

u

x

DvC

=0

EscMem =0

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

LerMem

=1

ULAparaReg

=0

0

M

u

x

1

Controle para Operação de

Armazenamento

Organização de Computadores

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

Reg a ser

lido #1

Reg a ser

UAL fonte

M

lido #2

=1

U

0

Reg a ser

M

X

escrito

u

x

Dado de

1

escrita

RegDst

=X EscReg

=0 16 Exten- 32

são

de

sinal

Somador

Operação da UAL

3

=Add

Zero

Resultado

da UAL

UAL

M

u

x

DvC

=0

EscMem =1

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

LerMem

=0

ULAparaReg

=X

M

u

x

Controle para Operação de Desvio

Condicional (beq)

Organização de Computadores

PC+1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

Reg a ser

lido #1

Reg a ser

UAL fonte

M

lido #2

=0

U

Reg a ser

M

X

escrito

u

x

Dado de

escrita

RegDst

=X EscReg

=0 16 Exten- 32

são

de

sinal

Somador

Operação da UAL

3

=Sub

Zero

Resultado

da UAL

UAL

M

u

x

DvC

=1

EscMem =0

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

LerMem

=0

ULAparaReg

=X

M

u

x

Sinais de Controle

Organização de Computadores

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

Somador

Operação da UAL

3

UAL fonte

M

u

x

Zero

Resultado

da UAL

UAL

Exten- 32

são

de

sinal

M

u

x

DvC

EscMem

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

LerMem

ULAparaReg

M

u

x

Resumo dos Sinais de Controle

Organização de Computadores

o

p

0

0

0

a

d

d

R

e

g

D

s

t

1

U

A

L

f

o

n

t

e

0

U

L

A

p

a

r

a

R

e

g1

E

s

c

R

e

g

1

L

e

r

M

e

m 0

E

s

c

M

e

m 0

D

v

C

0

U

A

L

O

p

A

d

d

0

1

0

l

w

0

1

0

1

1

0

0

A

d

d

0

1

1

s

w

X

1

X

0

0

1

0

A

d

d

1

0

0

b

e

q

X

0

X

0

0

0

1

S

u

b

Tabela-verdade para os Três Bits de

Controle da UAL

Organização de Computadores

Op2 Op1 Op0

Código

de Operação

Operação

da UAL

lw

0

1

0

010 (soma)

sw

0

1

1

010(soma)

beq

1

0

0

110 (subtração)

Tipo R(add)

0

0

0

010 (soma)

Função de Controle para

Implementação Monociclo

Organização de Computadores

o

p

0

0

0

a

d

d

R

e

g

D

s

t

1

U

A

L

f

o

n

te

0

U

L

A

p

a

r

a

R

e

g1

E

s

c

R

e

g

1

L

e

r

M

e

m

0

E

s

c

M

e

m

0

D

v

C

0

U

A

L

O

p

0

0

U

A

L

O

p

1

1

U

A

L

O

p

2

0

0

1

0

lw

0

1

0

1

1

0

0

0

1

0

0

1

1

s

w

X

1

X

0

0

1

0

0

1

0

1

0

0

b

e

q

X

0

X

0

0

0

1

0

1

1

Implementação da Função de Controle

(PLA)

Organização de Computadores

Entradas

Op2

Op1

Op0

Saídas

Formato R

Iw

sw

beq

RegDst

UALfonte

ULAparaReg

EscReg

LerMem

EscMem

DvC

UALOp2

Juntando as Partes

Organização de Computadores

PC +1

1

Resultado

da UAL

Somador

Registradores

PC

Instr [24:22] op

Endereço

de leitura

Instrução

Memória

de Instruções

M

U

X

RegDst

RegDst

Controle

Principal

UALfonte

ULAparaReg

EscReg

LerMem

EscrMem

DvC

UAL Op2

Reg a ser

lido #1

Reg a ser

lido #2

Reg a ser

escrito

Dado de

escrita

EscReg

16

Somador

Operação da UAL

UAL fonte

M

u

x

Zero

Resultado

da UAL

UAL

Exten- 32

são

de

sinal

M

u

x

DvC

EscMem

Memória

de dados

Endereço Dado

lido

Dado a

ser escrito

LerMem

ULAparaReg

M

u

x

Implementação Monociclo

Organização de Computadores

• Vantagens

– Um ciclo de relógio por instrução torna lógica mais simples

• Desvantagens

– Ciclo de clock determinado pela instrução que leva maior tempo

• Instrução de carga utiliza cinco unidades funcionais em série

tempo de acesso à memória de instruções +

– tempo de acesso ao banco de registradores +

– retardo da UAL +

– tempo de acesso à memória de dados +

– tempo de estabilidade dos dados para o banco de registradores

– Duplicação de unidades funcionais