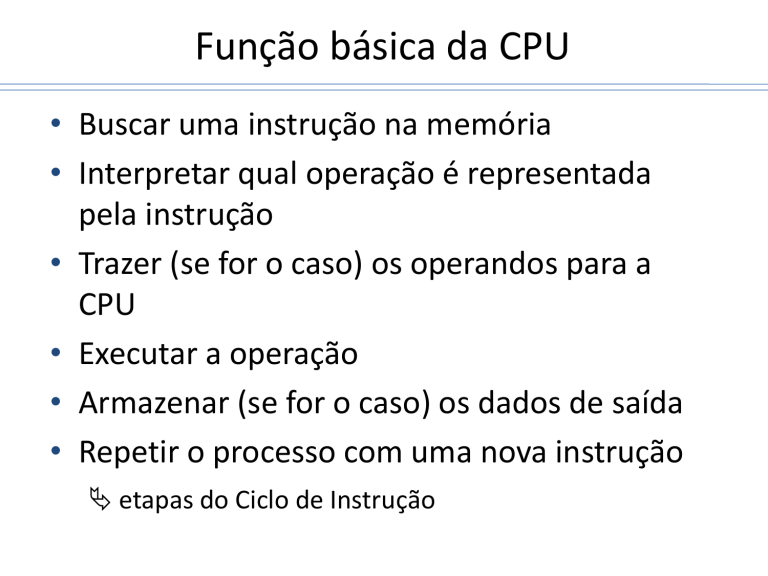

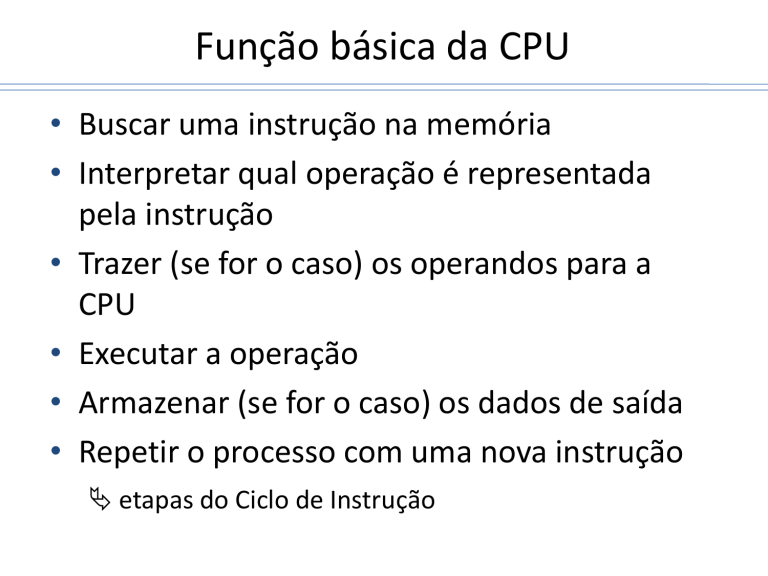

Função básica da CPU

• Buscar uma instrução na memória

• Interpretar qual operação é representada

pela instrução

• Trazer (se for o caso) os operandos para a

CPU

• Executar a operação

• Armazenar (se for o caso) os dados de saída

• Repetir o processo com uma nova instrução

etapas do Ciclo de Instrução

Performance

• Medida de performance baseada em:

– número de instruções

– período do clock

– ciclos de clock por instrução (CPI)

• Clock

– dispositivo gerador de pulsos (medido em Hertz)

– Para cada pulso do relógio se realiza uma microinstrução

• A quantidade de vezes que o pulso se repete

em um segundo define a velocidade do clock

– Freqüência medida em Hertz (1 ciclo por segundo)

Ex: 1 MHertz

Performance

• Número de instruções

– Depende do programa

• Período do clock e ciclos de clock por

instrução

– Dependem da implementação do processador

Implementação da UCP

•

•

•

•

Definir como a instrução

Construção do caminho do dados

Definição da unidade de controle

Começar por uma implementação simples

(cada instrução dura exatamente um

clock) e ir melhorando iterativamente

Unidades da UCP

Composta por 2 tipos de unidades funcionais:

• Elementos que operam sobre valores de

dados

– Ex: ULA (Unidade Lógica e Aritmética) = ALU

• Elementos de estados

– Ex: Registradores e a memória de instruções e

dados

Unidades da UCP

• Elementos “combinacionais”:

– Elementos que operam sobre valores de dados

– Saída depende somente das entradas

– Dado o mesmo conjunto de entradas, produz sempre a

mesma saída

– Saída é uma “combinação” dos dados de entrada

• Elementos “seqüenciais”:

– Elementos de estados

– A saída depende tanto da entrada como do estado interno

do elemento

– Ex: Uma operação no banco de registradores depende

tanto do número do registrador quanto do valor

armazenado no registrador

Elementos necessários para construção da UCP

• Lugar para guardar as instruções do programa

– Memória de instruções (elemento de estados)

• Elementos para guardar o endereço da

instrução

– Program Counter (PC) (elemento de estados)

• Elemento para adicionar 1 ao PC para que este

possa ir para a próxima instrução

– ULA (Unidade Lógica e Aritmética) (elemento

combinacional)

Elementos necessários para construção (I)

• Memória de instruções

Endereço de

leitura

Instrução

• PC

Memória de

Instruções

PC

• ULA só de soma

Somador

Caminho de dados da

Busca da Instrução

• Busca a instrução na memória, cujo endereço

está no contador de programa PC

• Incrementa o contador de programa PC de 1

1

Somador

PC

Endereço de

leitura

Instrução

Memória de

Instruções

Subconjunto de instruções

• O foco será dado em um subconjunto de

instruções:

– Aritmética: add e addi

– Memória: lw e sw

– Desvio: beq

• Para cada instrução iremos definir o caminho de

dados

• O método de implementação das outras

instruções ocorre a partir das instruções básicas

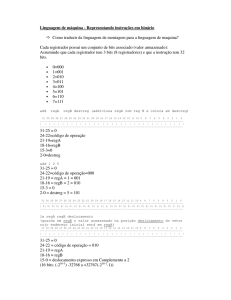

Revisão do Formato das Instruções (I)

• R-FORMAT (lê dois registradores e escreve o resultado

em outro registrador)

– add regA regB destreg

31

25 24

0

7 bits

22 21

19 18

16 15

regA regB

rdop

3 bits 3 bits 3 bits

3 2

0

0

destreg

13 bits 3 bits

op: código de operação

regA: registrador com primeiro operando fonte

regB: registrador com segundo operando fonte

destreg: registrador que guarda resultado da operação

Exemplo: Instrução de Soma

• add regA regB destreg

– Mem[PC]

Obtém instrução da memória

– R[destreg] R[regA] + R[regB]

Executa operação de soma

– PC PC + 1

Calcula próximo endereço

1) Buscar informação dos registradores

2) Somar os valores

3) Guardar informação no registrador

Elementos necessários para construção (II)

• Banco de Registradores com 8 registradores

– Registrador selecionado por

• Reg a ser lido #1

• Reg a ser lido #2

• “Reg a ser escrito” seleciona registro que recebe

“dado a ser escrito” quando EscReg=1

– Um barramento de 32 bits de entrada

• Dado a ser escrito

– Dois barramentos de 32 bits de saída

• Dado lido #1 e Dado lido #2

– Registrador 0 tem o valor 0

Elementos necessários para construção (II)

• Banco de Registradores com 8 registradores

3

No do registrador

Dado

Reg a ser

lido # 1

Reg a ser

lido #2

Dado

lido #1

3

Reg a ser

escrito

Dado

lido #2

32

Dado de

escrita

3

EscReg

32

32

Dado

Elementos necessários para construção (III)

• Elementos Combinacionais

Select (=0 linha de cima,

=1 linha de baixo)

Somador

X

A

Soma = X + Y

Y

32

B

32

M

U

X

32

C

Multiplexador

Controle da ULA

(operação a ser executada)

32

3

Zero Usado para verificar se 2 dados são iguais

ULA

32

Resultado da UAL

32

Caminho de Dados para

Instruções do tipo R-FORMAT

• R[destreg]

R[regA] op R[regB]

– Reg a ser lido #1 = regA, Reg a ser lido #2=regB

– Reg a ser escrito= destreg

– Controle da UAL e de EscReg baseado no código da

instrução

Caminho de Dados para

Instruções do tipo R-FORMAT

• R[destreg]

I

N

S

T

R

U

Ç

Ã

O

R[regA] op R[regB]

Operação da UAL

3

3

3

32

Reg a ser

lido # 1

3

Reg a ser

lido #2

Dado

lido #1

32

Reg a ser

escrito

Dado

lido #2

32

Dado de

escrita

EscReg

UAL

Zero

Resultado da UAL

Revisão do Formato das Instruções (II)

• I-Format (trabalha com imm)

– lw regA regB imm

– sw regA regB imm

– addi regA regB imm

– beq regA regB imm

• Desvio utiliza endereço PC relativo

(PC + 1 + imm)

31

25 24

0

22 21

op

19 18

16 15

regA regB

7 bits 3 bits 3 bits 3 bits

0

imm

16 bits

Exemplo: Instrução de Carga

• lw regA regB imm

– mem[PC]

Busca instrução na memória

32 bits

16 bits

– End

R[regA]+SignExt(imm) Calcula o endereço

da memória

– R[regB] Mem[End] Carrega os dados da

memória no registrador

– PC PC+1

Calcula o próximo endereço

1)

2)

3)

4)

Buscar informação em registrador

Transformar 16 bits em 32 bits

Pegar informação da memória

Guardar informação do registrador

Elementos necessários para construção (IV)

• Extensão de sinal

– Transformar um número com 16 bits em um com

32 bits

– Replicar o bit mais significativo:

– Ex: (2)10 = 0000 0000 0000 0010 (com 16 bits)

0000 0000 0000 0000 0000 0000 0000 0010

– Ex: (-2)10 = inv (0000 0000 0000 0010)+1=

1111 1111 1111 1110 (com 16 bits)

1111 1111 1111 1111 1111 1111 1111 1110

Elementos necessários para construção (IV)

• Extensão de sinal

16

Extensão

de sinal

32

Elementos necessários para construção (V)

• Memória

– Um barramento de entrada: Dado a ser escrito

– Um barramento de saída: Dado lido

• Seleção de endereço

– Endereço seleciona a palavra a ser colocada em

Dado lido ou

endereço no qual o Dado a ser escrito será posto

– Para escrever no endereço, seta EscMem para 1

– Para ler do endereço, seta LerMem para 1

Elementos necessários para construção (V)

• Memória

EscMen

Endereço

Dado

lido

Dado a ser

escrito

LerMem

Caminho de Dados para

Instrução de Carga

• lw regA regB imm

(guarda no regB o dado do endereço de memória regA+imm)

Operação da UAL

3

I

N

S

T

R

U

Ç

Ã

O

3

32

Reg a ser

lido # 1

3

Reg a ser

lido #2

Dado

lido #1

Reg a ser

escrito

Dado

lido #2

Zero

UAL

EscMen

Endereço

Dado a ser

escrito

Dado de

escrita

EscReg

16

32

Extensão

de sinal

32

Dado

lido

LerMem

Exemplo: Instrução de

Armazenamento

• sw regA regB imm

– mem[PC]

– End

Busca instrução na memória

R[regA]+SignExt(imm)

Calcula o endereço

da memória

– Mem[End] R[regB]

Carrega os dados na

memória

– PC PC+1

Calcula o próximo endereço

1)

2)

3)

4)

Buscar informação em registrador

Transformar 16 bits em 32 bits

Pegar informação em registrador

Guardar informação na memória

Caminho de Dados para Instrução

de Armazenamento

• sw regA regB imm

(guarda no enderenço de memória regA+imm o dado de regB)

Operação da UAL

I

N

S

T

R

U

Ç

Ã

O

3

Reg a ser

lido # 1

3

Reg a ser

lido #2

Dado

lido #1

Reg a ser

escrito

Dado

lido #2

3

Zero

UAL

EscMen

Endereço

Dado a ser

escrito

Dado de

escrita

EscReg

16

32

Extensão

de sinal

32

Dado

lido

LerMem

Revisão do Formato de Instrução de Desvio

Condicional (III)

• beq regA regB imm

– mem[PC]

– Cond

Busca instrução na memória

R[regA]-R[regB]

Calcula a condição

de desvio

– if (Cond eq 0)

• PC

PC+1 + SignExt(imm)

Calcula endereço PC

relativo

– else

• PC

PC+1

Calcula o próximo endereço

Caminho de Dados para Instrução

de Desvio Condicional

PC+1 vindo do caminho de dados de

busca de uma instrução

I

N

S

T

R

U

Ç

Ã

O

3

Reg a ser

lido # 1

3

Reg a ser

lido #2

Endereço alvo

do desvio condicional

Somador

Dado

lido #1

UAL

Reg a ser

escrito

Zero

Dado

lido #2

Para a lógica de

controle do desvio

condicional

3

Dado de

escrita

Operação da UAL

EscReg

16

Extensão

de sinal

32

Se R[regA]-R[regB] = 0

o sinal na saída Zero é 1.

Se R[regA]-R[regB] != 0

o sinal na saída Zero é 0.

Passos do Projeto

• Objetivos: projetar um caminho de dados para

possibilitar a execução de todas as instruções

vistas em um único ciclo de clock

• De acordo com a arquitetura do conjunto de

instruções, define-se uma estrutura

organizacional macro.

• Essa estrutura é refinada para definir os

componentes do caminho de dados, suas

interconexões e pontos de controle

Caminho de Dados

• Busca de Instrução + Instruções Aritm. e Lóg. (R-format)

+ Instruções de Referência à Memória (I-Format)

1

P

C

Somador

Endereço de

leitura

Instrução

Operação da UAL

Reg a ser

lido # 1

M

U

X

3

Reg a ser

lido #2

Dado

lido #1

Reg a ser

escrito

Dado

lido #2

Dado de

escrita

Memória de

Instruções

EscReg

16

Extensão

de sinal

Zero

M

U

X

UAL

Endereço

Dado

lido

Dado a ser

escrito

LerMem

32

EscMen

M

U

X

Caminho de Dados

• Busca de Instrução + Instruções Aritm. e Lóg. (R-format)

+ Instruções de Referência à Memória (I-Format) + Desvio

1

M

U

X

Somador

UAL

Reg a ser

lido # 1

P

C

Endereço de

leitura

Instrução

M

U

X

3

Reg a ser

lido #2

Dado

lido #1

Reg a ser

escrito

Dado

lido #2

Dado de

escrita

Memória de

Instruções

16

EscMen

M

U

X

UAL

Endereço

Dado

lido

Dado a ser

escrito

LerMem

EscReg

Extensão

de sinal

DvC

32

M

U

X