Tecnologia TTL

Rodrigo Wobeto de Araujo 993045-0

Samuel Cristiano de Ávila, 993831-1

Resumo: este artigo comenta um pouco sobre o

funcionamento de um dispositivo TLL, as classes de

dispositivos com sua velocidade de chaveamento e

potência dissipada. Também é mensionado os

parametros de sua configuração.

Palavra-chave:

Tecnologia

TTL,

transistor-transistor, Portas lógicas.

1.

Lógica

HISTÓRIA

Existem varias maneiras de projetar

dispositivos eletrónicos lógicos. No anos 30, os

laboratórios da Bell conceberam o primeiro

dispositivo lógico recorrendo a relês. O primeiro

computador digital, “Eniac”, desenvolvido nos

anos 40, utilizava circuitos lógicos baseados em

tubos de vácuo. A invenção do díodo

semicondutor e do transistor bipolar permitiu o

desenvolvimento de sistemas computacionais de

menor dimensão, maior rapidez e maior

capacidade de processamento. Nos anos 60, o

desenvolvimento

tecnológico

permitiu

a

integração de díodos, transistores e outros

componentes eletrónicos num único dispositivo, o

circuito integrado (CI). Surge, assim, a primeira

família de CI’s, baseados no mesmo tipo de

circuitos internos e com características de entrada

e saída semelhantes, com capacidade de

implementar diferentes tipos de funções lógicas.

De entre os vários tipos de circuitos

internos dos CI’s, consequentemente de famílias

lógicas, destaca-se a família TTL (“Transistor –

Transistor Logic”), introduzida nos anos 60 e

utilizada em larga escala. No entanto, 10 anos

antes da invenção do transistor bipolar, foi

patenteado o transistor MOSFET (“ metal-oxide

semicondutor field effect transistor (MOSFET)”

ou apenas transistor MOS. Na altura, era reduzida

a sua aplicabilidade devido à dificuldade de

fabrico e a velocidades reduzidas de operação.

Com os desenvolvimentos tecnológicos nesta área

assiste-se, atualmente, à substituição da tecnologia

TTL pela tecnologia MOS e, particularmente, pela

tecnologia CMOS (“ Complementary MOS”).

Hoje em dia, a grande maioria dos circuitos com

níveis de integração em larga escala, tais como

memórias e microprocessadores, utilizam a

tecnologia CMOS. No entanto, devido à grande

popularidade dos CI’s TTL, a maioria das famílias

CMOS são projetadas de modo a serem parcial ou

mesmo totalmente compatíveis com a família

TTL.

2.

CIRCUITOS INTEGRADOS

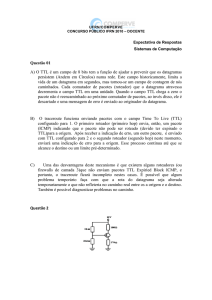

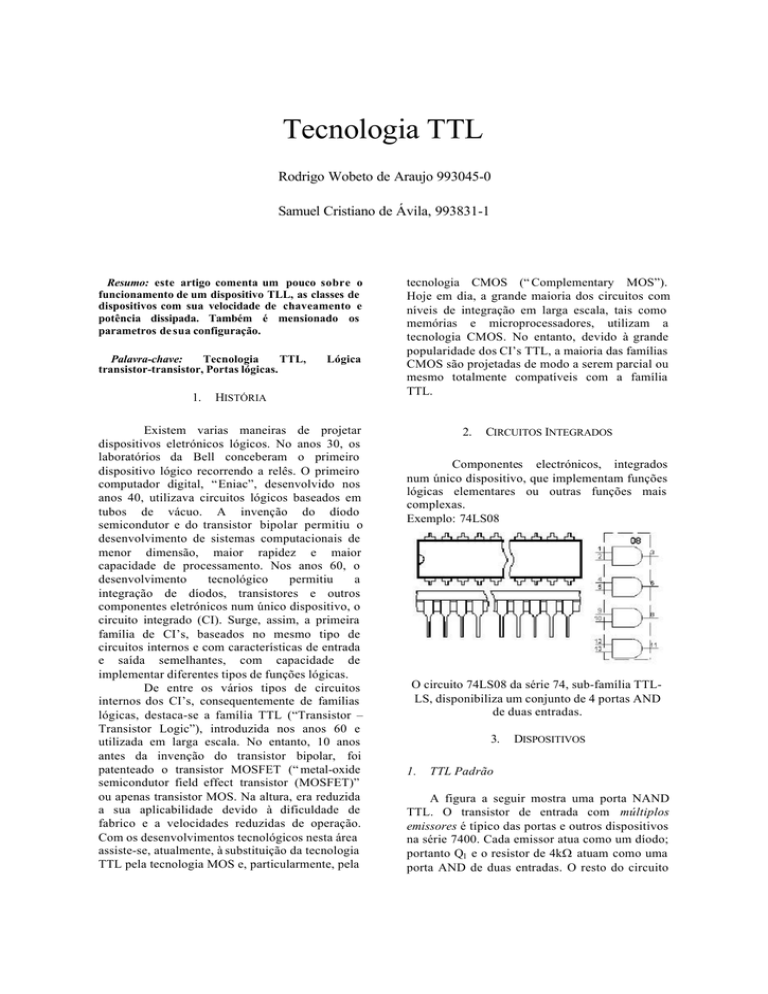

Componentes electrónicos, integrados

num único dispositivo, que implementam funções

lógicas elementares ou outras funções mais

complexas.

Exemplo: 74LS08

O circuito 74LS08 da série 74, sub-família TTLLS, disponibiliza um conjunto de 4 portas AND

de duas entradas.

3.

1.

DISPOSITIVOS

TTL Padrão

A figura a seguir mostra uma porta NAND

TTL. O transistor de entrada com múltiplos

emissores é típico das portas e outros dispositivos

na série 7400. Cada emissor atua como um díodo;

portanto Q1 e o resistor de 4kΩ atuam como uma

porta AND de duas entradas. O resto do circuito

inverte o sinal de forma que o circuito total atua

como uma porta NAND de duas entradas. Os

transistores de saída (Q3 e Q4 ) formam uma

conexão poste totem (um npn em série com um

outro); este tipo de estágio de saída é típico na

maioria dos dispositivos TTL. Com um estágio de

saída poste de totem, ou o transistor superior ou o

inferior está conduzindo. Quando Q3 está

conduzindo, a saída é alta; quando Q4 está

conduzindo, a saída é baixa.

As tensões de entrada A e B são ou baixa

(idealmente aterradas) ou altas (idealmente +5V).

se A ou B é baixa, a base Q1 é abaixada para

aproximadamente 0,7V. isto reduz a tensão de

base de Q2 para quase zero. Em conseqüência, Q2

entra em corte. Com Q2 aberto, Q4 entra em corte,

e a base e Q3 é elevada. Como Q3 atua como um

seguidor de emissor, a saída Y é elevada para uma

tensão alta.

Por outro lado, quando A e B são ambas

tensões altas, os díodos de emissor de Q1 param

de conduzir e o díodo coletor passa a conduzir

diretamente. Isto força a base de Q2 a ficar alta.

Por sua vez, Q4 entra em saturação, produzindo

uma saída baixa.

São usados transistores em poste de totem

porque eles produzem uma impedância de saída

baixa. Ou Q3 funciona como um seguidor de

emissor (saída alta) ou Q4 é saturado (saída baixa

). Quando Q3 está conduzindo, a impedância de

saída é aproximadamente 70Ω; quando Q4 está

saturado, a impedância de saída é somente 12Ω

(isto pode ser calculado a partir de informação na

folha de dados). De qualquer forma, a impedância

de saída é muito baixa. Isto significa que a tensão

de saída pode mudar rapidamente de um estado

para outro porque qualquer capacitância parasita

de saída é rapidamente carregada ou descarregada

por meio da baixa impedância de saída.

Uma porta TTL padrão tem uma dissipação

de potência de cerca de 10mW e o tempo de

atraso de propagação é o tempo que a saída de

uma porta leva par mudar após as entradas terem

mudado. O tempo de atraso de propagação de uma

porta TTL padrão é aproximadamente 10ns.

Esta série é numerada de acordo com a

seguinte tabela:

Número do

Descrição

dispositivo

7400

Quatro portas NAND de duas

entradas

7402

Quatro portas NOR de duas entradas

7404

Seis inversores

7408

Quatros portas AND de duas

entradas

7410

Três portas NAND de duas entradas

7411

Três portas AND de três entradas

7420

Duas portas NAND de quatro

entradas

7421

Duas portas AND de quatro entradas

7425

Duas portas NOR de quatro entradas

7427

Três portas NOR de três entradas

7430

Porta NAND de oito entradas

7486

Quatro portas OR-exclusivo de duas

entradas

Qualquer dispositivo da série 7400

funciona em uma faixa de temperatura de 0 a

70°C e em uma faixa de alimentação de 4,75 a

5,5V. Isto é adequado para aplicações comerciais.

A série 5400, desenvolvida para

aplicações militares, tem as mesmas funções

lógicas que a série 7400, com exceção que ela

trabalha em uma faixa de temperatura de –55 a

125°C e em uma faixa de alimentação de 4,5 a

5,5V. Embora os dispositivo da série 5400 possam

substituir os dispositivos da série 7400, eles

raramente são usados comercialmente em virtude

de seu custo mais elevado.

2.

TTL de Baixa Potência

Aumentando as resistência internas, um

fabricante pode reduzir a dissipação de potência

das portas TTL. Dispositivos desse tipo são

chamados TTL de baixa potência e numerados

74L00, 74L01, etc. Esses dispositivos são mais

lentos que os TTL padrão em virtude das

constantes de tempo internas maiores. Uma porta

TTL de baixa potência tem uma dissipação de

potência de 1mW e um tempo de atraso de

propagação de cerca de 35ns.

4.

3.

Diminuindo

as

resistências,

um

fabricante pode abaixar as constantes de tempo

internas, o que diminui o tempo de atraso de

propagação. As resistências menores, entretanto,

aumentam a dissipação de potência. Essa variação

de projeto é conhecida como TTL de alta

velocidade. Dispositivos desse tipo são numerados

74H00, 74H01, etc. Uma porta TTL de alta

velocidade tem uma dissipação de potência de

cerca de 22mW e um tempo de atraso de

propagação de aproximadamente 6ns.

4.

TTL Schottky

Com TTL padrão, TTL de alta

velocidade e TTL de baixa potência, os

transistores entram em saturação forte, fazendo

com que um excesso de portadores seja

armazenado na base. Ao fazer o chaveamento de

um transistor da saturação para o corte, você tem

de esperar que os portadores adicionais fluam para

fora da base. O atraso é conhecido como tempo de

atraso de saturação.

Uma maneira de reduzir o tempo de

saturação é usar o TTL Schottky. A idéia é

fabricar um díodo Schottky em companhia de

cada transistor bipolar de um circuito TTL. Como

o díodo Schottky tem uma tensão direta de

somente 0,25 a 0,4V, ele evita que o transistor

sature completamente. Isto virtualmente elimina o

tempo de atraso de saturação, o que significa uma

velocidade de chaveamento melhor. Esses

dispositivos são numerados 74S00, 74S01, 74S02

e assim por diante.

Os dispositivos TTL Schottky são muito

rápidos, capazes de operar com confiabilidade em

100MHz. O 74S00 tem uma dissipação de

potência de cerca de 20mW por porta e um tempo

de atraso de propagação de aproximadamente 3ns.

5.

PARÂMETROS TTL

TTL de Alta Velocidade

1.

Entradas flutuantes

Quando uma entrada TTL é alta (idealmente

+5V), a corrente de emissor é aproximadamente

zero. Quando uma entrada TTL é flutuante (não

conectada), não é possível nenhuma corrente de

emissor por causa do circuito aberto. Portanto,

uma entrada TTL flutuante é equivalente a uma

entrada alta. Por causa disso, às vezes você vê

entradas não-usadas deixadas desconcertadas;

uma entrada aberta permite que o restante da porta

funcione corretamente.

Existe uma desvantagem de entradas

flutuantes. Quando você deixa uma entrada aberta,

ela atua como uma pequena antena; portanto capta

tensões parasitas de ruído eletromagnético. Em

alguns ambientes, a captação de ruído é grande o

suficiente para causar o funcionamento irregular

dos circuitos lógicos. Por essa razão a maioria dos

projetistas prefere conectar as entradas TTL nãousadas à tensão de alimentação.

5.

Tensões de Entrada

Quando a entrada é 0V (aterrada), ela esta no

estado baixo e é designada por VIL. Com

dispositivos TTL podemos aumentar VIL até 0,8V

e ainda ter uma entrada em nível baixo. Em outras

palavras, a tensão de entrada em estado baixo,

VIL, pode Ter qualquer valor entre 0 e 0,8V.

Entretanto, se a entrada é 5V, é uma entrada

alta e pode ser designada por VIH. Essa tensão

pode diminuir até 2V sem ocorrer alteração no

estado de saída. Em outras palavras, a entrada em

estado alto, VIH, é de 2 a 5V.

TTL Schottky de Baixa Potência

Aumentando as resistências internas bem

como usando díodos Schottky, os fabricantes

chegaram a uma conciliação entre baixa potência

e alta velocidade: Schottky de baixa potência.

Dispositivos desse tipo são numerados

74LS00, 74LS01, etc. Uma porta Schottky de

baixa potência tem uma dissipação de potência de

cerca de 2mW e um tempo de atraso de

propagação de aproximadamente 10ns.

Qualquer entrada entre 0,8 e 2V é

indeterminada, porque não há nenhuma garantia

de que ela produzirá a tensão correta na saída.

3.

Tensões de Saída

Idealmente, o estado de saída baixo é 0V

e o estado de saída alto é 5V. Não podemos

conseguir esses valores ideais por causa das

quedas de tensão internas dos dispositivos TTL.

Com os dispositivos TTL, qualquer

tensão de saída de 0 a 0,5V é considerada uma

saída baixa e designada por VOL . Isto significa que

a saída em estado baixo, VOL , de um dispositivo

TTL, pode Ter qualquer valor entre 0 e 0,4V.

Em virtude das quedas de tensões nos

dispositivos TTL, a tensão de saída em estado alto

tem valores entre 2,7 e 5,0V e é designada por

VOH .

Qualquer valor entre 0,5 e 2,7V é considerado

indeterminado.

Da mesma forma os piores valores altos

são:

VOH.mín=2,7V

saída do acionador

VIH.mím=2V

entrada da carga

Em qualquer caso, a diferença é 0,4V.

Essa diferença é chamada imunidade ao ruído. Ela

representa proteção incluída contra ruído.

Nós precisamos de proteção contra ruído

porque o fio de conexão entre o acionador TTL e

a carga é equivalente a uma pequena antena que

capta sinais de ruídos parasitas. Na maioria dos

ambientes a tensão de ruído induzido é menor que

0,4V, e não obtemos nenhum disparo falso da

carga TTL.

No pior caso, a entrada baixa para a carga

TTL é:

VIL=VOL +Vruído =0,5V+Vruído <0,8V

No pior caso da entrada de estágio alto é:

VIL=VOH -Vruído =2,7-Vruído >2V

7.

4.

Compatibilidade

Os dispositivos TTL são compatíveis porque

as janelas de saída baixa e alta se encaixam dentro

das janelas de entrada baixa e alta. Portanto a

saída de qualquer dispositivo TTL é apropriada

para acionar a entrada de um outro dispositivo

TTL.

5.

Alimentação e Drenagem

Quando uma saída TTL padrão é baixa,

existe

uma

corrente

de

emissor

de

aproximadamente -1,6mA(pior caso). O sinal

negativo indica que a corrente convencional é

para fora do dispositivo.

Entretanto, quando a saída TTL padrão é alta,

existe uma corrente reversa de emissor de

+0,04mA(pior caso). O sinal positivo indica que a

corrente fluí para dentro do dispositivo.

6.

Imunidade ao Ruído

No pior caso existe uma diferença de

0,4V entre as tensões de saída do acionador e as

tensões de entrada necessária para a carga. Por

exemplo, os piores casos de valores baixos são:

VOL.max=0,5V

saída do acionador

VIL.max=0,8V

entrada da carga

Carga-Padrão

Um dispositivo TTL pode fornecer

corrente (saída alta) ou drenar corrente (saída

baixa). As folhas de dados dos dispositivos TTL

padrão indicam que qualquer dispositivo da série

7400 pode drenar até 16mA (IOL.máx=16mA), e

pode fornecer até 0,4mA (IOH.máx=-0,4mA). Como

discutido anteriormente, os piores caso de

corrente de entrada TTL

são

IIL.máx=-1,6mA

e

IIH,máx=0,04mA. Como as

corrente

de

saída

máximas são dez vezes

maiores que as correntes

de entrada, podemos

conectar

até

dez

emissores TTL a qualquer

saída TTL.

No estado baixo,

a tensão é garantidamente

0,4V ou menor. Se você tentar conectar mais de

dez emissores, a tensão de saída pode subir acima

de 0,4V sob condições de pior caso. Se isso

acontecer, a operação em estado baixo não será

mais confiável. Portanto, dez cargas TTL são o

máximo que o fabricante permite para operação

em estado baixo garantido.

No estado alto, uma tensão de saída alta

(pior caso) com o acionador fornecendo 0,4mA

para dez cargas TTL de 0,04mA cada. Para essa

corrente de alimentação, a tensão de saída é

garantida como sendo 2,7V ou maior sob

condições de pior caso. Se tentar conectar mais de

dez carga TTL, você excederá IOH.máx, e a

operação em estado alto tornar-se-á não confiável.

1.

A porta NAND é a espinha dorsal da

série 7400. Todos os dispositivos nessa série são

derivados da porta NAND de duas entradas. Para

produzir portas NAND de mais entradas, o

fabricante usa transistores com mais emissores.

2.

8.

Tempo de propagação

As portas lógicas são dispositivos físicos,

reais, e como tal não reagem a variações de

entrada com velocidade infinita. É necessário um

certo tempo para que uma variação na entrada se

propague para a saída. É, afinal, este tempo finito

que faz com que os computadores não operem a

frequências infinitas. O tempo que uma

determinada porta demora a reagir não é definido

com completo rigor, até porque depende, entre

outros factores, das condições de temperatura. Os

fabricantes dos CI’s definem, por isso, um limite

máximo para esse tempo.

Especificações dos fabricantes:

• TpLH – tempo máximo de propagação

quando a saída transita do nível baixo(L) para

o nível alto(H).

• TpHL – tempo máximo de propagação

quando a saída transita do nível alto(H) para o

nível baixo(L).

• Tp – tempo de propagação igual ao valor

máximo de TpLH e TpHL.

Portas NAND

Portas NOR

Para obter outras funções lógicas, o fabricante

modifica o projeto básico da porta NAND. Aqui

foram adicionados Q5 e Q6 ao projeto básico da

porta NAND. Como Q2 e Q6 estão em paralelo,

obtemos a função OR, a qual é seguida pela

inversão par obter a função NOR.

Quando A e B são ambas baixas, as bases Q1

e Q5 são levadas ao nível baixo; isto leva Q2 e Q6

ao corte. Em seguida, Q3 atua como um seguidor

de emissor, e obtemos uma saída alta.

Se A ou B é alta, Q1 e Q5 estão em corte,

forçando Q2 e ou Q6 a conduzir. Quando isto

acontece, Q4 satura e leva a saída a uma tensão

baixa.

Com mais transistores, um fabricante pode

produzir portas NOR de três e quatro entradas

(nota: uma porta NOR de oito entradas TTL não é

disponível).

3.

Portas AND e OR

Para produzir a função AND, um outro

estágio emissor comum (EC) é inserido no projeto

básico da porta NAND. A inversão adicional

converte a porta NAND em uma porta AND. As

portas AND TTL disponíveis são a 7408 (quatro

de duas entradas), 7411 (três de três entradas) e

7421 (duas de quatro entradas).

Da mesma forma, um outro estágio EC pode

ser inserido na porta NOR.; isto converte a porta

NOR em uma porta OR. A única porta OR TTL

disponível é a 7432 (quatro de duas entradas).

6. IDENTIFICAÇÃO DOS CI’ S

5. VISÃO PANORÂMICA DA TTL

A identificação base do CI’s segue o

formato XX FAM NNN, onde:

• XX representa a série 54 ou 74;

• FAM representa a sub-família;

• NNN representa o número da função lógica

implementada no CI.

Exemplo: O circuito integrado 74LS08, pertence à

série 74, sub-família TTL-LS e implementa a

função lógica 08 ( 4 portas AND de 2 entradas).

Outras

referências

são

normalmente

adicionadas

para

definir,

entre

outras

características, o tipo de invólucro.

A

0

0

1

1

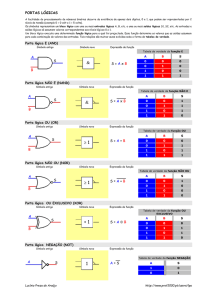

7. FUNÇÕES LÓGICAS ELEMENTARES

1. Função Igualdade:

F(A)=A

Tabela de Verdade:

A

0

1

F

0

1

F ( A) = A

(ou Função NOR): F ( A) =

Tabela de Verdade:

A

B

0

0

0

1

1

0

1

1

A+ B

F

1

0

0

0

11. Função OU EXCLUSIVO

(ou Função EXCLUSIVE OR):

Tabela de Verdade:

A

0

1

F

1

0

7. Função Intersecção

(ou Função Produto Lógico, ou Função E, ou

Função AND): F ( A) = A.B

Tabela de Verdade:

A

B

F

0

0

0

0

1

0

1

0

0

1

1

1

8. Função Reunião

(ou Função Soma Lógica, ou Função OU, ou

Função OR): F ( A) = A + B

Tabela de Verdade:

A

B

F

0

0

0

0

1

1

1

0

1

1

1

1

Função NÃO E

(ou Função NAND):

Tabela de Verdade:

F

1

1

1

0

10. Função NÃO OU

6. Função Negação

(ou Complementação ou Inversão ou NOT):

9.

B

0

1

0

1

F ( A) = A.B

F ( A, B) = A.B + A.B

Tabela de Verdade:

A

0

0

1

1

B

0

1

0

1

F

0

1

1

0

8.BIBLIOGRAFIA

•

ELETRÔNICA DIGITAL, Princípios e

Aplicações Lógica Combinacional

Malvina Leach, ed. McGRAW-HILL

Vol. 1

•

http://www.dmi.ubi.pt/~mario/SL-Capitulo3.pdf

•

http://www.estv.ipv.pt/PaginasPessoais/ffranc

isco/sd/07ci.pdf