SISTEMAS DIGITAIS

2º Semestre de 2000/2001

FOLHAS DE EXERCÍCIOS

FOLHA 5: (Circuitos de lógica combinatória).

1. Desenhe um logigrama simplificado que converta um número de 3 bits representado

em código de Gray para a representação em binário natural utilizando portas lógicas

XOR.

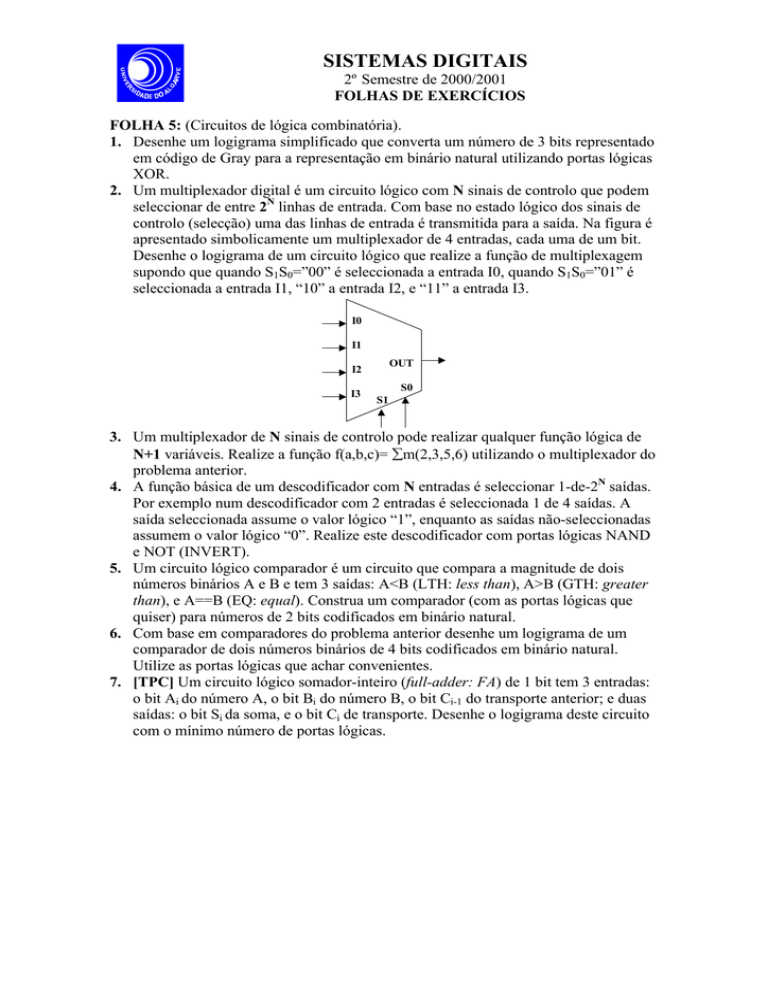

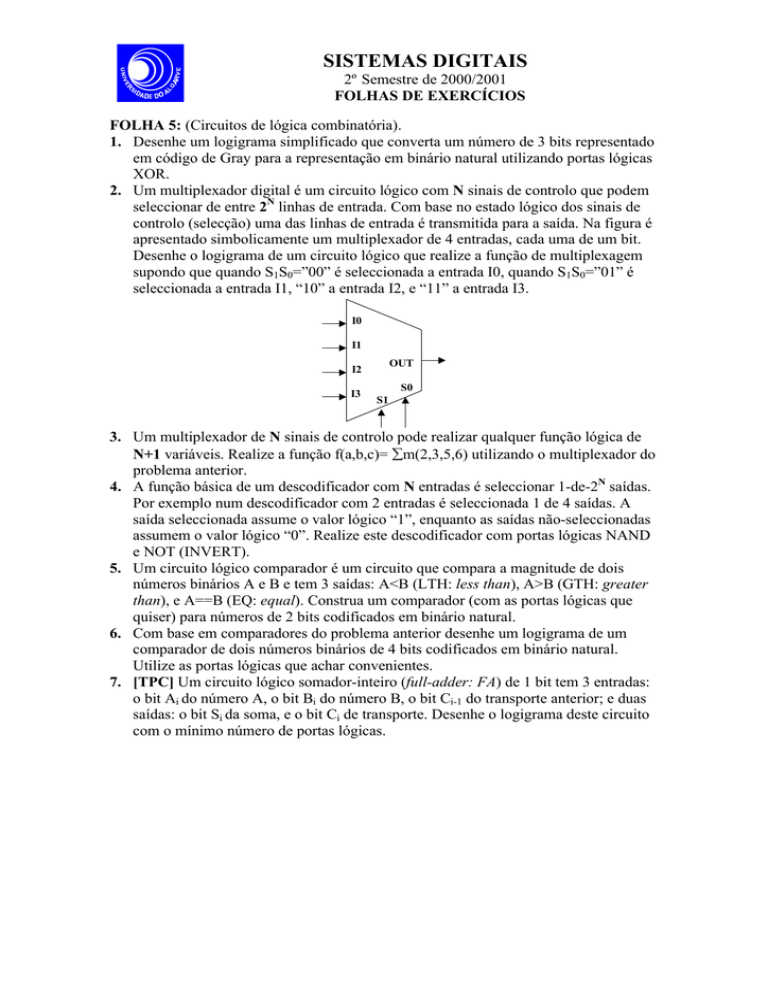

2. Um multiplexador digital é um circuito lógico com N sinais de controlo que podem

seleccionar de entre 2N linhas de entrada. Com base no estado lógico dos sinais de

controlo (selecção) uma das linhas de entrada é transmitida para a saída. Na figura é

apresentado simbolicamente um multiplexador de 4 entradas, cada uma de um bit.

Desenhe o logigrama de um circuito lógico que realize a função de multiplexagem

supondo que quando S1S0=”00” é seleccionada a entrada I0, quando S1S0=”01” é

seleccionada a entrada I1, “10” a entrada I2, e “11” a entrada I3.

I0

I1

OUT

I2

I3

S0

S1

3. Um multiplexador de N sinais de controlo pode realizar qualquer função lógica de

N+1 variáveis. Realize a função f(a,b,c)= ∑m(2,3,5,6) utilizando o multiplexador do

problema anterior.

4. A função básica de um descodificador com N entradas é seleccionar 1-de-2N saídas.

Por exemplo num descodificador com 2 entradas é seleccionada 1 de 4 saídas. A

saída seleccionada assume o valor lógico “1”, enquanto as saídas não-seleccionadas

assumem o valor lógico “0”. Realize este descodificador com portas lógicas NAND

e NOT (INVERT).

5. Um circuito lógico comparador é um circuito que compara a magnitude de dois

números binários A e B e tem 3 saídas: A<B (LTH: less than), A>B (GTH: greater

than), e A==B (EQ: equal). Construa um comparador (com as portas lógicas que

quiser) para números de 2 bits codificados em binário natural.

6. Com base em comparadores do problema anterior desenhe um logigrama de um

comparador de dois números binários de 4 bits codificados em binário natural.

Utilize as portas lógicas que achar convenientes.

7. [TPC] Um circuito lógico somador-inteiro (full-adder: FA) de 1 bit tem 3 entradas:

o bit Ai do número A, o bit Bi do número B, o bit Ci-1 do transporte anterior; e duas

saídas: o bit Si da soma, e o bit Ci de transporte. Desenhe o logigrama deste circuito

com o mínimo número de portas lógicas.

![1. [5] Desenhe um circuito rectificador de onda completa. Dispõe](http://s1.studylibpt.com/store/data/005153713_1-a81ffab7290038346cfda2c943fa496d-300x300.png)

![1. [2,5] Uma fonte de corrente tem uma intensidade nominal de 100](http://s1.studylibpt.com/store/data/004535512_1-c591a15ee860fabf69226bb4d8d623ed-300x300.png)