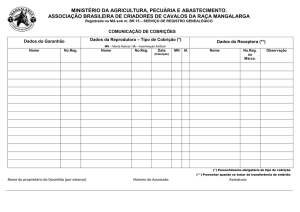

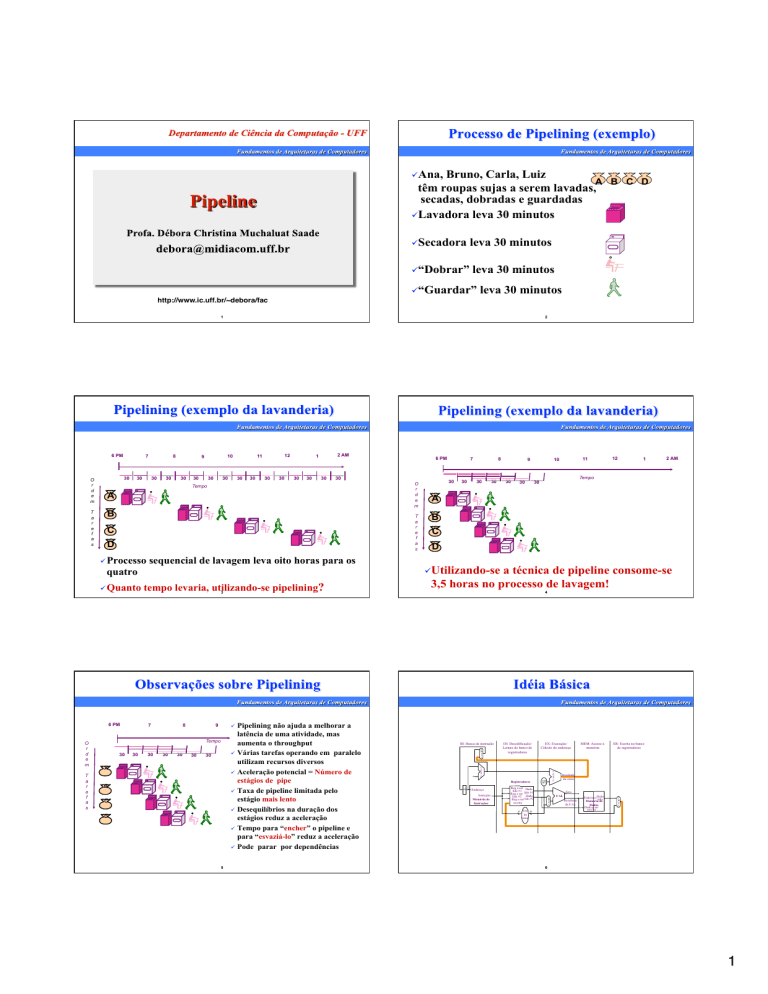

Ana,

Bruno, Carla, Luiz

A B C D

têm roupas sujas a serem lavadas,

secadas, dobradas e guardadas

Lavadora leva 30 minutos

Secadora

“Dobrar”

leva 30 minutos

leva 30 minutos

“Guardar”

leva 30 minutos

http://www.ic.uff.br/~debora/fac!

1

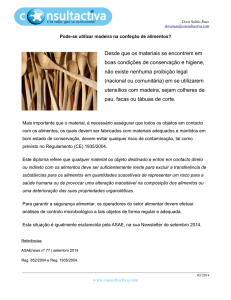

6 PM

O

r

d

e

m

T

a

r

e

f

a

s

8

7

30

30

30

30

30

30

30

12

11

10

9

30

2

30

30

30

30

2 AM

1

30

30

30

30

O

r

d

e

m

Tempo

A

B

T

a

r

e

f

a

s

C

D

Processo

sequencial de lavagem leva oito horas para os

quatro

Quanto

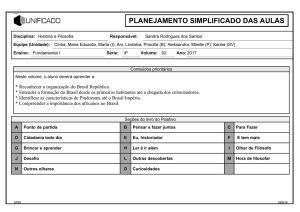

6 PM

O

r

d

e

m

T

a

r

e

f

a

s

6 PM

tempo levaria, utilizando-se pipelining?

7

30

30

30

30

30

30

30

8

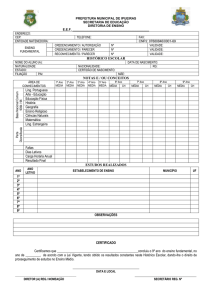

não ajuda a melhorar a

latência de uma atividade, mas

aumenta o throughput

Várias tarefas operando em paralelo

utilizam recursos diversos

Aceleração potencial = Número de

estágios de pipe

Taxa de pipeline limitada pelo

estágio mais lento

Desequilíbrios na duração dos

estágios reduz a aceleração

Tempo para “encher” o pipeline e

para “esvaziá-lo” reduz a aceleração

Pode parar por dependências

30

30

30

12

1

2 AM

Tempo

30

A

B

C

D

Utilizando-se

a técnica de pipeline consome-se

3,5 horas no processo de lavagem!

4

Pipelining

9

30

11

10

9

3

Tempo

30

8

7

30

A

B

C

D

5

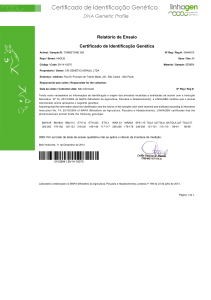

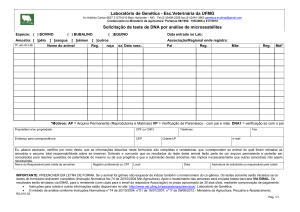

BI: Busca da instrução

0

M

u

x

1

4

DI: Decodificação/

Leitura do banco de

registradores

s

o

m

a

d

o

r

Registradores

PC

EX: Execução/

Cálculo do endereço

Endereço

Instrução

Memória de

Instruções

Reg a ser Dado

lido #1

Reg a ser lido #1

lido #2 Dado

Reg a ser lido #2

escrito

16

Ext.

de

sinal

s

o

m

a

d

o

r

Shift

left 2

MEM: Acesso à

memória

ER: Escrita no banco

de registradores

Resultado

da soma

Zero

0

M

u

x

1

32

UAL

Resultado

da UAL

Endereço Dado

lido

Memória de

Dados

Dado a ser

escrito

1

M

u

x

0

6

1!

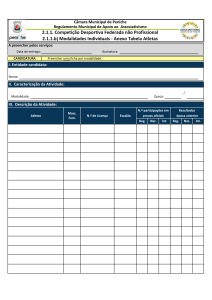

Ciclo 1 Ciclo 2

Load Busca

Ciclo 3 Ciclo 4

Reg/Dec

UAL

Mem

Ciclo 5

Ordem de

execução

do programa

(em instruções)

Reg

2

Tempo

Busca

lw 0 1 100

4

Reg

UAL

lw 0 2 200

Busca:

Busca da instrução da memória de

instruções

Reg/Dec: Leitura do(s) registrador(es) e

decodificação da Instrução

UAL: Calcula o endereço da memória de dados

Mem: Lê dado da memória de dados

Reg: Escreve o dado no banco de registradores

6

8

Busca

8 ns

lw 0 2 200

2

Busca

2 ns

4

Reg

Busca

2 ns

lw 0 3 3 00

6

Reg

Acesso ao

Reg

dado

UAL

Busca

8

10

...

14

12

Acesso ao

Reg

dado

UAL

UAL

Reg

Reg

Busca

2 ns

2 ns

Acesso ao

Reg

dado

UAL

Acesso ao

Reg

dado

2 ns

2 ns

2 ns

que vão ser executadas 100 instruções

monociclo

• 1 ciclo de relógio tem duração de 45 ns

Waste

• 45 ns/ciclo × 1 CPI x 100 inst = 4500 ns

Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6 Ciclo 7 Ciclo 8 Ciclo 9 Ciclo 10

Máquina

Clk

Implementação Pipeline:

ideal pipelined

• 1 ciclo de relógio tem duração de 10 ns

Exec

Mem

Escr

Reg

Exec

Mem

Escr

Exec

Mem

Reg

18

8 ns

Máquina

Store

Tipo R Busca

16

8 ns

Ordem de

execução

Tempo

do programa

(em instruções)

lw 0 1 100

Suponha

Ciclo2

Load

Reg

14

8

Ciclo 1

Clk

Implementação Monociclo:

Store Busca

12

lw 0 3 3 00

7

Load Busca

10

Acesso ao

Reg

dado

• cada estágio de pipeline utiliza um ciclo de relógio

• 5 × 1 ciclo + (1 ciclo × (100 inst -1)) = 50 ns + 99 ×

Escr

10 ns = 1040 ns

9

10

Tempo (ciclos de clock)

Tempo (em ciclos de clock)

Re g

MI

CC 3

ALU

Reg

MI

CC 4

CC 5

MD

Re g

ALU

Reg

ALU

CC 7

Re g

MD

Reg

I

n

s

t

r.

r

Inst 0

Inst 1

Inst 2

Inst 3

Mi

Reg

Mi

Reg

Mi

Md

Reg

Md

Reg

Md

Mi

Reg

Mi

Reg

Inst 4

Reg

Reg

Md

ALU

11

MD

CC 6

ALU

lw $3, 300($0)

CC 2

ALU

lw $2, 200($0)

CC 1

MI

ALU

lw $1, 100($0)

ALU

Ordem de

execução

do programa

(em instruções)

O

r

d

e

m

Reg

Md

Reg

12

2!

Tempo (ciclos de clock)

Conflitos

Md

Mi

Reg

Md

Mi

Reg

Md

Reg

Md

Reg

ALU

I

n

s

t

r.

Instr 1

Reg

ALU

que dobra ocupada com outra atividade

(lavando panela)

• sem duas memórias, não poderia ter acesso à

instrução simultâneo com dados

Mi

ALU

• Ex.: lavadora/secadora combinadas, ou pessoa

Load

ALU

O

r

d

e

m

ALU

estruturais: tentativa de utilizar o

mesmo recurso de modos diferentes ao mesmo

tempo

Instr 2

Mi

Instr 3

Reg

Mi

Instr 4

Reg

Reg

Reg

Md

Reg

Detecção fácil nesse caso!

13

14

Parada:

Conflitos

de controle: tentativa de tomar uma

decisão antes que a condição seja avaliada

O

r

d

e

m

Add

Beq

Mi

Reg

Md

Reg

de dados: tentativa de utilizar um

item antes de estar pronto

Tempo (ciclos de clock)

Reg

Md

Mi

Reg

Md

Mi

Reg

ALU

Mi

ALU

Certo

Reg

Conflitos

ALU

I

n

s

t

r

Reg

Md

escolhe uma direção e retorna se

• predição não executada

Add

Beq

Load

Reg

16

errada

O

r

d

e

m

Md

Mi

Load

15

Predição:

Reg

ALU

I

n

s

t

r

Tempo (ciclos de clock)

Mi

ALU

precisa saber quantidade de sabão; precisa

esperar a secadora para colocar próximo

uniforme

• instruções de desvio

ALU

• Ex.: lavar uniformes de time de futebol e

espera até decisão estar clara

• Ex.: uma meia na secadora e outra na

Reg

Reg

Md

Reg

lavadora; não pode dobrar

• instrução depende de resultado da instrução

anterior, ainda no pipeline

- 50% do tempo

17

18

3!

Tempo (ciclos de clock)

BI

ID/RF

addi r1 r4 100

add r2 r3 r1

Mi

addi r1 r4 100

EX

MEM

Reg

Md

Mi

Reg

ALU

O

r

d

e

m

ALU

add r2 r3 r1

REG

Reg

Md

Reg

I

n

s

t

r

19

20

• “Adiantamento” (forwarding) do resultado de um estágio

para outro

add r2 r3 r1

Mi

addi r1 r4 100

EX

MEM

Reg

Md

Mi

Reg

ALU

O

r

d

e

m

ALU

Tempo (ciclos de clock)

ID/RF

BI

ER

Reg

Md

Reg

I

n

s

t

r

21

4!