UNIVERSIDADE FEDERAL DE SANTA CATARINA

PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Conversores Multiníveis em Corrente

Tese submetida à Universidade Federal de Santa Catarina

para a obtenção do Grau de Doutor em Engenharia Elétrica

Henrique Antônio Carvalho Braga

Florianópolis, 1996

ii

Conversores Multiníveis em Corrente

Henrique Antônio Carvalho Braga

Esta Tese foi julgada adequada para obtenção do título de Doutor em Engenharia,

especialidade Engenharia Elétrica, área de Sistemas de Energia, e aprovada em sua forma

final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de

Santa Catarina.

Florianópolis, 18 de Dezembro de 1996.

Prof. Ivo Barbi, Dr. Ing.

Orientador

Prof. Adroaldo Raizer, Dr.

Coordenador do Curso de Pós-Graduação em Engenharia Elétrica

BANCA EXAMINADORA:

Prof. Ivo Barbi, Dr. Ing.

Prof. Arnaldo José Perin, Dr. Ing.

Prof. Enio Valmor Kassick, Dr.,

Prof. Fernando Luiz Marcelo Antunes, Ph.D.

Prof. Gilberto Costa Drumond de Sousa, Ph.D.

iii

Para Fernanda, Lucas e Mateus,

que pacientemente torceraram, sofreram

e aguardaram por este momento.

iv

AGRADECIMENTOS

A Deus, Primeiro Cientista, que convida o homem a participar da imensa obra de

criação e descobrimento do universo.

A meus pais, Luiz e Aracy, pela paciência e dedicação, e por terem me proporcionado

as melhores opções de ensino, dentro de suas possibilidades.

Ao Professor Ivo Barbi, pelo profissionalismo, determinação, amizade e solicitude

durante todas as etapas deste trabalho.

Aos professores e profissionais do Instituto de Eletrônica de Potência da Universidade

Federal de Santa Catarina - INEP/UFSC, pela colaboração em diversos momentos.

Ao amigo, colega e atual professor do INEP, Alexandre Ferrari de Souza, pelas

valiosas colaborações e discussões técnicas, que me propiciaram evoluir em meus

conhecimentos.

Aos colegas e amigos, Carlos Alberto Canesin (professor da UNESP/Ilha Solteira),

Carlos Augusto Ayres (professor da EFEI/MG) e Ewaldo Luiz de Mattos Mehl (professor da

UFPR) pelas colaborações em várias ocasiões.

Aos Bolsistas de Iniciação Científica Juliano Anderson Pacheco, Luiz Cláudio Souza

dos Santos e Frank Weiner Heerdt, pelas contribuições em determinadas etapas deste

trabalho.

Aos amigos de Florianópolis, que com seu carinho, ajudaram a mim e minha família a

superar a saudade e distância do lar.

Ao sofrido Povo Brasileiro, muitas vezes sem o mínimo direito de acesso à Escola,

que com seu suor e impostos me permitiram atingir este estágio de educação.

v

BIOGRAFIA DO AUTOR

HENRIQUE ANTÔNIO CARVALHO BRAGA nasceu em Aimorés, MG, em 01 de

agosto de 1959. Estudou até a quarta série do Primeiro Grau no Grupo Escolar Machado de

Assis, em sua cidade natal. Da quinta à oitava série do Primeiro Grau freqüentou o Instituto

Educaional Carmo, também em Aimorés, MG. O primeiro ano do Segundo Grau foi cursado

no Colégio Tiradentes da Polícia Militar, em Manhuaçu, MG. Em 1976 mudou-se para Juiz

de Fora, onde cursou os dois últimos anos do Segundo Grau e preparou-se para o Exame PréVestibular pelo Sistema CAVE de ensino. Prestou Vestibular em 1978 e foi aprovado na

Pontifícia Universidade Católica - PUC- de Belo Horizonte e na Universidade Federal de Juiz

de Fora - UJFJ, onde classificou-se em quinto lugar e efetivamente concluiu o curso de

Engenharia Elétrica, em 1982. Em 1983 ingressou no Curso de Mestrado em Engenharia

Elétrica da Coordenação dos Programas de Pós-Graduação em Engenharia da Universidade

Federal do Rio de Janeiro - COPPE/UFRJ. Orientado pelo Professor Edson Hirokazu

Watanabe, obteve o grau de Mestre em Ciências, em abril de 1988, na área de Eletrônica de

Potência. Em 1985 classificou-se em primeiro lugar, em concurso público, para provimento

de vaga de Professor de Eletrônica no Departamento de Circuitos Elétricos da Faculdade de

Engenharia da UFJF. Ingressou no quadro docente da UFJF em março de 1986, onde se

mantém ligado profissionalmente até a presente data. Na UFJF foi Coordenador do

Laboratório de Microcomputação - LABMICRO, Tesoureiro da Associação dos Professores

de Ensino Superior - APES e Chefe do Departamento de Circuitos Elétricos. Também foi

fundador e primeiro Conselheiro do Ramo Estudantil do Instituto dos Engenheiros Elétricos e

Eletrônicos - IEEE na UFJF. É membro da Sociedade Brasileira de Automática - SBA, da

Sociedade Brasileira de Eletrônica de Potência - SOBRAEP e do IEEE.

vi

Sumário

Página

Simbologia e Abreviaturas ___________________________________________________ ix

Resumo___________________________________________________________________ xi

Abstract _________________________________________________________________ xii

1. Introdução ______________________________________________________________ 1

1.1. Associação Série de Chaves Semicondutoras _____________________________________ 4

1.2. Associação Paralela de Chaves Semicondutoras __________________________________ 4

1.3. Associação de Conversores Estáticos ___________________________________________ 7

1.3.1. Associação Série de Conversores Estáticos ____________________________________________ 8

1.3.2. Associação Paralela de Conversores Estáticos ________________________________________ 13

1.3.3. Conversão Estática Distribuída ____________________________________________________ 16

1.4. Associação de Células de Comutação __________________________________________ 18

1.5. Objetivos e Metodologia _____________________________________________________ 23

2. A Célula Multinível em Corrente ___________________________________________ 26

2.1. Conceitos Fundamentais ____________________________________________________ 26

2.2. Aplicação ao Conversor Buck-2 células ________________________________________ 34

2.3. Aplicação aos Conversores CC-CC ____________________________________________ 40

2.4. Aplicação aos Inversores de Tensão ___________________________________________ 41

2.5. Aplicação aos Inversores de Corrente__________________________________________ 42

2.6. Aplicação aos Retificadores __________________________________________________ 44

2.7. Conclusões ________________________________________________________________ 45

3. Modelo Matemático dos Conversores MNC ___________________________________ 46

3.1. Modelo da chave PWM _____________________________________________________ 46

3.2. Modelo Entrada-Saída do Conversor Buck - 2 células ____________________________ 49

3.3. Modelo Entrada-Saída do Conversor Buck - 3 células ____________________________ 55

3.4. Modelo Entrada-Saída do Conversor Boost - 2 células ____________________________ 60

vii

3.5. Modelo Controle-Saída do Conversor Buck - 2 células____________________________ 62

3.6. Modelo Controle-saída do Conversor Boost - 2células ____________________________ 64

3.7. Conclusões ________________________________________________________________ 68

4. Nova Técnica de Paralelismo ______________________________________________ 69

4.1. O Paralelismo Convencional _________________________________________________ 69

4.2. Paralelismo de IGBTs_______________________________________________________ 70

4.3. A Célula MNC como Técnica de Paralelismo ___________________________________ 72

4.4. Projeto dos Indutores de Equilíbrio ___________________________________________ 77

4.4.1. Paralelismo MNC Aplicado aos Conversores CC-CC___________________________________ 80

4.4.2. Paralelismo MNC Aplicado aos Inversores de Tensão e Retificadores de Corrente ___________ 87

4.4.3. Paralelismo MNC de Inversores de Corrente e Retificadores de Tensão ____________________ 95

4.5. Técnicas Alternativas de Paralelismo de Células de Comutação ____________________ 98

4.6. Considerações Sobre a Dinâmica do Equilíbrio de Correntes _____________________ 107

4.7. Conclusões _______________________________________________________________ 109

5. Conversores CC-CC Multiníveis em Corrente ________________________________ 110

5.1. Conteúdo Harmônico e Interferência Eletromagnética __________________________ 111

5.2. Corrente Multinível nos Conversores CC-CC __________________________________ 114

5.3. Metodologia de Projeto e Limitações Tecnológicas ______________________________ 121

5.4. Compensação do Desequilíbrio de Correntes___________________________________ 125

5.5. Outras Alternativas para Equilíbrio de Correntes ______________________________ 132

5.6. Conclusões _______________________________________________________________ 136

6. Inversores de Corrente e Retificadores de Tensão MNC________________________ 137

6.1. Inversor de Corrente ______________________________________________________ 137

6.2. Inversores de Corrente MNC________________________________________________ 140

6.3. Estratégias de Chaveamento ________________________________________________ 141

6.4. Seqüência Assimétrica de Chaveamento_______________________________________ 144

6.5. Seqüência Simétrica de Chaveamento ________________________________________ 153

6.6. Estratégia Genérica de Chaveamento _________________________________________ 155

viii

6.7. Inversor MNC Polifásico ___________________________________________________ 159

6.8. Resultados Experimentais __________________________________________________ 161

6.9. Retificador de Tensão MNC ________________________________________________ 167

6.10. Conclusões ______________________________________________________________ 172

7.Um Pré-Regulador de 3,2 kW com FP Unitário

e Comutação Suave em Tensão____________________________________________ 173

7.1. Definição do Sistema_______________________________________________________ 173

7.2. Comutação Não-Dissipativa_________________________________________________ 179

7.3. Orientações de Projeto _____________________________________________________ 186

7.4. Resultados Experimentais __________________________________________________ 201

7.5. Conclusões _______________________________________________________________ 206

8.Conversores Multiníveis em Tensão e Corrente _______________________________ 207

8.1. Proposta de uma Topologia Genérica _________________________________________ 207

8.2. Conversor Buck -2 Células Multinível em Tensão e Corrente _____________________ 209

8.3. Conclusões _______________________________________________________________ 214

9.Conclusão Geral ________________________________________________________ 215

Referências Bibliográficas _________________________________________________ 223

Apêndice A - Arquivos de Simulação no Pspice® _______________________________ 228

ix

Simbologia e Abreviaturas

SÍMBOLO

SIGNIFICADO

UNIDADE

utilizado para indicar fluxo convencional positivo de correntes

↑

utilizado para polaridade positiva convencional de tensões (ou +/-)

A

terminal ativo da célula de comutação unidirecional em tensão

C

terminal comum da célula de comutação

cf.

confira ou conforme

Co

capacitância do capacitor filtro de tensão

δ

quociente entre as razões cíclicas D2/D1 para conversor MNC-2 células

D

razão cíclica

∆i

variação de corrente nos indutores ou chaves

Dq

razão cíclica da célula q (também usado para denominar diodos)

∆t

atraso no comando das chaves

e.g.

exempli gratia (por exemplo)

µF

s

f

freqüência escalar de uma grandeza alternada (senoidal ou não)

φ

ângulo relativo ao atraso no comando das chaves

fS

freqüência de chaveamento de um conversor estático

Hz

I

corrente de fonte independente cc

A

i

corrente em ramo de um circuito (valor instantâneo)

A

IC

corrente média que sai do nó comum, C, de uma célula de comutação

A

λ

número de níveis de corrente de um conversor MNC

Lo

indutância filtro de corrente

Hz

H

x

SÍMBOLO

SIGNIFICADO

UNIDADE

m

margem de segurança usada no projeto de indutores de equilíbrio

M

índice de modulação

n

número de células de comutação associadas

P

terminal passivo da célula de comutação unidirecional em tensão

q

razão entre a resistência parasita, rL, do indutor de equilíbrio e r

θ

representação do tempo em grandeza angular (é igual a ωt)

r

resistência “média”de condução de uma célula de comutação

ρ

razão entre a resistência série do indutor de filtro (nó C) e r

rL

resistência parasita dos indutores de grampeamento

Ω

Ro

resistência de carga

Ω

rON

resistência de condução de chaves ou diodos (modelo resistivo)

Ω

tempo (em segundos, ms ou µs)

s

t

rad (ou o)

Ω

T1, T2

terminal ativo ou passivo da célula de comutação bidirecional em tensão

THD

taxa de distorção harmônica (“total harmonic distortion”)

%

TS

período de chaveamento (=1/fS)

s

V

tensão de fonte independente cc ou valor eficaz de tensão senoidal

V

v

tensão entre nós de um circuito (valor instantâneo)

V

ω

freqüência angular de um sinal alternado

rad/s

xi

Resumo

Neste trabalho propõe-se uma nova estrutura de associação paralela de células de

comutação que também apresenta múltiplos níveis de corrente nos elementos internos de

equilíbrio. Baseado nesta característica, o conceito de multiníveis em corrente é introduzido

aqui, exigindo uma diferenciação na terminologia convencional empregada até a presente

data.

A célula genérica multinível em corrente (MNC) consiste na associação paralela de

células de comutação por meio de indutores de grampeamento de corrente que garantem, na

condição recomendada de projeto, uma distribuição de corrente equilibrada entre as chaves

semicondutoras da estrutura. A estrutura genérica pode ser empregada como técnica de

paralelismo, situação em que as chaves são disparadas com o mesmo sinal de comando, ou na

geração de multiníveis de corrente no ramo de tensão da célula, aplicação que exige

defasagens e estratégias de comando específicas, em determinados casos.

Como técnica de paralelismo a célula MNC possui a vantagem de empregar um menor

número de elementos de equilíbrio, quando comparada com outras alternativas. A técnica

garante, ainda, um mecanismo de supressão de picos de corrente superando, assim, a técnica

convencional de associação paralela de chaves. Por meio desta característica, acredita-se

obter conversores mais robustos e confiáveis. Praticamente todos os conversores estáticos,

operando em condução contínua de corrente, podem beneficiar-se desta nova técnica.

Enquanto projetada para aproveitamento dos multiníveis de corrente a célula MNC é

capaz de otimizar o conteúdo harmônico do conversor, reduzir interferência eletromagnética

conduzida ou irradiada e, em determinados casos, viabilizar a obtenção de um fator de

potência “quase-unitário”.

No corpo do trabalho foram incluídas análises teóricas, equacionamento matemático,

resultados de simulação e experimentação para, praticamente, todos os casos estudados.

Novas estruturas e técnicas também foram sugeridas aqui, pois enquadram-se também no

tema principal proposto.

xii

Abstract

This work presents a new electric structure for parallel connection of commutation

cells, having its internal elements conducting a number of intermediate current levels. By this

way, the current multilevel concept has been introduced for the very first time, requiring a

different terminology from the one employed nowadays.

The generic current multilevel cell associates any number of single commutation cells

by means of clamping inductors which guarantee, assuming a good design, a balanced

distribution of currents among the semiconductor switches of the structure. The generic

structure can be used to substitute the conventional parallel connection technique, a situation

that implies in the same gate signal for all the active switches, or to generate current

multilevels through the cell voltage branch, an application that requires delayed gate signals

and specific switching strategies, depending on the case.

As a new paralleling technique the new current multilevel cell has the advantage of

employing less balancing elements, as compared to other similar alternatives. The technique

also ensures a current clamping mechanism, which prevents that a single switch conducts

alone all the current of the structure. This situation is a known problem in the conventional

paralleling technique. Thus, the new technique can provide more reliable and robust

paralleled converters. Almost all static converters can take benefit of the new paralleling

technique.

When it is designed to generate current multilevels, the new cell can provide

converters with harmonics optimization (low THD), reduced irradiated and conducted EMI

and also a “quasi-unity” power factor rectifier.

Along this text a number of theoretical analyses have been included as well as

mathematical models, simulation and experimental results for almost all the studied cases.

Some other techniques and structures have been also suggested here, since they are related to

the main goal of the whole work too.

1

Capítulo

U

1.

Introdução

m dos mais importantes enfoques de pesquisa na indústria de componentes

usados em Eletrônica de Potência consiste na busca de dispositivos

semicondutores de potência capazes de conduzir elevadas correntes e

paralelamente suportar grandes valores de tensão quando bloqueados.

Neste sentido foram desenvolvidos novos dispositivos na última década, cada um dos quais

apresentando características máximas de tensão, corrente e freqüência qualificando-os para

diferentes aplicações.

De acordo com a tecnologia empregada na fabricação pode-se classificar os atuais

componentes semicondutores de potência em quatro grandes grupos principais: os tiristores

(SCR, GTO, etc.), os transistores de junção bipolar (BJT), os transistores de efeito de campo

(JFET, MOSFET, etc.) e os transistores híbridos ou transistores bipolares de gatilho isolado

(IGBT). Esta ordem de apresentação é cronológica, ou seja, os tiristores inauguraram a era

dos semicondutores controlados de potência enquanto os IGBTs consistem numa tecnologia

mais recente. Alguns destes componentes ocupam faixas bastante específicas de aplicações e

níveis de potência. Os tiristores, por exemplo, ainda reinam absolutos em aplicações de alta

potência e baixa freqüência (e.g. tração elétrica e transmissão HVDC - alta tensão/corrente

contínua). Já os IGBTs têm sido aplicados em freqüências intermediárias (menor que 50kHz)

em potências cada vez maiores (já superaram 1 MVA em 1996), chegando atualmente a

ameaçar os tiristores de potência mais baixa como os GTOs. Os IGBTs são usados hoje em

aplicações que vão desde fontes chaveadas a acionamento de motores. Os MOSFETs, por

outro lado, têm sido utilizados em médias potências e altas freqüências (50 a 600_kHz),

tipicamente em fontes chaveadas com comutação não dissipativa, periféricos de

computadores, eletrônica automotiva e fontes de potência para aquecimento indutivo [1]. Os

transistores bipolares ocupam, juntamente com os MOSFETs, a menor faixa de potência (até

dezenas de kW), sendo capazes de chavear satisfatoriamente até 20 kHz (mas em operação

linear operam até 30 MHz). Em determinadas aplicações tanto os MOSFETs quanto os

transistores bipolares também têm sido ameaçados por componentes mais modernos, como o

IGBT. Circuitos Integrados de potência (“smart power IC’s”) consistem em um novo capítulo

da Eletrônica de Potência, e têm sido desenvolvidos para atuar até na faixa de médias

potências, devendo substituir componentes discretos e circuitos convencionais de disparo e

2

proteção. Outros componentes recentes incluem o “MOS-controlled thyristor” (tiristor com

tecnologia de gate MOS, ou ainda tiristor de controle MOS) e o “Emitter-switched thyristor”

(ou tiristor chaveado pelo emissor). Eles devem ser utilizados em aplicações que exijam

tensões superiores a 2 kV [1], [2], [3].

A Tabela 1.1 reúne um conjunto de informações a respeito do estado-da-arte dos

componentes básicos mencionados aqui.

TABELA 1.1

- VALORES NOMINAIS MÁXIMOS DOS COMPONENTES (1996) COMPONENTE

TENSÃO, V

CORRENTE, A

FREQÜÊNCIA, kHz

POTÊNCIA, kVA

TIRISTOR

10.000

5.000

2

10.000

TRANSISTOR

1.000

300

20

200

MOSFET

1.000

100

50

50

IGBT

3.000

1.000

20

3.000

Para se atingir os níveis de tensão e corrente de alguns elementos da Tabela 1.1 os

fabricantes recorrem, em geral, a técnicas de produção de circuitos integrados. Para ampliar

os limites de corrente são produzidos módulos que contêm componentes discretos em paralelo

(na prática um paralelismo de “chips”). Estes módulos minimizam problemas de “layout” e

divergência de parâmetros, permitindo uma operação segura com elevados níveis de corrente

apesar de, geralmente, serem de alto custo[4]. Para os IGBTs, por exemplo, o limite de

corrente e potência dos componentes discretos está em torno de 70A e 200kVA.

Os valores desta tabela são aproximados, devendo ser usados apenas como estimativa,

já que a diversidade de fabricantes e tecnologias oferecem um universo muito extenso de

alternativas. Deve-se observar também que nem sempre é possível encontrar um componente

capaz de operar simultaneamente com os valores máximos indicados em uma mesma linha da

tabela. Outros parâmetros como a energia gasta no comando e corte, queda de tensão em

condução, custo, etc., também são fundamentais para a caracterização de um determinado

componente, mas não foram incluídos na tabela. A freqüência de trabalho máxima mostrada

não considera a possibilidade de circuitos de comutação suave, o que certamente ampliaria os

limites descritos. Os valores indicados consideram um limite aceitável de perdas de

chaveamento em operação dissipativa.

3

A Fig. 1.1 mostra as principais aplicações de Eletrônica de Potência, em função da

tensão de bloqueio e corrente de condução exigida dos componentes semicondutores.

1000

FONTES

CHAVEADAS

AUTOMAÇÃO

INDUSTRIAL

100

Corrente de Condução, A

HVDC

TRAÇÃO

ELÉTRICA

ACIONAMENTO

DE MOTORES

10

1

“BALLASTS” DE

ILUMINAÇÃO

ELETRÔNICA

EMBARCADA

(AUTOMOTIVA)

0.1

10

100

1000

Tensão de Bloqueio, V

10 000

Fig. 1.1- Aplicações típicas da Eletrônica de Potência.

Da Tabela 1.1 e Fig. 1.1 fica claro que alguns componentes podem ser utilizados em

diferentes aplicações, enquanto outros estão limitados a faixas específicas de potência. Mas,

os fabricantes de semicondutores mantêm um trabalho contínuo na pesquisa de novos

componentes, especialmente na tentativa de atingir e superar a marca dos kV e kA. Conforme

mencionado anteriormente uma possibilidade é produzir módulos de potência [4], [5]. Outras

técnicas incluem a extensão da junção de bloqueio direto por toda a área do dispositivo e não

somente em parte dele, conforme aplicado no tiristor de controle MOS [6]. Entretanto, os

novos dispositivos são normalmente mais caros, de difícil acesso e pouco conhecidos. Os

engenheiros preferem, então, empregar componentes bem estabelecidos no mercado, de baixo

custo e confiáveis. Assim, se uma determinada aplicação exige valores de tensão ou corrente

superiores aos que o dispositivo escolhido é capaz de lidar recorre-se ao processo de

associação de componentes. Associação série para grandes tensões e paralela para grandes

correntes. Este procedimento exige, em geral, um projeto cuidadoso e preciso para

determinados componentes. Alguns problemas comuns são: dificuldade de sincronismo na

entrada em condução e bloqueio, variações bruscas de tensão ou corrente nos dispositivos,

instabilidade térmica, etc.

4

Para melhorar a confiabilidade da associação série e paralela de alguns tipos de chaves

semicondutoras de potência pode-se recorrer a diversos recursos, alguns bem difundidos na

literatura técnica.

1.1.

Associação Série de Chaves Semicondutoras

A associação série de componentes requer procedimentos mais ou menos comuns para

os diferentes tipos de chaves semicondutoras. O problema aqui consiste em garantir que todos

os componentes da associação estejam submetidos à mesma tensão (dentro de certa

tolerância), tanto sob o ponto de vista estático quanto dinâmico. Do ponto de vista estático

ocorre que os componentes nem sempre possuem o mesmo modelo de estado ON (quedas de

tensão e impedâncias). A situação se agrava para componentes de lotes diferentes e é menos

crítica dentro de um mesmo lote. Sob o ponto de vista dinâmico existe a possibilidade de

apenas um componente ter que suportar toda a tensão do conversor, admitindo que os demais

tenham entrado em condução antes.

Os SCRs (“Silicon Controlled Rectifiers”) podem ser usados como exemplo para

ilustrar a necessidade de uma rede auxiliar, a fim de minimizar os problemas da associação

série simples. A solução mais comumente empregada é mostrada na Fig. 1.2, onde se percebe

a existência de elementos resistivos em paralelo com circuitos “snubbers” convencionais.

Naturalmente a impedância desta rede auxiliar deve ser projetada para não interferir no

chaveamento normal dos componentes.

Rede Auxiliar

de Equilíbrio

Estático e Dinâmico

de Tensão

Fig. 1.2- Associação série de SCRs.

Os demais componentes semicondutores de potência requerem estruturas similares

para garantia da distribuição equilibrada de tensão, estática e dinâmica.

1.2.

Associação Paralela de Chaves Semicondutoras

A Fig. 1.3 mostra o que ocorre em uma associação paralela de um par de dispositivos

quaisquer quando um componente assume toda a corrente durante o início de condução ou

bloqueio do par. Imperfeições de “layout”, indutâncias parasitas de fios e cabos e

5

divergências no comportamento dinâmico dos dispositivos, respondem por problemas na

entrada em condução ou bloqueio de virtualmente todos os componentes semicondutores.

Atrasos no bloqueio podem ocorrer principalmente com transistores, devido ao tempo de

armazenagem (“storage time”), e com IGBTs, devido ao efeito da corrente de cauda [7].

Corrente na Chave 1

Corrente na Chave 2

tempo

(a)

(b)

Fig. 1.3 - Chaveamentos com desequilíbrio de corrente em um par paralelo.

a) Entrada em condução; b) Bloqueio

Para viabilizar a associação paralela de transistores bipolares, BJTs, torna-se

necessária a utilização de resistores de emissor, como mostrado na Fig. 1.4. A ausência desses

elementos pode determinar a condução permanente de apenas uma chave, provocando o

fenômeno conhecido como desequilíbrio térmico (“thermal runaway”). Esta situação acontece

porque a tensão de saturação, VCEsat, do transistor possui coeficiente de temperatura negativo.

Ou seja, quanto mais corrente conduz um componente maior a sua temperatura, o que reduz a

sua tensão de saturação e o expõe o melhor caminho para a corrente. Esta realimentação

determinará, por fim, uma temperatura superior à que o componente pode suportar,

provocando sua destruição.

i1

i2

Q1

Q2

R

R

Fig. 1.4- Associação Paralela de Transistores Bipolares.

6

A associação paralela de SCRs (Silicon Controlled Rectifiers) pode também ser

inviabilizada pelos diferentes tempos de entrada ou saída de condução dos elementos. O

equilíbrio estático é resolvido, em geral, pela conexão série de fusíveis (cuja queda de tensão

é superior à dos tiristores, definindo assim uma distribuição de corrente equilibrada). Sob o

ponto de vista dinâmico, entretanto, costuma-se utilizar indutâncias em série com os

elementos semicondutores, como representado na Fig. 1.5a. Isto tem o efeito de limitar a taxa

de di/dt que poderia ser destrutiva para alguns elementos. Em alguns casos economicamente

justificáveis pode-se utilizar ainda indutâncias acopladas, como mostra a Fig. 1.5b. Deve-se

lembrar também que os SCRs devem ser protegidos contra dv/dt extremos, o que exige um

circuito snubber em paralelo com os componentes semicondutores (não mostrados na figura)

aumentando, assim, a complexidade da estrutura.

(a)

(b)

Fig. 1.5- Associação Paralela de SCRs.

a) Indutâncias em série; b) Indutâncias acopladas

O coeficiente de temperatura positivo da resistência de condução dos MOSFETs

torna-se vantajoso para este tipo de componente semicondutor. Quanto maior a corrente de

um elemento em paralelo, maior sua resistência condução, o que em contrapartida limita o

crescimento da corrente, determinando um melhor equilíbrio estático de corrente. Assim, os

MOSFETs não requerem normalmente resistores ou indutores quando associados em paralelo.

Esta observação se aplica, no entanto, apenas para as condições de regime permanente do

componente. Para condições dinâmicas, diferenças no tempo de chaveamento e diferenças nas

indutâncias externas (cabos e parasitas) podem determinar um severo desequilíbrio refletido

em transitórios de corrente e tensão que afetam a operação do dispositivo. Os estados

dinâmicos são complexos e são função de muitas variáveis. Desta forma os componentes em

paralelo que sofrem as ações transitórias do desequilíbrio de corrente serão continuamente

submetidos a esforços diferentes dos demais. É possível afirmar, portanto, que este regime

poderá definir uma redução de confiabilidade e vida-útil dos circuitos em questão.

Em função dos recentes avanços na fabricação de IGBTs (“insulated gate bipolar

transistors”) diversos trabalhos têm sido publicados sobre as características destes elementos

7

quando associados em paralelo [8], [9], [10]. Os IGBTs mais comuns no mercado são do tipo

epitaxial (“punch-through” ou PT) e possuem coeficiente de temperatura negativo (em relação

à tensão de saturação coletor-emissor), semelhante aos transistores bipolares. Desta forma

estes componentes também podem sofrer o efeito do desequilíbrio térmico, sendo

imprescindível a montagem dos componentes num mesmo dissipador [11]. Para garantir o

equilíbrio dinâmico de corrente em uma associação paralela de IGBTs exige-se um projeto

cuidadoso de “layout”. Deve-se buscar a total simetria dos ramos que envolvem os

componentes, reduzindo ao máximo as indutâncias parasitas de fios e cabos. Em geral, as

soluções propostas pelos fabricantes envolvem módulos e produtos especialmente projetados

para uma perfeita associação paralela, como no caso do encapsulamento ISOTOP®[5]. Na

prática isto representa linha de produção menor e, conseqüentemente, uma solução mais cara.

Uma outra categoria de IGBTs usa tecnologia homogênea (“non-punch-through” ou

NPT) e apresenta coeficiente de temperatura positivo, de forma que o problema do

desequilíbrio térmico é inexistente [5], [9]. Mas, os problemas de layout e diferenças nos

comportamentos dinâmicos dos componentes da associação ainda é um fato que deve ser

levado em consideração no projeto.

Recentemente, alguns grupos de pesquisa têm investido numa alternativa à simples

associação de componentes procurando, mais amplamente, a conexão de múltiplos

conversores. Outra linha de trabalho busca encontrar células básicas de comutação capazes de

serem associadas indefinidamente e que possam ser aplicadas a qualquer tipo de conversor

estático conhecido.

1.3.

Associação de Conversores Estáticos

De maneira similar à que inspira a associação de chaves de potência, uma linha de

pesquisa recente estuda as possibilidades de associação de conversores em série e em

paralelo. A idéia principal por trás desta técnica consiste em repartir a tensão ou corrente total

de um conversor (em geral um inversor) entre um número determinado de conversores

menores. Em determinados casos é possível, ainda, obter níveis intermediários de tensão ou

corrente que viabilizam a síntese de uma forma de onda alternada em degraus, com baixa

distorção harmônica. O principal objetivo deste procedimento consiste na redução de perdas e

melhoria da estabilidade mecânica dos acionamentos de motores ca. Esta técnica deu origem

ao termo multinível, que tem sido largamente utilizado para designar níveis intermediários de

tensão em conversores. Provavelmente a terminologia tenha surgido a partir dos arranjos de

8

transformadores multifases, muito utilizados nos primórdios da Eletrônica de Potência [12].

Importantes contribuições à nomenclatura, equacionamento e teoria generalizada de

conversores multiníveis de tensão são apresentados em [13].

A associação série ou paralela de conversores pode ser realizada para conversores com

entrada em tensão ou corrente. O texto a seguir apresenta alguns casos típicos propostos e

publicados, em sua maioria, na última década. Estes exemplos, e a seqüência com que são

apresentados (apesar de não ser uma seqüência cronológica de proposição científica),

compõem o conjunto básico de apoio bibliográfico que norteou o caminho para motivação

deste estudo. Em determinados casos fica impossível referenciar todas as contribuições em

um assunto específico, bem como encontrar a referência original ou primeira.

1.3.1. Associação Série de Conversores Estáticos

Os conversores cc-cc podem ser associados em série conforme exemplifica a Fig. 1.6

para pares de conversores buck e boost. A idéia poder ser expandida aos demais conversores

(buck-boost, c′uk, sepic e zeta), além de poder ser generalizada para um número qualquer de

unidades. A estrutura duplo-boost foi proposta como uma forma de reduzir o volume final do

conversor operando com correção do fator de potência, tendo sido originalmente denominada

de boost três-níveis [14], [15]. Isto é alcançado pela operação simétrica das chaves (mesma

largura de pulso e defasadas de metade do período) e pela conseqüente divisão da tensão de

saída entre os dois conversores. Assim, pode-se reduzir à metade o valor do indutor de

entrada, enquanto que as perdas de condução e chaveamento podem ser reduzidas (exigindo

menor volume de dissipador). Na prática a divisão de tensão não é tão simples de ser obtida e

alguns trabalhos têm procurado técnicas para alcançar o equilíbrio desejado [16].

V

V/2

V/2

V/2

V/2

(a)

V

(b)

Fig. 1.6 - Associação série dupla de conversores cc-cc.

a) Duplo buck (ou buck três níveis); b) Duplo boost (ou boost três níveis)

A Fig. 1.7 mostra um esquema simplificado da associação de três inversores de tensão

(“voltage source inverter” - VSI) em meia-ponte proposta em [17]. Esta topologia foi sugerida

para permitir a repartição equilibrada da tensão de entrada (750V) através de transistores

9

bipolares com capacidade de bloqueio menor. O inversor é comandado de maneira

convencional. Ou seja, as chaves S1, S3 e S5 recebem o mesmo pulso de disparo que é, por sua

vez, complementar (com devido tempo morto) ao pulso que dispara as chaves restantes. T1, T2

e T3 são transformadores para conexão à carga.

inversor meia-ponte

V

6

V

V

6

6

carga

T1

S1

S2

T1

Rede de

Grampeamento

T2

de Tensão

T3

6

V

6

carga

V

6

T2

V

6

V

6

carga

T3

S3

S4

S5

S6

Fig. 1.7 - Associação série de inversores VSI em meia-ponte.

A estrutura da Fig. 1.7 inclui ainda um circuito especial de grampeamento (não

detalhado na figura) das tensões nos primários dos transformadores, a fim de garantir uma

divisão de tensão segura. Os secundários dos transformadores também são conectados em

série produzindo uma tensão de cerca de 300V de pico. O comando utilizado não permite

operação multinível de tensão. Entretanto, isto poderia ser alcançado por meio de uma

estratégia de comando que incluísse atrasos entre os pulsos de disparo das chaves de mesmo

grupo.

A Fig. 1.8 apresenta um exemplo de associação série de inversores de tensão

monofásicos em ponte completa (ou “H-bridge”)[18].

10

V1 =

V

2

V2 =

V

2

S1

S2

S3

S4

S5

S6

S7

S8

Carga

Fig. 1.8 - Associação série de inversores VSI em ponte completa.

A estrutura da Fig. 1.8 é capaz de impor à carga cinco níveis de tensão: +V, +V/2, 0, V/2 e -V. O circuito emprega oito chaves que, como para o inversor convencional, são

disparadas de forma complementar. Ou seja, se S1 conduz S3 está aberta, se S2 conduz S4 está

aberta, e o mesmo se dá para as chaves do inversor inferior. Isto garante que as chaves estarão

submetidas no máximo a uma tensão igual a V/2, que é metade da tensão total, V. Deve-se

observar, ainda, que para uma aplicação de carga genérica o circuito exige que as chaves

contenham diodos em anti-paralelo (o que é uma característica comum de algumas chaves

modernas, como MOSFETs e IGBTs-PT). Utilizando até 16 combinações de chaveamento

pode-se associar à seqüência de disparo qualquer método de otimização de harmônicos do

tipo PWM (“Pulse Width Modulation”). A Fig. 1.9 mostra uma tensão de saída possível onde

se utilizou larguras idênticas para todos os pulsos. Entretanto, poder-se-ia utilizar também

uma modulação do tipo PWM senoidal. Ou ainda, dependendo da freqüência da saída e do

nível de potência da aplicação, poder-se-ia evitar qualquer modulação. Isto reduziria as perdas

de chaveamento mas iria piorar o conteúdo harmônico na saída. Cumpre notar, porém, que a

técnica multinível exige muito menos das chaves, já que a freqüência de chaveamento de uma

chave individual é inferior à da repetição de pulsos na tensão de saída. Portanto, estratégias de

comando (modulações) mais complexas podem ser utilizadas, ja’ que não determinam

necessariamente numa elevação da freqüência de chaveamento, fator que deve ser evitado em

altas potências.

11

Tensão na Carga

+V

+V

2

0

Tempo

-V

2

-V

Fig. 1.9 - Tensão de saída multinível com controle por largura de pulso.

A topologia da Fig. 1.8 tem, entretanto, a desvantagem de exigir duas fontes de tensão

separadas (isoladas). É verdade que a partir de um sistema alternado poder-se-ia obter estas

duas fontes por meio de transformadores com secundário duplo, e posterior retificação. Mas

isto, sem dúvida, é uma característica bastante onerosa (e volumosa). A aplicação da técnica

da Fig. 1.8 apenas se justifica, portanto, quando uma variedade de potenciais cc é disponível.

Este sistema, bem como as técnicas de controle propostas em [18], pode ser estendido para

um número qualquer de inversores em série (um número indefinido de níveis de tensão) e

também ser adaptado para estruturas trifásicas.

A Fig. 1.10 apresenta uma topologia multinível proposta anteriormente àquela

mostrada na Fig. 1.8 e possui a vantagem de prescindir de múltiplas fontes cc. Entretanto,

como se pode notar, exige uma rede passiva (capacitores em paralelo com resistores) para

viabilizar os níveis intermediários de tensão [13]. No caso ideal, os capacitores assumem uma

tensão fixa igual à tensão de entrada dividida pelo número de chaves, excluindo a de neutro. É

possível conectar à carga qualquer ponto de tensão intermediária, o que viabiliza uma forma

de onda multinível. Nesta estrutura as chaves com mesmo índice operam de forma

complementar (quando a superior conduz a inferior está bloqueada, e vice-versa). Por este

motivo, a tensão nas chaves bloqueadas não é igual para todas elas. Por exemplo, se Sn

conduz, Sn’ estará submetida à tensão total V. Por outro lado, as tensões de bloqueio

diminuem conforme a chave esteja mais próxima do ponto neutro.

Apesar de permitir um total controle da forma de onda de tensão na carga esta

estrutura não obedece à regra da divisão da tensão de entrada entre as chaves (que é uma

característica fundamental da associação série). Consiste, assim, numa variação topológica

dos inversores conhecidos, capaz de gerar uma tensão multinível sem reunir as vantagens da

associação série de conversores. A configuração apresentada é do tipo inversor em meiaponte. Assim como no caso anterior, pode-se realizar ordens de comando associadas a

qualquer tipo de modulação, visando melhorar ainda mais a qualidade (reduzir os

12

harmônicos) da tensão de saída. Aliás, esta preocupação é compartilhada por todos os

inversores multiníveis.

V

2n

Sn

S

V

2n

S

2

1

V

2n

V

V

2n

V

2n

Carga

S0

,

S1

,

S2

V

2n

,

Sn

Fig. 1.10 - Inversor multinível de tensão em meia-ponte.

O inversor em meia-ponte da Fig. 1.10 é capaz de produzir n+1 níveis de tensão

(incluindo o zero) na carga, enquanto o inversor em ponte completa permitiria uma operação

com 2n+1 níveis. Por exemplo, o inversor meia-ponte (ou três-níveis) formado por duas

chaves mais a de neutro pode imprimir à carga os níveis +V/2, 0 e -V/2, enquanto o pontecompleta permite os níveis +V, +V/2, 0, -V/2, -V. Esta configuração é apresentada na

Fig. 1.11, onde se pode observar que o circuito possui duas chaves a menos em comparação

com a estrutura da Fig. 1.8, que é equivalente em termos de níveis de tensão gerados na carga.

Este circuito também é conhecido como três-níveis (devido aos três potenciais de tensão

compostos pela entrada e dois capacitores), apesar de poder impor à carga cinco níveis de

tensão. É claro que esta afirmativa está subordinada ao fato de os capacitores manterem suas

tensões estáveis. Para garantir isto é necessário que a estratégia de comando seja tal que os

capacitores tenham ciclos de carga e descarga idênticos, para um período da tensão alternada

de saída (ou para múltiplos deste).

V

2

V

S1

Carga

So

V

2

S2

,

S1

,

So

,

S2

Fig. 1.11 - Inversor VSI multinível em ponte completa.

V

2

V

2

13

Existe ainda a possibilidade de se associar inversores CSI em série, como proposto em

[19] e mostrado na Fig. 1.12 para três unidades. Entretanto, a estratégia de modulação e

disparo utilizada nesta referência parece não beneficiar as chaves com uma divisão

equilibrada de tensão.

I cc

Fonte de

Corrente cc

Inversor CSI

Fig. 1.12 - Associação série de inversores de corrente.

1.3.2. Associação Paralela de Conversores Estáticos

Conversores cc-cc podem ser associados em paralelo conforme ilustra a Fig. 1.13a

para dois conversores boost. Esta idéia foi proposta originalmente como uma forma de

superar as limitações tecnológicas dos componentes, tendo sido denominada conversão

“interleaved” [20]. Mais recentemente esta técnica tem sido resgatada e aplicada na correção

do fator de potência (PFC) de fontes chaveadas [21], [22]. A conversão “interleaved” referese à interconexão de múltiplos conversores para os quais a freqüência de chaveamento é a

mesma, mas os pulsos de disparo são defasados. Isto permite benefícios análogos aos

alcançados com o conversor cc-cc três níveis da Fig. 1.6. É claro que a técnica pode ser

ampliada para um número qualquer de elementos e seria possível também disparar os

dispositivos com o mesmo sinal de comando. Outros conversores cc-cc poderiam também ser

associados de forma semelhante, como mostra a

Fig. 1.13b para o conversor buck. A

14

generalização desta idéia é um assunto que será tratado mais apropriadamente no Capítulo 4

(cf. também a Fig. 1.18).

I

Lf

D2

I/2

L2

I/2

I/2

L1

I

D1

S

S

1

2

I/2

(a) Boost

(b) Buck

Fig. 1.13 - Conversores cc-cc em paralelo.

A Fig. 1.14 mostra um exemplo monofásico da associação paralela de dois inversores

VSI em ponte completa [23], [24]. Através desta técnica a corrente da carga é igualmente

partilhada pelas chaves ativas. Assim, espera-se que quando a corrente da carga, io, assumir

seu valor máximo as correntes provenientes das chaves, i1 e i2, fluirão com a metade deste

valor, ou seja io/2. A topologia pode ser aplicada a inversores trifásicos e ser generalizada para

um número maior de inversores em paralelo. Entretanto possui duas desvantagens: só permite

um número par de inversores e exige a construção de indutores acoplados, geralmente de

implementação mais complexa.

i

1

i2

V

io

Carga

Fig. 1.14 - Associação paralela de inversores de tensão em ponte completa

Assim como para o circuito da Fig. 1.8 aqui também torna-se importante a definição

de uma estratégia de comando, capaz de minimizar o conteúdo harmônico da saída, seja para

otimizar o acionamento de motores, seja para reduzir a interferência eletromagnética

irradiada. A técnica de paralelismo da Fig. 1.14 pode ser aplicada a uma grande variedade de

conversores em Eletrônica de Potência.

Estendendo a linha de pensamento da associação de conversores, é possível conectar

também inversores de corrente (“current source inverter”, CSI) em paralelo, como mostra a

Fig. 1.15. Esta topologia foi proposta em [25], a fim de aumentar a capacidade de potência

15

dos inversores de corrente e viabilizar a redução do ruído e perdas no acionamento de motores

de indução. Naturalmente o circuito pode ser generalizado para um número qualquer de

conversores [26]. Entretanto, devem ser considerados os problemas pertinentes ao controle do

fluxo de potência simultaneamente com o controle do conteúdo harmônico [27]. Uma

importante contribuição desta técnica consiste na implementação de multiníveis de corrente,

até então só referenciada para inversores de tensão. A geração de sinais de comando para

viabilizar o bom equilíbrio de corrente entre os inversores (e chaves) torna-se um assunto

particular e complexo, sobretudo pelo grande número de dispositivos envolvidos [27].

I/2

I

ia

I/2

Fonte de

Corrente

a

b

c

Motor de

Indução

Inversor 1

Inversor 2

Capacitores

de Filtragem

Fig. 1.15- Associação de dois inversores de corrente em paralelo

A Fig. 1.16 mostra as formas de onda ideais para a corrente de saída na fase a do

circuito da Fig. 1.15 , bem como as contribuições individuais dos inversores, ia1 e ia2, em

função da corrente de entrada Idc. A variável α é a defasagem entre as correntes geradas pelos

dois inversores. Não se utilizou aqui nenhum tipo de modulação adicional o que, certamente,

poderia melhorar ainda mais a qualidade da forma de onda da tensão e corrente na carga.

16

i a1

I

2

i a2

I

2

I

i = i

a

a1

+ i

I

2

a2

π

3

α

α

Fig. 1.16 - Corrente multinível na fase a e suas componentes.

1.3.3. Conversão Estática Distribuída

Pode-se concluir, a partir dos exemplos deste item, que a maior parte dos sistemas de

Eletrônica de Potência é capaz de ser representada por meio da associação de módulos

conversores básicos. Neste sentido, uma nova abordagem na associação de conversores tem

sido considerada, tendo como objeto principal a busca da distribuição equilibrada da potência

total entre um determinado número de conversores “autônomos” [28], [29]. Esta nova técnica

tem sido denominada “conversão distribuída”, ou ainda “sistemas com arquitetura celular”.

Esta segunda denominação será evitada neste texto, já que pode ser mal interpretada com o

tema discutido no próximo item. O assunto tem sido tratado como uma forma de se reduzir o

volume final do sistema por meio da elevação da freqüência nos conversores individuais.

Pode-se dizer que a conversão distribuída permite ainda, em relação ao sistema não

distribuído, um desempenho superior e uma maior confiabilidade. A questão da

confiabilidade está relacionada com a eventual introdução de módulos extras ou redundantes,

que em caso de falha individual reduzem a probabilidade de falha total do sistema [30]. A

Fig. 1.17 mostra um diagrama de blocos simplificado da técnica em questão.

17

Controle de Tensão

Controle de Corrente

Conversor 1

Tensão

de

Entrada

Conversor 2

Carga

Conversor n

Fig. 1.17 - Conversão distribuída.

Conforme mostra a Fig. 1.17 um sistema de conversão estática distribuída é uma

forma de se associar em paralelo vários conversores de baixa potência na tentativa de facilitar

a construção de sistemas de conversão estática de alta potência. Na prática, o equilíbrio

desejado entre os conversores básicos deverá ser alcançado por meio do controle da tensão e

corrente de um conversor individual, baseado em informações sobre o número de conversores

utilizados, bem como dados sobre os demais módulos [31], [32]. Assim, os conversores

individuais não são tão autônomos assim. De fato o termo autonomia tem sido substituído

recentemente por “quase-autonomia”, como pode ser concluído confrontando [33] e [34].

Dentro da concepção dos conversores distribuídos também busca-se uma forma

adequada para conexão das saídas em paralelo. Neste sentido foi desenvolvida a técnica

mostrada na Fig. 1.18 [29], que consiste numa forma de se associar inversores com pólo

ressonante (PRI), que é um tipo de estrutura com perdas de chaveamento nulas [35]. Apesar

de ter sido proposta muito recentemente, esta técnica de paralelismo foi inspirada em uma

referência mais antiga [36].

18

Cr 1

Lr1

Carga

Lr2

Cr 2

V

2

V

2

Lrn

Cr n

Fig. 1.18 - Conexão paralela de inversores com pólo ressonante (PRPI).

1.4.

Associação de Células de Comutação

Uma forma mais básica de se propor conversores com capacidade de

compartilhamento de tensão ou corrente entre estruturas menores é tratá-los a partir de células

de chaveamento. Neste sentido foi proposto o conceito de célula de comutação ou chave

PWM [37]. A célula de comutação é uma estrutura de três terminais que representa toda a

não-linearidade existente em um conversor estático. Seu funcionamento é baseado na

operação complementar de duas chaves eletrônicas conectadas a um ponto comum. Em outras

palavras enquanto uma chave conduz a outra permanece bloqueada, e vice-versa. A Fig. 1.19

mostra duas maneiras de representar uma célula de comutação. Estas são as representações

mais simples. Entretanto, dentro da abordagem celular, seria possível incluir numa célula

básica elementos passivos, ou até mesmo chaves auxiliares.

T1

T

C

1

Sn

C

,

Sn

T2

(a)

T2

(b)

Fig. 1.19 - A célula de comutação ou chave PWM.

a) Representação simplificada, b) Esquema “real”

19

A linha pontilhada da Fig. 1.19b indica que as chaves são complementares, mas

poderia ser omitida usando-se a convenção de chaves de mesmo nome diferenciadas apenas

pelo sinal “ ’ ”, como também foi usado na figura. Entre os terminais T1 e T2 sempre haverá

uma fonte de tensão (ou um laço capacitivo), enquanto que o terminal C, ou comum, estará

sempre conectado a uma fonte de corrente (ou um ramo indutivo). Em termos de dispositivos

eletrônicos, e dependendo da natureza do conversor, a célula de comutação pode ser composta

de chaves controladas (MOSFET, IGBT, GTO, etc.) e chaves passivas (diodos). A Fig. 1.20

mostra os arranjos típicos para alguns conversores comuns em Eletrônica de Potência.

A

Corrente cc

T1

Tensão cc

C

Tensão cc

Corrente cc

C

P

(a) Fonte Chaveada

Sn

Corrente ca

,

Sn

Sn

C

,

Sn

T2

(b) Inversor VSI

T1

T2

Tensão ca

(c) Inversor CSI

Fig. 1.20 - Arranjos para a célula de comutação.

Da Fig. 1.20 percebe-se que, dependendo do tipo de conversor, as tensões e correntes

nos terminais da célula básica de comutação podem ser do tipo unidirecional (corrente

contínua-cc) ou bidirecional (corrente alternada-ca). Para a fonte chaveada, ou conversor cccc, da letra a os terminais T1 e T2 são mais comumente denominados A (de ativo) e P (de

passivo), respectivamente.

Um importante trabalho que se enquadra na concepção de associação de células é o

proposto em 1981 por Nabae, Takakashi e Akagi [38]. A Fig. 1.21a mostra a estrutura

proposta e a Fig. 1.21b apresenta a célula de comutação mínima. Este circuito foi denominado

originalmente inversor com neutro grampeado, ou NPC (“neutral-point clamped”), sendo

capaz de impor à carga 5 níveis de tensão. Assim como para outras estruturas similares este

conversor tem sido referenciado como conversor três-níveis (“three-level inverter”) [18] e

[39]. Curiosamente o trabalho não faz menção ao termo multinível, denominação que só mais

tarde foi definida por Bhagwat e Stefanovic′ [13].

20

Embora a referência [13] tenha resgatado o termo “multinível” e generalizado o

tratamento com inversores VSI, o trabalho de Nabae et alli parece ter sido o primeiro a

discutir os benefícios desta técnica sobre os inversores convencionais (que até então

utilizavam a técnica PWM para controle de harmônicas). 1

T

1

S

V

2

V

V

2

2

S1

V

Carga

V

2

,

S1

V

2

C

io

,

S2

T

2

(a)

(b)

Fig. 1.21 - Inversor VSI - NPC monofásico em ponte completa (três-níveis).

O inversor NPC também pode ser generalizado para n-níveis, conforme discutido em

[40] e esquematizado na Fig. 1.22. Deve-se notar que um inversor NPC considerado trêsníveis possui duas chaves superiores e duas inferiores (para cada braço), que estão submetidas

à metade da tensão total. Para o caso genérico da Fig. 1.22 pode-se dizer que o inversor terá

n+1 níveis de tensão, e suas chaves bloqueadas estarão submetidas a uma tensão igual à

tensão de entrada dividida pelo número de chaves, n, de uma metade do braço (ou seja V/n).

O estudo de conversores estáticos utilizando o conceito da célula de comutação

permite uma abordagem mais simplificada e passível de generalização, seja do ponto de vista

do número de células, seja do ponto de vista do número de fases, seja do ponto de vista do

tipo de conversor. Dentro desta linha os trabalhos de Meynard&Foch constituem importantes

contribuições, sobretudo pelo estudo sistemático e proposição de aplicações [41], [42]. A

Fig. 1.23 mostra a célula genérica multinível proposta nessa referência, aqui representada para

facilidade de comparação com a Fig. 1.22. Entretanto, a mesma topologia já havia sido

publicada por Maruyama&Kumano [43], sendo até protegida anteriormente por uma patente

japonesa [81].

1

O trabalho de Nabae et. alli [38] data de 1981. Entretanto um trabalho mais antigo (1977) parece ter proposto uma outra

topologia multinível, mas que encontra-se protegida por patentes norte-americanas (cf. as referências [3] e [4] de [13]).

Devido às dificuldades óbvias estas referências não puderam ser localizadas.

21

V

n

S

S

V

n

S

V

n

n

n-1

1

V0

V

,

1

,

S

2

S

V

n

S

,

n-1

S

,

n

V

n

Fig. 1.22 - Braço de inversor NPC multinível.

Sobre a estrutura NPC, a célula de Foch&Meynard tem a vantagem de melhor

equilíbrio de tensões [41]. Nesta estrutura n células são associadas por n-1 capacitores de

grampeamento (ou equilíbrio), enquanto que no conversor NPC são necessários n capacitores.

T1

Sn

S2

...

S1

V

(n-1)V

n

2V

V

n

n

C n-1

C1

,

C2

...

i

(ca ou cc)

C

S1

,

S2

,

Sn

T2

Fig. 1.23 - Célula genérica multinível em tensão.

Na estrutura da Fig. 1.23 as chaves com mesmo número são do tipo complementar,

como exposto no início deste item. Uma tal estrutura também possui, em relação a algumas

topologias da seção anterior, a vantagem de poder ser aplicada a conversores cc-cc (isolados

22

ou não). Entretanto, suas aplicações limitam-se a conversores tipo fonte de tensão. Alguns

exemplos típicos são mostrados na Fig. 1.24.

S6

S3

S2

S3

S2

V

2V

3

2V

S1

V

3

S4

S1

S5

V

3

V

3

2V

3

Carga

V

3

Carga

(a) Chopper ou Conversor Buck 4 níveis

(b) Inversor VSI 4 níveis

Fig. 1.24 - Exemplos de aplicação da estrutura genérica da Fig. 1.23.

Apesar de suas vantagens, o trabalho de Meynard e Foch possui algumas restrições

que devem ser observadas, sobretudo na estratégia de comando utilizada. A Fig. 1.25 mostra

os resultados de simulação para o conversor buck três-níveis (duas células) com carga Ro-Lo e

comandos defasados com três estados: uma chave conduz, as duas conduzem e nenhuma

conduz (portanto uma estratégia bastante convencional). Os parâmetros utilizados foram

V=500V; C1=50µF; Lo=1mH; Ro=10Ω; D=60%; ∆t=5µs; TS=50µs (ou fS=20kHz). Onde C1 é

o capacitor de grampeamento; D é a razão cíclica, ∆t é o atraso no comando das duas chaves e

TS é o período de chaveamento (com freqüência fS).

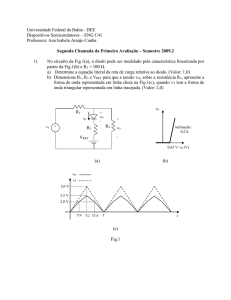

O terceiro traço da Fig. 1.25a mostra como a tensão no capacitor de equilíbrio diverge

do valor previsto mesmo após a estrutura atingir o equilíbrio em regime permanente (como

pode ser constatado dos dois primeiros traços para a tensão e corrente na carga). Este

comportamento termina por provocar o desequilíbrio de tensão nas chaves, conforme

mostram os dois primeiros traços da Fig. 1.25b. O último traço mostra a corrente no capacitor

de equilíbrio e ilustra a desigualdade no processo de carga e descarga de C. O arquivo de

simulação desta estrutura no Pspice® é apresentado no Apêndice A (b2v.cir).

23

(a)

(b)

Fig. 1.25 - Divergência do ponto de operação para o conversor buck-2 células.

(a) De cima para baixo: corrente de saída, tensão de saída e tensão no capacitor de grampeamento

(b) De cima para baixo: Tensão na chave S1, tensão na chave S2 e corrente no capacitor de grampeamento

As estruturas e técnicas apresentadas até aqui representam as principais propostas

publicadas nos últimos anos, envolvendo a associação de componentes, conversores ou

células de comutação. Em alguns casos a concepção multinível se aplica, mas tem sido

predominantemente relacionada a níveis intermediários de tensão. Fica evidente, assim, a

existência de uma “lacuna” tecnológica no que diz respeito a uma abordagem geral sobre os

conversores multiníveis em corrente. Inexiste, ainda, a proposição de uma célula genérica

multinível em corrente capaz de ser adaptada aos principais conversores estáticos.

1.5.

Objetivos e Metodologia

O principal objetivo deste trabalho é propor uma estrutura genérica de divisão e

produção de níveis intermediários de corrente, que possa ser adaptada aos principais

conversores estáticos de Eletrônica de Potência. Pode-se conseguir, assim, uma operação em

níveis de potência mais elevados e, em determinados casos, a redução do conteúdo harmônico

gerado pelo conversor. Fica evidente a possibilidade de utilização de chaves semicondutores

de potência com níveis nominais de corrente bem inferiores ao total envolvido na aplicação e,

24

até mesmo, a viabilidade de operação em níveis de potência acima dos permitidos pelo

“estado-da-arte”.

Como metas complementares serão incluídas a modelagem matemática da estrutura

genérica (bem como de alguns casos particulares), adaptação da estrutura para conversores

conhecidos, proposição de técnicas de projeto e implementação prática, proposta e análise de

estratégias de comando, estudo da viabilidade de comutação não-dissipativa e sugestão de

métodos de controle de equilíbrio de corrente nas chaves semicondutoras, quando for o caso.

Serão abordadas, também, algumas estruturas multiníveis em corrente pouco exploradas

formalmente até então, bem como as comparações básicas com a proposta deste trabalho.

A metodologia a ser empregada envolve a revisão bibliográfica criteriosa dos mais

recentes trabalhos publicados em periódicos e congressos internacionais especializados (o que

em parte foi apresentado neste capítulo), uso de técnicas de modelagem de circuitos

chaveados, emprego de ferramentas computacionais para simulação das estruturas propostas e

realização de estudos experimentais (adaptado a algumas estruturas) que viabilizem a

comprovação dos resultados teóricos.

O Capítulo 2 trata da apresentação básica da estrutura multinível em corrente (MNC)

desenvolvida neste estudo. Nesse capítulo a estrutura é estudada em sua forma básica e uma

prova geral de funcionamento é apresentada, sobretudo fundamentando-se em princípios

físicos e análise de circuitos por inspeção. Também são propostas as principais adaptações

aos conversores estáticos conhecidos.

O Capítulo 3 propõe uma técnica de modelagem matemática geral, baseada no

“modelo da célula de comutação”. Neste capítulo são desenvolvidas as equações gerais para

os conversores buck e boost bem como uma proposta de generalização de modelagem para

conversores com n células. Os modelos entrada-saída e controle-saída são abordados em

detalhes.

O Capítulo 4 discute a aplicação da célula MNC aqui proposta como técnica

alternativa de paralelismo de células de comutação. Neste caso não existe a preocupação

quanto à geração e aproveitamento de níveis intermediários de corrente (multiníveis).

Sugestões para projeto e adaptação do método a todos os conversores estáticos, bem como

outras considerações práticas são apresentadas. Uma comparação com a técnica convencional

de paralelismo, bem como com técnicas e estruturas mais recentes são discutidas em detalhes.

A dinâmica da distribuição de corrente entre chaves também é considerada neste capítulo. São

25

apresentados, ainda, resultados práticos testando a vantagem da técnica para redução de picos

de corrente e resultados experimentais obtidos de um conversor buck-3 células de 4,5 kW.

O Capítulo 5 trata da aplicação da célula MNC aos conversores cc-cc com

aproveitamento dos níveis intermediários de corrente. Assim, os conversores MNC cc-cc são

estudados como uma proposta de minimização de interferência eletromagnética (EMI) e

eliminação de harmônicas específicas. Técnicas de projeto e limitações tecnológicas são

discutidas. Resultados experimentais mostram os efeitos de parâmetros parasitas no

desequilíbrio de corrente entre chaves. Soluções para o controle do desequilíbrio estático em

situações práticas são apresentadas e comparadas.

O Capítulo 6 discute a aplicação da célula MNC aos inversores fonte de corrente

(CSI) e retificadores com filtro de “ondulação” de corrente na saída. As estratégias de

chaveamento e modulação são discutidas, bem como uma proposição de parâmetros para

eliminação de harmônicas e minimização da distorção harmônica total. Um protótipo de um

conversor CSI-2 células (cinco níveis), operando em cerca de 2kW, mostra a viabilidade

prática do sistema bem como suas características e limitações. Também são apresentadas

propostas para obtenção de n níveis de corrente, bem como a possibilidade de operação com p

fases.

No Capítulo 7 apresenta-se a adaptação da célula MNC a um pré-regulador para

telecomunicações baseado em um conversor boost, com fator de potência unitário e

comutação suave em tensão, operando em 3,2 kW. As equações de projeto, técnicas de

implementação e resultados experimentais também são discutidos em detalhes.

O Capítulo 8 discute e propõe uma célula genérica multinível em corrente e tensão

(MNCV). Resultados de simulação, limitações de funcionamento, bem como propostas de

aplicação são apresentados. Sugestões para melhor abordagem e aprofundamento deste

assunto também são indicadas.

O Capítulo 9 apresenta as principais conclusões do presente estudo, seja sob o ponto

de vista particular de cada aplicação, seja com relação ao trabalho como um todo. Sugestões

para continuidade e aprofundamento das questões levantadas são discutidas e ponderadas.

Finalmente são relacionadas as citações bibliográficas e um apêndice envolvendo os

arquivos de simulação no Pspice®.

26

Capítulo

N

2. A Célula Multinível em Corrente

o capítulo anterior foram apresentadas as bases teóricas da célula de

comutação. Mostrou-se ainda, na Fig. 1.23, uma técnica de associação

série de células, envolvendo chaves ativas, passivas e elementos

capacitivos. Apesar de genérica, aquela técnica possui algumas limitações

com relação a determinados conversores estáticos e quanto às técnicas de comando.

Neste capítulo será apresentada uma célula genérica de associação paralela de células

de comutação, bem como seu funcionamento básico e principais aplicações. Parte dos

resultados e discussões aqui apresentados foram publicados em [48] (cf. também [64]).

2.1.

Conceitos Fundamentais

A Fig. 2.1 apresenta uma estrutura para associação paralela de células de comutação

capaz de ser empregada em praticamente todos os conversores estáticos conhecidos, podendo

ser comandada por meio de estratégias que seriam inviáveis para a técnica equivalente de

associação série. Como pode ser visto, as células são conectadas por meio de indutores,

denominados indutores de equilíbrio (ou ainda, indutores de divisão ou grampeamento). Será

mostrado que a corrente de saída do nó C divide-se de forma equilibrada, por entre as células

da associação. Como decorrência desta condição, será visto que os indutores assumem níveis

específicos de corrente que se situam entre o valor da corrente de saída e um valor mínimo.

Além disso, espera-se aproveitar estes níveis intermediários para, em determinados casos,

promover uma melhoria do conteúdo harmônico do conversor. Esta célula será doravante

referenciada como Célula Genérica Multinível em Corrente ou Célula MNC.

T1

i

Sn

...

Sn

Ln-1

V

T2

i n-1

iS3

...

i

S3

S2

i

S2

S1

L2

L1

i2

i1

...

Fig. 2.1- Célula genérica multinível em corrente

S1

C

io

27

O circuito da Fig. 2.2 mostra a adaptação da célula genérica MNC ao conversor cc-cc

do tipo buck (às vezes referenciado como conversor abaixador ou “chopper”). Neste caso a

corrente de saída é unidirecional e as chaves inferiores são chaves semicondutoras passivas de

condução espontânea (ou diodos). As chaves superiores são chaves semicondutoras

controladas que podem ser de qualquer tecnologia, desde que permitam condução e bloqueio

comandado. Como este é um circuito de entrada em tensão, a saída é do tipo corrente, o que

explica a indutância de saída existente. Este elemento pode ser um filtro de corrente adicional

ou pode ser parte da própria carga (como nos motores cc). A carga, por sua vez, pode ser

puramente resistiva ou ainda possuir um capacitor em paralelo. Pode até conter uma força

contra-eletromotriz em série com a resistência e indutância. O circuito dessa figura será usado

para orientar uma primeira análise sobre o funcionamento geral da célula proposta.

A

...

i Sn

i

iS3

Sn

L

S3

n-1

i

S2

L2

S2

S1

L1

S1

...

V

i n-1

i2

i1

C

io

LO

Carga

...

P

Fig. 2.2 - Conversor CC-CC buck MNC

Para reunir as informações básicas sobre o funcionamento da estrutura da Fig. 2.2 é

necessário definir algumas condições-limites. Neste sentido, admite-se inicialmente que:

1. Os indutores de equilíbrio são ideais (indutância pura).

2. Todos os indutores são projetados para operação em condução contínua de

corrente (“continuous conduction mode”- CCM).

3. Todas as chaves superiores possuem o mesmo modelo de condução (resistência

dinâmica, tensão de saturação, etc.).

4. Todas as chaves inferiores possuem o mesmo modelo de condução (resistência

dinâmica, tensão de saturação, etc.).

5. As chaves ativas são comandadas com uma mesma razão cíclica, D, e período

de comutação, T.

De forma a simplificar o estudo por inspeção será considerado ainda que todas as

chaves (ativas e passivas) possuem modelo de operação resistivo, com resistência de

condução r (que tende a zero) e de bloqueio infinita (oo). É suposto, também, que os pulsos de

disparo das chaves ativas são coincidentes no tempo (sem atrasos ou defasagens). Após a

28

análise inicial será apresentada uma discussão sobre as possíveis alterações quando algumas

destas condições não forem satisfeitas.

Considera-se, agora, que as chaves estão operando com razão cíclica máxima (D=1).

Neste caso, as chaves superiores estarão conduzindo em todo o intervalo T, e as chaves

inferiores estarão permanentemente bloqueadas. A Fig. 2.3 mostra o circuito equivalente para

esta situação.

A

...

i Sn

L

r

i

iS3

Sn

S3

L2

r

n-1

i

S1

S2

S1

S2

r

L1

r

...

V

i n-1

C

i1

i2

io

LO

Carga

...

P

Fig. 2.3 - Circuito equivalente para D=1

Como as resistências de condução são muito pequenas, pode-se dizer que o ponto C

assume um potencial de tensão constante igual a V (a tensão de entrada). Nesta situação, a

corrente de saída cresce exponencialmente até atingir seu valor máximo e em regime

permanente será limitada apenas pelos elementos resistivos (e ativos) da carga. Supondo uma

carga passiva com resistência igual a Ro, a corrente io atinge o valor V/Ro, que é fixo e sem

“ondulação” (ou seja corrente cc). Ora, sabe-se que em regime permanente de corrente

contínua os indutores tendem para um curto-circuito. Neste caso o circuito da Fig. 2.4

representa melhor o que acontece após io alcançar o valor de regime, Io. Percebe-se que

existem n elementos resistivos iguais, de valor r, em paralelo. Do nó comum C desta rede sai

(ou entra no nó A) uma corrente cc, sem ripple, de valor Io.

A

...

i Sn

S1

S2

S3

S1

S2

r

r

r

r

i

i

iS3

Sn

I

...

V

i n-1

i2

i1

C

o

V

Ro

...

P

Fig. 2.4 - Regime permanente para D=1

Aplicando a Lei de Kirchhoff das correntes (teorema do divisor de corrente) ao nó C

do circuito da Fig. 2.4 pode-se concluir que:

29

iS 1 = iS 2 = iS 3 =... = iSn =

Io

.

n

(2.1)

Por outro lado, as correntes nos indutores de equilíbrio podem ser determinadas pela

Lei de Kirchhoff aplicada aos nós de chegada:

i1 = I o − iS 1 = I o −

i2 = i1 − iS 2 =

I o (n − 1) I o

=

.

n

n

(n − 1) I o I o (n − 2) I o

− =

.

n

n

n

(2.2)

(2.3)

De forma geral, o q-ésimo indutor, Lq, terá uma corrente:

iq =

(n − q ) I o

.

n

(2.4)

Utilizando esta expressão para o último indutor de equilíbrio, Ln-1, vem:

in −1 =

Io

.

n

(2.5)

Deve ficar claro que as correntes dos indutores de equilíbrio, assim como a corrente de

saída, são correntes contínuas, constantes e sem ripple. Isto é reflexo da situação determinada

pela razão cíclica constante máxima. Conforme será demonstrado a seguir, as relações

descritas pelas equações (2.1) a (2.5) constituem uma figura de mérito para a célula genérica

da Fig. 2.1, sendo válidas desde que as condições (1)-(5) sejam respeitadas. Deve-se observar,

sobretudo, que estas relações não dependem do valor dos indutores, do valor ou existência de

elementos capacitivos na carga e nem do valor de r (já que se admitiu que todas as chaves são

iguais). De fato, se as equações (2.1) a (2.5) foram normalizadas para Io, os níveis

intermediários de corrente só dependerão do número de células associadas, n. Mais

amplamente porém, na presença de chaveamento, estas equações tratariam das relações entre

as correntes médias nos indutores e máximas das chaves (já que no bloqueio suas correntes

são nulas). Fica, assim, configurada a propriedade do uso da terminologia: célula MNC.

Um primeiro passo para comprovação das declarações anteriores seria verificar o que

ocorre quando, após atingir o regime com D=1, os pulsos das chaves são completamente

retirados (D=0). Esta condição é esquematizada na Fig. 2.5.

30

A

...

Ln-1

L2

io

L1

...

V

i n-1

r

r

i2

r

i1

C

LO

r

Carga

...

P

Fig. 2.5 - Ausência de pulsos nas chaves

Neste caso, a distribuição em níveis de corrente nos indutores determinaria que todos

os diodos entrariam em condução, numa ação de roda-livre (ou “free-wheeling”). Ora,

conforme admitido inicialmente, estes elementos se aproximam de um curto-circuito (r →0),

quando em condução. O primeiro efeito, então, seria a descarga progressiva da corrente de

saída em virtude da natureza resistiva da carga. Na ausência de fontes externas que fomentem

os níveis anteriores de corrente, todos os indutores de equilíbrio também se descarregam

gradualmente até zero, apesar de estarem envolvidos em laços quase ideais. Como a corrente

de saída Io também é zero percebe-se que, ainda assim, as equações (2.1) a (2.5) se verificam

em regime! Resta, portanto, investigar o que ocorre na situação normal de operação em que

0 < D < 1.

Uma constatação, aparentemente simples, a respeito da operação das chaves do

circuito da Fig. 2.1 é que as chaves superiores (ou ativas) conduzem sempre que recebem um

pulso de comando. Por outro lado, as chaves inferiores só conduzirão se não estiverem

reversamente polarizadas (quando não há comando para as superiores) e, se e somente se, as

correntes que chegam e saem de seu catodo forem diferentes. A situação de distribuição de

corrente em níveis, verificada na situação anterior, e declarada nas equações (2.1) a (2.5) é,

portanto, um caso que viabiliza a condução dos diodos. Assim, cumpre investigar que

modificações ocorrem quando a razão cíclica é reduzida. Ou seja, o que acontece quando o

conversor está realmente chaveando.

Em primeiro lugar, o indutor de saída deverá acompanhar a mudança no valor médio