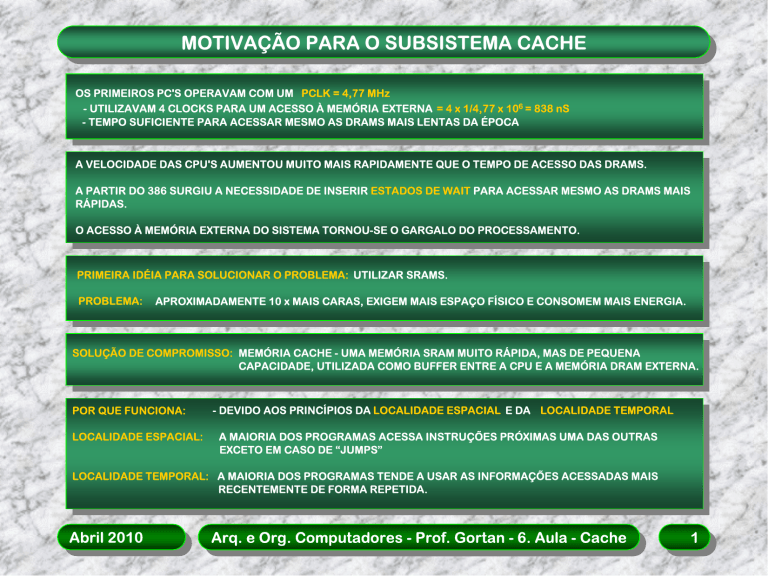

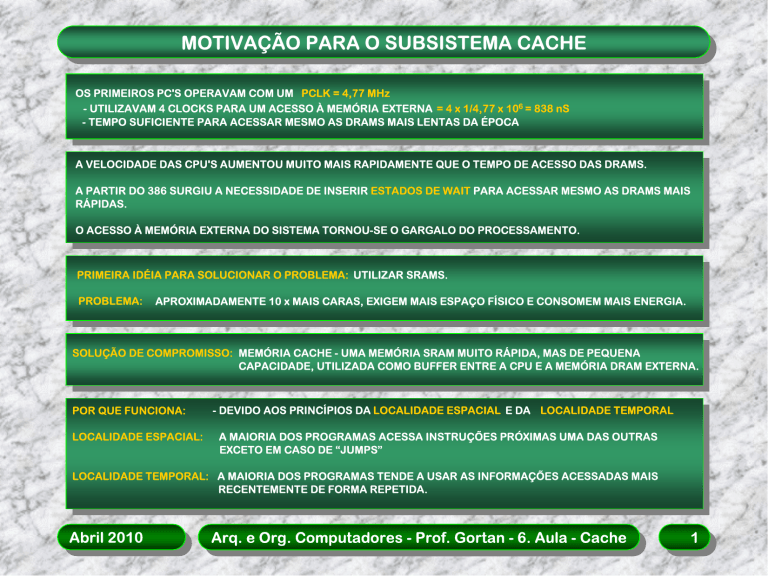

MOTIVAÇÃO

MOTIVAÇÃOPARA

PARAOOSUBSISTEMA

SUBSISTEMACACHE

CACHE

OS PRIMEIROS PC'S OPERAVAM COM UM PCLK = 4,77 MHz

- UTILIZAVAM 4 CLOCKS PARA UM ACESSO À MEMÓRIA EXTERNA = 4 x 1/4,77 x 106 = 838 nS

- TEMPO SUFICIENTE PARA ACESSAR MESMO AS DRAMS MAIS LENTAS DA ÉPOCA

A VELOCIDADE DAS CPU'S AUMENTOU MUITO MAIS RAPIDAMENTE QUE O TEMPO DE ACESSO DAS DRAMS.

A PARTIR DO 386 SURGIU A NECESSIDADE DE INSERIR ESTADOS DE WAIT PARA ACESSAR MESMO AS DRAMS MAIS

RÁPIDAS.

O ACESSO À MEMÓRIA EXTERNA DO SISTEMA TORNOU-SE O GARGALO DO PROCESSAMENTO.

PRIMEIRA IDÉIA PARA SOLUCIONAR O PROBLEMA: UTILIZAR SRAMS.

PROBLEMA:

APROXIMADAMENTE 10 x MAIS CARAS, EXIGEM MAIS ESPAÇO FÍSICO E CONSOMEM MAIS ENERGIA.

SOLUÇÃO DE COMPROMISSO: MEMÓRIA CACHE - UMA MEMÓRIA SRAM MUITO RÁPIDA, MAS DE PEQUENA

CAPACIDADE, UTILIZADA COMO BUFFER ENTRE A CPU E A MEMÓRIA DRAM EXTERNA.

POR QUE FUNCIONA:

LOCALIDADE ESPACIAL:

- DEVIDO AOS PRINCÍPIOS DA LOCALIDADE ESPACIAL E DA LOCALIDADE TEMPORAL

A MAIORIA DOS PROGRAMAS ACESSA INSTRUÇÕES PRÓXIMAS UMA DAS OUTRAS

EXCETO EM CASO DE “JUMPS”

LOCALIDADE TEMPORAL: A MAIORIA DOS PROGRAMAS TENDE A USAR AS INFORMAÇÕES ACESSADAS MAIS

RECENTEMENTE DE FORMA REPETIDA.

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

11

VANTAGENS

VANTAGENSEEPROBLEMAS

PROBLEMASDA

DAUTILIZAÇÃO

UTILIZAÇÃODA

DACACHE

CACHE

O DESEMPENHO DE UM SISTEMA CACHE PODE SER AVALIADO PELA TAXA DE ACERTOS:

"HIT RATE" = (NR. DE ACERTOS / NR TOTAL DE ACESSOS) X 100 %

ACERTO = "CACHE HIT" = DADO REQUISITADO ENCONTRA-SE NA CACHE.

VANTAGEM ADICIONAL DA UTILIZAÇÃO DE UM SISTEMA CACHE:

ALÉM DE ACELERAR O ACESSO AOS DADOS E INSTRUÇÕES DA MEMÓRIA, O SUBSISTEMA CACHE PERMITE

INCREMENTAR O DESEMPENHO GERAL DO SISTEMA POIS LIBERA O BARRAMENTO EXTERNO PARA OUTROS BUS

MASTERS ACESSAREM.

PROBLEMA: CONSISTÊNCIA (OU COERÊNCIA) DA CACHE COM A MEMÓRIA EXTERNA:

EM UM SISTEMA ONDE PODEM COEXISTIR DIVERSOS BUS MASTERS É NECESSÁRIO GARANTIR QUE AS

INFORMAÇÕES CONTIDAS NA CACHE E NA MEMÓRIA EXTERNA SÃO IDÊNTICAS. SE A MEMÓRIA EXTERNA SOFRER

ATUALIZAÇÕES POR ALGUM OUTRO BUS MASTER QUE NÃO A CPU, A CACHE FICARÁ DESATUALIZADA (CACHE

CONTÊM "STALE DATA").

PROBLEMA: CONSISTÊNCIA (OU COERÊNCIA) DA CACHE COM OUTRAS CACHES:

EM SISTEMAS MULTIPROCESSADOS, ONDE MÚLTIPLAS CPU´S, CADA QUAL COM SUA CACHE EMBUTIDA, FAZEM

ACESSO À UMA MEMÓRIA EXTERNA COMUM, É PRECISO GARANTIR A COERÊNCIA TAMBÉM ENTRE AS CACHES.

NO CASO DO PROCESSADOR PENTIUM ISSO É OBTIDO COM O PROTOCOLO MESI.

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

22

PRINCÍPIO

PRINCÍPIOGERAL

GERALDO

DOSUBSISTEMA

SUBSISTEMACACHE

CACHE

MICROPROCESSADOR

MEMÓRIA

DE

DIRETÓRIO

PARTE

BAIXA

DO

ENDEREÇO

LÓGICA

DE

GERENCIAMENTO

HIT

BARRAMENTO DE DADOS

ENDEREÇO

PARTE ALTA DO ENDEREÇO

MEMÓRIA

CACHE

MEMÓRIA EXTERNA - (DRAM)

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

33

ARQUITETURAS

ARQUITETURASBÁSICAS

BÁSICASDE

DEACESSO

ACESSOÀÀCACHE

CACHE

DESVANTAGEM:

MICROPROCESSADOR

MICROPROCESSADOR

"LOOK UP"

PENALTY:

CACHE MISSES

GERAM

ACESSOS MAIS

DEMORADOS

DESVANTAGEM:

ACESSOS À

CACHE NÃO

LIBERAM O

BARRAMENTO

PARA OUTROS

BUS MASTERS

CACHE

CACHE

BUS MASTER 1

BUS MASTER 2

MEMÓRIA

DE

SISTEMA

(DRAM)

BUS MASTER n

ARQUITETURA "LOOK ASIDE"

Abril

Abril2010

2010

BUS MASTER 1

MEMÓRIA

DE

SISTEMA

(DRAM)

BUS MASTER 2

BUS MASTER n

ARQUITETURA "LOOK THROUGH"

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

44

CARACTERÍSTICAS

CARACTERÍSTICASQUE

QUEINFLUEM

INFLUEMNO

NODESEMPENHO

DESEMPENHODA

DACACHE

CACHE

ARQUITETURA DO

BUFFER:

LOOK THROUGH

NÍVEL DA CACHE:

L1, L2, L3 ...

ARQUITETURA DE

DADOS e CÓDIGO:

COMBINADA (UNIFIED)

FILOSOFIA DE ESCRITA

(WRITE POLICY):

Abril

Abril2010

2010

ORGANIZAÇÃO:

LOOK ASIDE

TAMANHO DA LINHA:

TAMANHO DA CACHE:

DEDICADA (SPLIT)

WRITE THROUGH

BUFFERED WRITE THROUGH

WRITE BACK

FILOSOFIA DE

ENDEREÇAMENTO:

COMPLETAMENTE ASSOCIATIVA

MAPEADA DIRETAMENTE

ASSOCIATIVA POR CONJUNTOS

n BYTES POR LINHA

KB DE SRAM DA CACHE

(EXCETUADA A MEMÓRIA DO

DIRETÓRIO)

FÍSICO OU VIRTUAL

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

55

ORGANIZAÇÃO

ORGANIZAÇÃODOS

DOSDADOS

DADOSEEDO

DODIRETÓRIO

DIRETÓRIO

INTERESSANTE PARA CACHES PEQUENAS (4K OU MENOS)

POIS A "LOOK-UP PENALTY" PODE SE TORNAR EXCESSIVA

PARA MAIS POSIÇÕES.

O DIRETÓRIO CONTÉM O ENDEREÇO COMPLETO DO DADO

DADO 6

DADO 5

DADO n

DADO 4

...

...

ENDEREÇO DO DADO n

ENDEREÇO DO DADO 6

DADO 6

ENDEREÇO DO DADO 5

DADO 5

ENDEREÇO DO DADO 4

DADO 4

DADO 3

ENDEREÇO DO DADO 3

DADO 3

DADO 2

ENDEREÇO DO DADO 2

DADO 2

DADO 1

ENDEREÇO DO DADO 1

DADO 1

DIRETÓRIO DA CACHE

MEMÓRIA CACHE

MEMÓRIA EXTERNA

CACHE COMPLETAMENTE ASSOCIATIVA - "FULLY ASSOCIATIVE"

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

66

ORGANIZAÇÃO

ORGANIZAÇÃODOS

DOSDADOS

DADOSEEDO

DODIRETÓRIO

DIRETÓRIO

A "LOOK-UP PENALTY" É MÍNIMA - MAS A CHANCE DA POSIÇÃO JÁ

ESTAR OCUPADA É GRANDE

...

O DIRETÓRIO CONTÉM O NÚMERO DA PÁGINA A QUE O DADO PERTENCE

CADA PÁGINA TEM EXATAMENTE O TAMANHO DA CACHE

CADA DADO SÓ PODE OCUPAR A MESMA POSIÇÃO NA CACHE QUE ELE

OCUPA NA PÁGINA.

PÁGINA 2

DADO 6

NO EXEMPLO, A POSIÇÃO DO DADO 6 (PÁGINA 2) JÁ ESTÁ OCUPADA

PELO DADO 1 (PÁGINA 0).

DADO 5

DADO 4

PÁGINA 1

PÁGINA 1

DADO 4

PÁGINA 0

DADO 3

DADO 3

PÁGINA 0

DADO 2

DADO 2

PÁGINA 0

DADO 1

DADO 1

PÁGINA 2

DADO 5

DIRETÓRIO DA CACHE

MEMÓRIA CACHE

PÁGINA 0

MEMÓRIA EXTERNA

CACHE MAPEADA DIRETAMENTE

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

77

EXEMPLO

EXEMPLODE

DEESTRUTURAÇÃO

ESTRUTURAÇÃODA

DACACHE:

CACHE:--486

486DX2

DX2COM

COM8K

8K

3 BITS

21 BITS 21 BITS 21 BITS 21 BITS

4 BITS

16 BYTES

16 BYTES

16 BYTES

16 BYTES

128 LINHAS x 16 BYTES = 2K

128 LINHAS x 16 BYTES = 2K

...

...

128 LINHAS x 16 BYTES = 2K

...

128 LINHAS x 16 BYTES = 2K

...

...

21 BITS - ÍNDICE DE PÁGINA

21 BITS - ÍNDICE DE PÁGINA

21 BITS - ÍNDICE DE PÁGINA

21 BITS - ÍNDICE DE PÁGINA

...

...

...

...

BITS DE VÁLIDO 1 A 4

...

...

3 BITS LRU POR LINHA

LINHA 127

VIA1

2K

VIA2

2K

VIA3

2K

VIA4

2K

LINHA 1

LINHA 0

LRU

VIA1

VALID

VIA2

VIA3

VIA4

DIRETÓRIO DA CACHE

ENDEREÇO FÍSICO:

MEMÓRIA CACHE

31

11

(21 BITS)

1 DE 2 MEGA PÁGINAS DE 2K

1 DE 2 MEGA PÁGINAS DE 2K

O VALOR É COMPARADO COM O

O VALOR É COMPARADO COM O

VALOR DE CADA UMA DAS 4 VIAS

VALOR DE CADA UMA DAS 4 VIAS

Abril

Abril2010

2010

1 DE 128 LINHAS EM CADA VIA

1 DE 128 LINHAS EM CADA VIA

10

4

(7 BITS)

3

0

(4 BITS)

1 DE 16 BYTES NA LINHA

1 DE 16 BYTES NA LINHA

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

88

INFLUÊNCIA

INFLUÊNCIADO

DOTAMANHO

TAMANHODA

DACACHE

CACHE

CAPACIDADES MAIORES PERMITEM TER UMA TAXA DE ACERTOS (HIT RATE) MAIOR

A RELAÇÃO ENTRE CAPACIDADE E DESEMPENHO ENTRETANTO NÃO É LINEAR

CACHE

EXISTE PORTANTO UM LIMITE PRÁTICO - EM FUNÇÃO DA RELAÇÃO CUSTO-BENEFÍCIO - PARA O TAMANHO DA

EXEMPLO DE CURVA TÍPICA DE DESEMPENHO:

100 %

50 %

1K

Abril

Abril2010

2010

8K

16 K

64 K

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

128 K

99

INFLUÊNCIA

INFLUÊNCIADO

DOTAMANHO

TAMANHODA

DALINHA

LINHADE

DECACHE

CACHE

PARA UM DADO TAMANHO DA MEMÓRIA RAM DA CACHE:

O AUMENTO DO TAMANHO DA LINHA => DIMINUIÇÃO DO TAMANHO DA MEMÓRIA DE DIRETÓRIO

EXEMPLO: CACHE MAPEADA DIRETAMENTE COM 4 KB DE DADOS:

A MEMÓRIA FICARÁ ESTRUTURADA EM 1 M PÁGINAS DE 4 KB CADA ( 1 M x 4 KB = 4 GB).

CADA ENTRADA DE DIRETÓRIO TERÁ PORTANTO 20 BITS PARA ESPECIFICAR 1 DE 1 M PÁGINAS.

ALTERNATIVA A: CADA LINHA DE CACHE COM 4 BYTES:

TOTAL DE LINHAS = 4 KB / 4 BYTES = 1024 LINHAS.

QUANTIDADE DE ENTRADAS DE DIRETÓRIO NECESSÁRIAS = 1024 (UMA PARA CADA LINHA).

TAMANHO DA MEMÓRIA DE DIRETÓRIO = 1024 x 20 BITS / 8 BITS/BYTE = 2560 BYTES

ALTERNATIVA B: CADA LINHA DE CACHE COM 16 BYTES:

TOTAL DE LINHAS = 4 KB / 16 BYTES = 256 LINHAS.

QUANTIDADE DE ENTRADAS DE DIRETÓRIO NECESSÁRIAS = 256 (UMA PARA CADA LINHA).

TAMANHO DA MEMÓRIA DE DIRETÓRIO = 256 x 20 BITS / 8 BITS/BYTE = 640 BYTES

CONTRAPARTIDA:

LINHAS DE CACHE MUITO LONGAS DEMORAM MAIS PARA SER CARREGADAS NA CACHE E COMEÇAM A FUGIR DO

PRINCÍPIO DA LOCALIDADE POIS A PROBABILIDADE DE ENTRAREM DADOS DESNECESSÁRIOS JUNTAMENTE COM

AQUELES REQUISITADOS PELA CPU AUMENTA.

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

10

10

ARQUITETURAS

ARQUITETURASEEBARRAMENTOS

BARRAMENTOS

CLK

66 MHz

Xn

CPU

nCLK

CLK

66 MHz

CACHE L1

CLK FSB 66 MHz

PONTE PCI

RAM

66

100

133

MHz

Xn

PONTE PCI

Cartucho SEC

CPU

BSB

nCLK nCLK

CLK

Xn

133

MHz

CACHE L1

RAM

PENTIUM II / III - XEON

Cartucho SEC

CLK FSB 133 MHz

PONTE PCI

RAM

PENTIUM II / III

CACHE

L2

CLK

Circuito

Integrado

Xn

CPU

BSB CACHE

L3

nCLK

nCLK

L1

L2

Cartucho

CLK FSB

CHIPSET

PONTE PCI

CACHE L1

RAM

CLK FSB 400 MHz

CHIPSET

Xn

BSB CACHE

CPU

nCLK nCLK/2 L2

CHIPSET

PENTIUM PRO

CLK FSB 133 MHz

Abril

Abril2010

2010

66

100

133

MHz

CHIPSET

CACHE

L2

BSB CACHE

CPU

nCLK nCLK

L2

CACHE L1

Circuito

Integrado

CACHE L1

PENTIUM

CLK

CLK

CLK FSB 66 MHz

66 MHz

66 MHz

CHIPSET

Xn

CPU

BSB

CACHE

nCLK nCLK/2

L2

CHIPSET

PONTE PCI

PENTIUM IV

RAM

PONTE PCI

RAM

ITANIUM (IA-64)

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

11

11

EXERCÍCIO

EXERCÍCIO--TLB

TLBDO

DO486

486DX2

DX2

TLB (TRANSLATION LOOKASIDE BUFFER) NO 486 DX2:

IMPLEMENTADO COMO UMA PEQUENA CACHE COM AS SEGUINTES CARACTERÍSTICAS:

- LOOK ASIDE BUFFER

- CACHE ASSOCIATIVA POR CONJUNTOS COM 4 VIAS

- RETÉM AS 32 TRADUÇÕES DE ENDEREÇO MAIS RECENTES (= 20 BITS DO ENDEREÇO FÍSICO CORRESPONDENTE)

DETERMINAR:

O NÚMERO DE TRADUÇÕES ARMAZENÁVEL EM CADA VIA: _________

DOS 20 BITS DO ENDEREÇO LINEAR A TRADUZIR, QUAIS ESPECIFICAM A POSIÇÃO DENTRO DE CADA VIA: ___ A ___

A QUANTIDADE DE BITS EM CADA ENTRADA DAS 4 VIAS DE DIRETÓRIO: ______

( NESTE ÚLTIMO ITEM ADICIONAR 1 BIT PARA ENTRADA VÁLIDA E 3 BITS PARA ATRIBUTOS DE PÁGINA)

A QUANTIDADE DE MEMÓRIA TOTAL EM BYTES PARA IMPLEMENTAR ESSE TLB: ________

DESENHAR UM ESBOÇO DA ESTRUTURA DO TLB DO 486 DX2 DE ACORDO COM OS DADOS ACIMA.

MOSTRAR AS 4 VIAS DE DADOS, AS 4 VIAS DE DIRETÓRIO E COMO AS DIVERSAS PARTES DO ENDEREÇO LINEAR

SÃO UTILIZADAS PARA VERIFICAR SE O CORRESPONDENTE ENDEREÇO FÍSICO SE ENCONTRA NO TLB.

INFORMATIVO: TAXA TÍPICA DE ACERTOS ("HIT RATE") NO TLB DO 486 DX2: 99 %

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

12

12

EXEMPLO

EXEMPLODE

DECHIPSET:

CHIPSET:VIA

VIAKT266A

KT266A

FSB

CPU

CPUATHLON

ATHLONOU

OU

DURON

DURON

200/266 MHz

BARRAMENTO

DE MEMÓRIA

V-LINK

200/266 MHz

SLOTS PCI

VÍDEO

VÍDEO

266 MB/s

BARRAMENTO

PCI

6 X USB

AGP 4X

VT8366A

VT8366A

PONTE

PONTENORTE

NORTE

EEPROM

EEPROM

ATA 33/66/100

VT8233

VT8233

PONTE SUL

PONTE SUL

HD

HD

HD

HD

LPC

SERIAL

SERIAL

USB

USB

USB

USB

USB

USB

USB

USB

USB

USB

USB

USB

SUPER

SUPER

IO

IO

AC97

AC97

Abril

Abril2010

2010

MC97

MC97

TECLADO

TECLADO

MOUSE

MOUSE

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

PARALELA

PARALELA

DISQUETE

DISQUETE

13

13

CLASSIFICAÇÃO

CLASSIFICAÇÃODA

DAMEMÓRIA

MEMÓRIA

AAARQUITETURA

ARQUITETURAIA-32,

IA-32,NA

NALINHA

LINHADE

DEPROCESSADORES

PROCESSADORESP6

P6EEPENTIUM

PENTIUM44PREVÊ

PREVÊAASEGUINTE

SEGUINTE

CLASSIFICAÇÃO

DE

ÁREAS

DE

MEMÓRIA

QUANTO

À

CACHEABILIDADE:

CLASSIFICAÇÃO DE ÁREAS DE MEMÓRIA QUANTO À CACHEABILIDADE:

CÓDIGO

TIPO

CACHEÁVEL

WB

LEITURA

ESPECULATIVA

MODELO DE

ORDENAMENTO

UC

STRONG

UNCACHEABLE

NÃO

NÃO

NÃO

STRONG ORDERING

UC-

UNCACHEABLE

NÃO

NÃO

NÃO

STRONG ORDERING MAS

ALTERÁVEL VIA MTRR´S

WC

WRITE COMBINE

NÃO

NÃO

SIM

WEAK ORDERING

WT

WRITE THROUGH

SIM

NÃO

SIM

SPECULATIVE

PROCESSOR ORDERING

WB

WRITE BACK

SIM

SIM

SIM

SPECULATIVE

PROCESSOR ORDERING

WP

WRITE

PROTECTED

SIM

(SÓ READS)

NÃO

SIM

SPECULATIVE

PROCESSOR ORDERING

O TIPO UTILIZADO PARA UMA DETERMINADA REGIÃO DA MEMÓRIA PODE SER AJUSTADO:

O TIPO UTILIZADO PARA UMA DETERMINADA REGIÃO DA MEMÓRIA PODE SER AJUSTADO:

- DINÂMICAMENTE PARA MEMÓRIA LINEAR ATRAVÉS DA PAT - PAGE ATTRIBUTE TABLE

- DINÂMICAMENTE PARA MEMÓRIA LINEAR ATRAVÉS DA PAT - PAGE ATTRIBUTE TABLE

- -ESTÁTICAMENTE

ESTÁTICAMENTE- -PARA

PARAMEMÓRIA

MEMÓRIAFÍSICA

FÍSICA- -ATRAVÉS

ATRAVÉSDOS

DOSMTRR’S

MTRR’S- MTRR’S

MTRR’S- -MEMORY

MEMORYTYPE

TYPERANGE

RANGEREGISTERS

REGISTERS

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

14

14

REGISTRADORES

REGISTRADORESMSR

MSR

NA

NAARQUITETURA

ARQUITETURAIA-32,

IA-32,AAPARTIR

PARTIRDA

DALINHA

LINHAP6,

P6,FORAM

FORAMINTRODUZIDOS

INTRODUZIDOSREGISTRADORES

REGISTRADORESDE

DE

HARDWARE

COM

FINALIDADES

ESPECIAIS

E

DEPENDENTES

DO

MODELO

DE

PROCESSADOR,

HARDWARE COM FINALIDADES ESPECIAIS E DEPENDENTES DO MODELO DE PROCESSADOR,

SIGNIFICANDO

SIGNIFICANDOQUE

QUENÃO

NÃOHÁ

HÁGARANTIAS

GARANTIASDE

DEQUE

QUEEM

EMMODELOS

MODELOSFUTUROS

FUTUROSOOMESMO

MESMO

REGISTRADOR

E

SUAS

FUNÇÕES

ESTARÃO

DISPONÍVEIS.

REGISTRADOR E SUAS FUNÇÕES ESTARÃO DISPONÍVEIS.

SÃO

SÃOOS

OSMSR’S

MSR’S- -MODEL

MODELSPECIFIC

SPECIFICREGISTERS

REGISTERS- -ACESSADOS

ACESSADOSVIA

VIAINSTRUÇÕES

INSTRUÇÕESRDMSR

RDMSREESTMSR

STMSR

ALGUNS

ALGUNSMSR’S

MSR’SENTRETANTO

ENTRETANTOFORAM

FORAMPROMOVIDOS

PROMOVIDOSAAREGISTRADORES

REGISTRADORESDEFINITIVOS,

DEFINITIVOS,

SIGNIFICANDO QUE A INTEL PRETENDE MANTER SEUS ENDEREÇOS E SUA FUNCIONALIDADE

SIGNIFICANDO QUE A INTEL PRETENDE MANTER SEUS ENDEREÇOS E SUA FUNCIONALIDADE

EM TODA A LINHA FUTURA DE PROCESSADORES.

EM TODA A LINHA FUTURA DE PROCESSADORES.

É O CASO DO REGISTRADOR PAT (PAGE ATTRIBUTE TABLE) E DOS MTRR´S - MEMORY TYPE

É O CASO DO REGISTRADOR PAT (PAGE ATTRIBUTE TABLE) E DOS MTRR´S - MEMORY TYPE

RANGE REGISTERS - UTILIZADOS NA DEFINIÇÃO DO TIPO DE CACHEABILIDADE DAS DIVERSAS

RANGE REGISTERS - UTILIZADOS NA DEFINIÇÃO DO TIPO DE CACHEABILIDADE DAS DIVERSAS

ÁREAS DE MEMÓRIA.

ÁREAS DE MEMÓRIA.

OOMSR

MSRIA32_CR_PAT

IA32_CR_PAT

OOPAT

PATÉÉUM

UMREGISTRADOR

REGISTRADORDE

DE64

64BITS

BITS- -DIVIDIDO

DIVIDIDOEM

EM88CAMPOS

CAMPOSDE

DE88BITS

BITS- -PAT0

PAT0AAPAT7

PAT7

--

CADA CAMPO PODE ESPECIFICAR ATÉ 256 POSSÍVEIS TIPOS DE CACHEAMENTO

CADA CAMPO PODE ESPECIFICAR ATÉ 256 POSSÍVEIS TIPOS DE CACHEAMENTO

ATUALMENTE APENAS OS TRÊS BITS MENOS SIGNIFICATIVOS SÃO UTILIZADOS

ATUALMENTE APENAS OS TRÊS BITS MENOS SIGNIFICATIVOS SÃO UTILIZADOS

SOMENTE

SOMENTEOS

OSTIPOS

TIPOSUC,

UC,UC-,WC,

UC-,WC,WT,

WT,WB,

WB,EEWP

WPSÃO

SÃOPREVISTOS

PREVISTOSNAS

NASVERSÕES

VERSÕESATUAIS.

ATUAIS.

CADA PÁGINA OU DIRETÓRIO DE PÁGINAS SELECIONA 1 DOS 8 CAMPOS PAT0 A PAT7 NO PAT

CADA PÁGINA OU DIRETÓRIO DE PÁGINAS SELECIONA 1 DOS 8 CAMPOS PAT0 A PAT7 NO PAT

ATRAVÉS

DOS BITS PWT, PCD E PAT NAS PTE´S OU PDE´S.

ATRAVÉS DOS BITS PWT, PCD E PAT NAS PTE´S OU PDE´S.

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

15

15

SELEÇÃO

SELEÇÃODO

DOMODELO

MODELODE

DECACHE

CACHEVIA

VIAPAT

PAT

31

12 11

PTE

Abril

Abril2010

2010

PAGE BASE ADDRESS

9 8 7 6 5 4 3 2 1 0

AVAIL.

P

G A D

T

P P U W

A C W / / P

D T S R

PAT

PCD

PWT

CAMPO

SELECIONADO

VALOR DEFAULT

0

0

0

PAT0

WB

0

0

1

PAT1

WT

0

1

0

PAT2

UC-

0

1

1

PAT3

UC

1

0

0

PAT4

WB

1

0

1

PAT5

WT

1

1

0

PAT6

UC-

1

1

1

PAT7

UC

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

16

16

MAPEAMENTO

MAPEAMENTODO

DOTIPO

TIPODE

DECACHE

CACHEVIA

VIAMTRR’S

MTRR’S

OS

OSREGISTRADORES

REGISTRADORESMTRR’S

MTRR’SSERVEM

SERVEMPARA

PARAMAPEAR

MAPEARREGIÕES

REGIÕESDA

DAMEMÓRIA

MEMÓRIAFÍSICA

FÍSICAQUANTO

QUANTO

AO

MODELO

DE

CACHEABILIDADE

UTILIZADO

PARA

AQUELA

REGIÃO

AO MODELO DE CACHEABILIDADE UTILIZADO PARA AQUELA REGIÃO

SÃO

SÃOGERALMENTE

GERALMENTEAJUSTADOS

AJUSTADOSPELA

PELABIOS

BIOSDURANTE

DURANTEAAINICIALIZAÇÃO

INICIALIZAÇÃODO

DOSISTEMA,

SISTEMA,PODENDO

PODENDO

SER

DEPOIS

ALTERADOS

PELO

SISTEMA

OPERACIONAL

TAMBÉM

NA

INICIALIZAÇÃO.

SER DEPOIS ALTERADOS PELO SISTEMA OPERACIONAL TAMBÉM NA INICIALIZAÇÃO.

- IA32_MTRR_CAP - DEFINE AS OPÇÕES DISPONÍVEIS NOS DEMAIS MTRR’S, INCLUSIVE A

- IA32_MTRR_CAP - DEFINE AS OPÇÕES DISPONÍVEIS NOS DEMAIS MTRR’S, INCLUSIVE A

QUANTIDADE

QUANTIDADEDE

DEREGISTRADORES

REGISTRADORESPARA

PARAREGIÕES

REGIÕESDE

DETAMANHO

TAMANHOVARIÁVEL

VARIÁVEL

- - IA32_MTRR_DEF_TYPE

IA32_MTRR_DEF_TYPE- -DEFINE

DEFINEOOMODELO

MODELODEFAULT

DEFAULTAAUTILIZAR

UTILIZARQUANDO

QUANDOUMA

UMAREGIÃO

REGIÃODE

DE

MEMÓRIA NÃO ESTÁ MAPEADA POR NENHUM OUTRO REGISTRADOR MTRR.

MEMÓRIA NÃO ESTÁ MAPEADA POR NENHUM OUTRO REGISTRADOR MTRR.

- - IA32_MTRR_FIX64K_00000

IA32_MTRR_FIX64K_00000- -MAPEIA

MAPEIA88REGIÕES

REGIÕESFIXAS

FIXASDE

DE64

64KKCADA

CADAENTRE

ENTRE00000

00000EE7FFFF

7FFFF

--

IA32_MTRR_FIX16K_80000 E

IA32_MTRR_FIX16K_80000 E

IA32_MTRR_FIX16K_A0000

IA32_MTRR_FIX16K_A0000- -MAPEIAM

MAPEIAM16

16REGIÕES

REGIÕESFIXAS

FIXASDE

DE16

16KKCADA

CADAENTRE

ENTRE00000

00000EEBFFFF

BFFFF

--

IA32_MTRR_FIX4K_C0000

IA32_MTRR_FIX4K_C0000ATÉ

ATÉ

IA32_MTRR_FIX4K_F8000 - MAPEIAM 64 REGIÕES FIXAS DE 4K CADA ENTRE C0000 E FFFFF

IA32_MTRR_FIX4K_F8000 - MAPEIAM 64 REGIÕES FIXAS DE 4K CADA ENTRE C0000 E FFFFF

--

IA32_MTRR_PHYSBASEn

IA32_MTRR_PHYSBASEnEE

IA32_MTRR_PHYSMASKn - MAPEIAM REGIÕES DE TAMANHO VARIÁVEL DA MEMÓRIA.

IA32_MTRR_PHYSMASKn - MAPEIAM REGIÕES DE TAMANHO VARIÁVEL DA MEMÓRIA.

--

IA32_MTRR_PHYSBASEn - CARACTERIZA O ENDEREÇO BASE E O TIPO DE CACHE A USAR

IA32_MTRR_PHYSBASEn - CARACTERIZA O ENDEREÇO BASE E O TIPO DE CACHE A USAR

IA32_MTRR_PHYSMASKn - CONTÉM MÁSCARA QUE CARACTERIZA O TAMANHO DA REGIÃO

IA32_MTRR_PHYSMASKn - CONTÉM MÁSCARA QUE CARACTERIZA O TAMANHO DA REGIÃO

NAS

NASVERSÕES

VERSÕESATUAIS

ATUAISnn==00AA77(8(8REGISTRADORES).

REGISTRADORES).

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

17

17

LAYOUT

LAYOUTDOS

DOSMTRR’S

MTRR’S

63

10

W

C

IA32_MTRR_CAP

8 7

F

I

X

0

VCNT

ESPECIFICA SUPORTE A WRITE COMBINED

ESPECIFICA SUPORTE A REGISTRADORES DE TAMANHO FIXO

ESPECIFICA SUPORTE A QUANTIDADE DE REGISTRADORES VARIÁVEIS

63

10 11

IA32_MTRR_DEF

E

7

F

E

0

TYPE

MTRR’S ENABLE BIT

FIXED RANGE MTRR’S ENABLE BIT

ESPECIFICA O TIPO DE CACHE DEFAULT UTILIZADO

63

56

TYPE7

Abril

Abril2010

2010

15

IA32_MTRR_FIXXK_XXXXXX

8 7

TYPE1

0

TYPE0

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

18

18

LAYOUT

LAYOUTDE

DEMTRR’S

MTRR’SPARA

PARAREGIÕES

REGIÕESVARIÁVEIS

VARIÁVEIS

63

35

IA32_MTRR_PHYSBASEn

12

PHYS BASE

7

0

TYPE

ESPECIFICA ENDEREÇO BASE ALINHADO EM 4K

ESPECIFICA O TIPO DE CACHE UTILIZADO PARA A REGIÃO

63

35

IA32_MTRR_PHYSMASKn

1211 10

PHYS MASK

V

0

RESERVADO

MÁSCARA DETERMINA REGIÃO AFETADA

VALIDA O PAR DE REGISTRADORES

2 PARES DE REGISTRADORES PRECISAM SER RESERVADOS PARA USO DO SISTEMA

2 PARES DE REGISTRADORES PRECISAM SER RESERVADOS PARA USO DO SISTEMA

A MÁSCARA É DETERMINADA PELA REGRA:

A MÁSCARA É DETERMINADA PELA REGRA:

ENDEREÇO

MÁSCARA = ENDEREÇO BASE AND MÁSCARA

ENDEREÇONA

NAREGIÃO

REGIÃOAND

AND MÁSCARA = ENDEREÇO BASE AND MÁSCARA

O ENDEREÇO BASE DEVE ESTAR ALINHADO EM 2n nCOM n > 12 OU n > M

O ENDEREÇO BASE DEVE ESTAR ALINHADO EM 2 COM n > 12 OU n > M

ONDE 2MMÉ O COMPRIMENTO DO BLOCO ESPECIFICADO

ONDE 2 É O COMPRIMENTO DO BLOCO ESPECIFICADO

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

19

19

CONSISTÊNCIA

CONSISTÊNCIAENTRE

ENTREAAPAT

PATEEOS

OSMTRR’S

MTRR’S

QUANDO

QUANDOUM

UMDETERMINADO

DETERMINADOMODELO

MODELODE

DECACHEAMENTO

CACHEAMENTOÉÉAPLICADO

APLICADOAAUMA

UMAPÁGINA

PÁGINAOU

OU

CONJUNTO

DE

PÁGINAS

ATRAVÉS

DO

REGISTRADOR

PAT,

O

MÉTODO

EFETIVAMENTE

CONJUNTO DE PÁGINAS ATRAVÉS DO REGISTRADOR PAT, O MÉTODO EFETIVAMENTE

APLICADO DEPENDERÁ DO CORRESPONDENTE AJUSTE PARA A MEMÓRIA FÍSICA

APLICADO DEPENDERÁ DO CORRESPONDENTE AJUSTE PARA A MEMÓRIA FÍSICA

CORRESPONDENTE,

CORRESPONDENTE,DETERMINADO

DETERMINADOPELOS

PELOSREGISTRADORES

REGISTRADORESMTRR.

MTRR.

OOMODELO

MODELOEFETIVAMENTE

EFETIVAMENTEAPLICADO

APLICADOEM

EMCADA

CADACASO

CASOPODE

PODESER

SEROBTIDO

OBTIDODE

DEUMA

UMATABELA

TABELANO

NO

MANUAL. DE UMA FORMA GERAL VALE O MODELO MAIS RESTRITIVO. CASO OS MTRR’S

MANUAL. DE UMA FORMA GERAL VALE O MODELO MAIS RESTRITIVO. CASO OS MTRR’S

ESPECIFIQUEM

ESPECIFIQUEMUMA

UMAREGIÃO

REGIÃOCOMO

COMOUC,

UC,OOMODELO

MODELONÃO

NÃOPODERÁ

PODERÁSER

SERALTERADO

ALTERADOPELA

PELAPAT.

PAT.

EX. MTRR ESPECIFICA WB, A PAT PODE REVERTER O MODELO PARA WT.

EX. MTRR ESPECIFICA WB, A PAT PODE REVERTER O MODELO PARA WT.

EM

EMCASO

CASODE

DEOPERAÇÃO

OPERAÇÃOCOM

COMMÚLTIPLOS

MÚLTIPLOSPROCESSADORES,

PROCESSADORES,AACONSISTÊNCIA

CONSISTÊNCIADOS

DOSMTRR’S

MTRR’SEE

DAS PAT’S DE CADA PROCESSADOR DEVE SER MANTIDA PELO SISTEMA OPERACIONAL

DAS PAT’S DE CADA PROCESSADOR DEVE SER MANTIDA PELO SISTEMA OPERACIONAL

O HARDWARE NÃO DISPÕE DE MECANISMOS PARA GARANTIR A CONSISTÊNCIA DOS

O HARDWARE NÃO DISPÕE DE MECANISMOS PARA GARANTIR A CONSISTÊNCIA DOS

REGISTRADORES NOS VÁRIOS PROCESSADORES DE UM SISTEMA MULTIPROCESSADO.

REGISTRADORES NOS VÁRIOS PROCESSADORES DE UM SISTEMA MULTIPROCESSADO.

Abril

Abril2010

2010

Arq.

Arq.eeOrg.

Org.Computadores

Computadores- -Prof.

Prof.Gortan

Gortan- -6.6.Aula

Aula- -Cache

Cache

20

20