Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

MICROPROCESSADORES

1º TESTE

Ano Lectivo: 2003/2004

Data: 30 de Abril de 2004

Ano Curricular: 1º Ano – 2º Semestre

Duração: 1h30

INFORMAÇÕES GERAIS

1. Identifique todas as folhas do enunciado com nome e nº.

2. Mantenha na secretária apenas a sua identificação e uma caneta (azul ou preta).

3. Responda no espaço delimitado a seguir a cada questão.

4. Utilize o verso da página, onde se encontra a pergunta, para rascunho ou para espaço adicional.

5. A não entrega do teste tem o mesmo significado que a não comparência ao teste.

1 de 7

Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

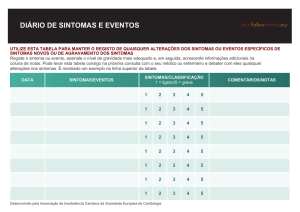

I - Unidade de Processamento

DATA

Sel D

DA

FSUA

Escrita de

Registos

Unidade de

Armazenamento

Sel A

AA

Sel B

BA

A

B

Endereço

Const.

Dado

0 1

MUX B

A

Função

Bits de

Estado

MB

Nota: RD, RA e RB correspondem aos registos seleccionados, respectivamente, pelos

sinais SelD, SelA e SelB.

DA, AA, BA

Função Cod.

R0

00

R1

01

R2

10

R3

11

B

FSUF

Unidade

Funcional

C,N,Z,V

DATA_IN

0 1

MUX D

Considere a seguinte Unidade de Processamento (UP) composta por uma Unidade de

Armazenamento (UA), com 4 registos (R0, R1, R2 e R3) de 8 bits, e uma Unidade

Funcional (UF) que implementa as 8 funções indicadas na tabela. A presente UA, para

compensar o reduzido número de operações de manipulação de dados da UF,

especificadas pelo sinal FSUF, incorpora um conjunto de funções suplementares de

transferências de dados entre registos, conforme descrito pelo sinal FSUA. As linhas

Endereço, Dado e Data_In destinam-se à comunicação com uma memória externa.

MD

FSUF

MB

MD

Função

Cod.

Função Cod. Função Cod.

B

000 Constante

0

Função

0

A+B

001

Registo

1

DataIn

1

A-B

010

A+1

011

AND (A,B)

100

OR (A,B)

101

NOT A

110

SR A

111

FSUA

Função

Não Escreve

RD = DATA

Ri = 0 (i=0 ... 3)

RA <> RB (Swap)

Cod.

00

01

10

11

1. [2,5 Val] Analise os dados fornecidos sobre a UP e assinale a resposta correcta em cada alínea:

a) A UP inclui uma Unidade de Armazenamento composta por __ registos de __ bits.

8, 4;

4, 8;

4, 4;

8, 8.

b) A UP permite endereçar directamente uma memória de __ palavras de __ bits.

256,16;

16,16;

256,8;

16,8.

c) A dimensão mínima da Palavra de Controlo, nas condições do enunciado, é de __ bits.

20;

9;

12;

13.

d) O simples aumento da complexidade da UF para 32 funções conduz _____ da dimensão da Palavra de Controlo,

nesta mesma situação o número de registos da UA deve ser ______.

ao aumento, expandido; à redução, expandido;

ao aumento, mantido;

à manutenção, reduzido;

e) A execução de uma micro-operação é realizada em ___ ciclo(s) do sinal de relógio.

1;

2;

1 ou 2;

número variável.

2. [1,5 Val] Defina um formato para a palavra de controlo e descreva para a operação indicada o conteúdo da(s) palavra(s) de

controlo necessárias à sua execução. (Sugestão: Para uma melhor legibilidade da(s) palavra(s) de controlo consideradas

utilize linguagem simbólica, isto é, as designações das funções e não as suas codificações.)

R3 ← (DATA_IN – R1)/2

2 de 7

Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

3. [2,5 Val] Considere uma Unidade de Armazenamento de 4 registos de 8 bits que permita incorporar as operações FSUA

especificadas na tabela da página anterior. Projecte a lógica combinatória para gerar o sinal de activação do carregamento

paralelo (LOAD_H) do registo R1. Suponha que o registo apenas tem o LOAD como sinal de controlo, portanto, os únicos

modos de operação serão manutenção do dado anterior ou carregamento paralelo. Admita, ainda e por simplicidade, que as

entradas de selecção SelD, SelA e SelB são entradas de descodificadores de 2/4 e que as respectivas saídas estão

identificadas com SD0 a SD3, SA0 a SA3 e SB0 a SB3, isto é, a entrada SelD = 01 activará o sinal SD1.

4. [2,5 Val] Admita que pretende projectar uma U. Aritmética para implementar as funções indicadas na tabela, considere,

ainda, que lhe é disponibilizado um somador completo de 8 bits. Projecte o circuito de lógica combinatória necessário a

geração do bit menos significativo do operando Y e ainda a lógica para activação do Cin.

Bloco A

F(A,FSUF)

Cin

X

Soma

Somador S

Bloco B

F(B,FSUF)

Y

Carry

FSUF

Função

B

A+B

A-B

A+1

AND (A,B)

OR (A,B)

NOT A

SR A

Cod.

000

001

010

011

100

101

110

111

3 de 7

Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

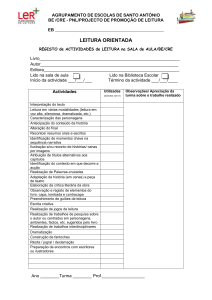

II - Unidade de Controlo

Considere a seguinte arquitectura de ciclo único:

Considere para esta questão a UP descrita

anteriormente.

Bits de

Estado

PL,JB,BC

Controlo e

Actualização

do PC

Sel D

Offset

DATA

DA

FSUA

Escrita de

Registos

Formatos das Instruções (10 bits):

Endereçamento por Registo

OpCode DR SA SB

Endereçamento Imediato

OpCode DR Operan.

Enderçamento Relativo

OpCode Offset

Unidade de

Armazenamento

Sel A

AA

Sel B

BA

A

B

Endereço

PC

Conc. 0s

Const.

Dado

UP

End.

0 1

MUX B

Memória de

Instruções

A

Função

Data Out

Bits de

Estado

PC – Registo de 8 bits

MB

MW

Data In MW End.

B

FSUF

Unidade

Funcional

Memória

deDados

C,N,Z,V

Descodificador

de Instruções

DAT A_IN

SelD,SelA,SelB,FSUA,

FSUF, MB,MD, MW

0 1

MUX D

OpCode

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Operação

MOVI DR, Op

ADD DR, SA, SB

SUB DR, SA, SB

INC DR

AND DR, SA, SB

OR DR, SA, SB

NOT DR

SR DR

LD DR, M[SA]

STR M[SA], SB

JMP Offset

JZ Offset

JN Offset

CMP SA, SB

SWAP SA, SB

INIT

PL – (0- Incremento ou

1- Carregamento Paralelo)

JB – (0- Salto Incondicional ou 1-Salto

Condicional)

BC – Selecção da Condição de Salto

0 – Salta se Z,

1 – Salta se N

Data Out

SelD, Sela e SelB – Selecção de um registo de

R0 a R3

MD

Descrição

(DR) ← Op

(DR) ← (SA)+(SB)

(DR) ← (SA)-(SB)

(DR) ← (DR) + 1

(DR) ← (SA) AND (SB)

(DR) ← (SA) OR (SB)

(DR) ← NOT (DR)

(DR) ← SR (DR)

(DR) ← M[(SA)]

M[(SA)] ← (SB)

(PC) ← (PC) + Offset

Z: (PC) ← (PC) + Offset

N: (PC) ← (PC) + Offset

(SA) – (SB)

(SA) ↔ (SB)

(Ri) ← 0, i = 0..3

Nota: As flags Z e N são guardadas num

registo na UF.

Bits de Estado

N, Z

N, Z

N, Z

N, Z

Z

Z

Z

Z

não são alteradas

não são alteradas

não são alteradas

não são alteradas

não são alteradas

N, Z

não são alteradas

não são alteradas

Endereçamento

Imediato

Registo

Registo

Registo

Registo

Registo

Registo

Registo

Registo

Registo

Relativo

Relativo

Relativo

Registo

Registo

Registo

4 de 7

Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

1. [2,5 Val] Assinale a resposta correcta em cada alínea:

a)

Considerando o armazenamento de programas com um máximo de 200 instruções numa memória, com a dimensão

mínima, o número de linhas de endereçamento deverá ser de ___ e a dimensão das palavras deverá ser de ___ bits.

200, 8;

256, 10;

8, 10;

16, 8.

b) Para o conjunto de instruções apresentado o(s) sinai(s) de selecção ___ retiram-se directamente da instrução enquanto

o(s) sinal(s) de selecção ___ devem ser gerados pelo descodificador de instruções.

(SelD,SelA), (SelB);

(SelD), (SelA,SelB);

(SelD,SelB), (SelA);

(SelA), (SelD,SelB);

c) Admitindo que pretendia utilizar uma memória para implementar toda a lógica combinatória relativa ao

descodificador de instruções (excluindo os sinais SelD, SelA e SelB), a dimensão mínima da memória deverá ser de

___ palavras de ___ bits.

4, 11;

16, 11;

4, 8;

16, 8.

d) No caso do “offset” ser especificada através dos campos DR, SA e SB da instrução, o bloco de extensão de sinal

deverá adicionar ___ bits.

4;

2;

1;

0.

e) No caso da “constante” ser especificada através dos campos SA e SB da instrução, o bloco de concatenação de zeros

deve adicionar ___ bits

4;

2;

1;

0.

2. Considere que se pretende projectar a Unidade de Controlo para a arquitectura da pergunta 1 de modo a permitir executar o

conjunto de instruções da tabela anterior (Admita que as Flags são guardadas num registo na UF).

a)

[1,5 Val] Determine a expressão da função lógica correspondente ao sinal MB=f(OpCode), a ser gerado pelo

Descodificador de Instruções.

b) [1,5 Val] Considere os seguintes conteúdos nas memórias de instruções e dados. Preencha a tabela com o conteúdo

dos registos e memória de dados após a execução de cada instrução e apenas quando se der alguma alteração.

Nota: caso alguma instrução seja executada mais do que uma vez apresente os valores relativos apenas à primeira

execução.

Endereço

..

01

02

03

04

05

06

07

08

Instrução

...

MOVI R0, 00

LD R1, M[R0]

INC R0

LD R2, M[R0]

CMP R2, R3

JZ +2

JMP -4

STR M[R0], R1

PC

01

02

03

04

05

06

07

03

09

Z

0

1

-0

-0

----

N

0

--0

-1

----

R0

07

00

-01

------

R1

01

-01

-------

R2

02

---02

-----

R3

04

---------

M[0]

01

---------

M[1]

02

---------

M[2]

03

---------

M[3]

04

-------01

5 de 7

Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

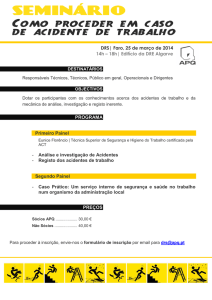

3. [2,5 Val] Considere a seguinte arquitectura elementar de computador de ciclo múltiplo:

PL,PI

Controlo e

Actualização

do PC

PC

Escrita de

Registos

DATA

Offset

Sel D

Para

Memória

DA

Formatos das Instruções (10 bits):

Endereçamento por Registo

OpCode DR SA SB

Endereçamento Imediato

OpCode DR Operan.

Enderçamento Relativo

OpCode Offset

FSUA

Unidade de

Armazenamento

Sel A

Da

Memória

AA

Sel B

BA

A

B

Do PC

Endereço

IL

IR

Conc. 0s

MC

0 1

MUX B

Bits de

Estado

Const.

Dado

UP

0 1

MUX B

MS

A

CAR

Controlo

CAR

Função

Bits de

Estado

MM

0 1

MUX B

MB

MW

Data In MW End.

B

FSUF

Memória

de Instruções e

Dados

Unidade

Funcional

C,N,Z,V

Memória de

Controlo

NA

Data Out

PC – Registo de 8 bits

PI – ( 0- Inactivo, 1- Incremento)

PL – (0- Inactivo, 1- Carregamento Paralelo)

IR – Registo de 8 bits

IL – (0- Inactivo, 1- Carregamento)

MS – Selecciona modo de actualização do

registo

CAR

(00Incremento,

01Carregamento, 10- Carregamento se Z, 11Carregamento se N)

MC – Selecciona fonte para carregamento de

CAR (0- Memória de Controlo, 1- IR)

MM – Selecciona Endereço

(0- do operando A, 1- do PC)

DATA_IN

MS, MC, IL PI, PL,

TD, TA, TB, FSUA,

FSUF, MB, MD,

MW, MM

0 1

MUX D

MD

Para IR

SelD, Sela e SelB – Selecção de um registo de

R0 a R4 (o registo R4 é um registo auxiliar de

uso exclusivo das microinstruções)

Nota: As flags Z e N são guardadas num

registo na UF.

a)

Na presente arquitectura de ciclo múltiplo a aquisição da instrução, a descodificação da instrução e a execução da

operação associada à instrução é executada em ___ ciclo(s) de relógio.

1;

2;

3;

número variável.

b) Em geral a arquitectura de ciclo múltiplo é mais ____ na execução de instruções _____ quando comparada com a

arquitectura de ciclo único.

lenta, complexas;

lenta, elementares;

rápida, elementares;

Nenhuma das anteriores

c) Durante os vários ciclos de execução de uma mesma instrução o registo IR __ o seu conteúdo, enquanto o registo

CAR ___ o respectivo conteúdo.

mantém, altera;

altera; altera;

mantém, mantém;

altera, mantém.

d) A memória de instruções e dados é endereçada pelo _____ para aquisição de instruções pelo ____ para escrita/leitura

de dados

operando A, IR;

Operando A; PC

PC, Operando A

PC, IR

e) Na arquitectura definida o deslocamento associado a uma instrução de salto pode assumir valores entre _ e _.

0, 256;

-31, 32;

-32, 31

0, 255;

6 de 7

Departamento de Engenharia Electrotécnica e de Computadores

Instituto Superior Técnico - Universidade Técnica de Lisboa

Microprocessadores 2003/2004

LEEC

Nome:

Nº:____________

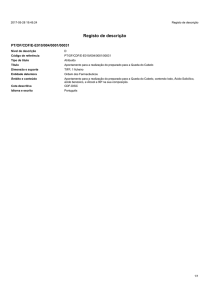

5. Considere a arquitectura de computador elementar de ciclo múltiplo. Admita a utilização de: (1) uma memória de controlo

de 64 palavras de N bits; (2) 1 registo auxiliar R4 cuja utilização é restrita às micro-instruções, passando nesta situação o

endereçamento dos registo a ser realizado por 3 bits (o endereço do registo Ri corresponderá à representação binária de i,

na palavra de controlo apenas se especifica a “1” o bit TD, TA e TB a quando da utilização do registo R4 para DR, SA ou

SB).

a)

[1,5 Val] Complete as linhas da memória de controlo de modo a definir o conjunto de micro-instruções (IF, EX0, ...)

necessárias à execução das seguintes instruções (utilize notação simbólica):

(DR) ← (SA)+(SB)

(SA) ↔ (SB)

M[(SA)] ← (SB)

N: (PC) ← (PC) + Offset

ADD DR, SA, SB

SWAP SA, SB

STR M[SA], SB

JN Offset

Notação simbólica a utilizar em cada campo das micro-instruções:

MS

00-INC

01-LOAD

10-LIFZ

11-LIFN

MC

0-MC

1-IR

IL

0-NL

1-LD

PI

0-NI

1-IN

PL

0-NL

1-LD

TD

0-DR

1-R4

TA

0-SA

1-R4

TB

0-SB

1-R4

MB

0-CT

1-RG

FSUF

Função

MD

0-FC

1-DT

FSUA

00-NW

01-WR

10-IN

11-SW

MM

0-RG

1-PC

MW

0-NW

1-WR

Conteúdo parcial da memória de controlo:

Endereço

IF

EX0

MOVI

ADD

SWAP

STR

JN

JN1

JN2

JN2

JN2

* Endereço

NA*

EX0

--IF

IF

IF

IF

JN2

IF

IF

IF

IF

MS

LOAD

LOAD

LOAD

LOAD

LOAD

LOAD

LIFN

LOAD

LOAD

LIFN

LIFN

MC

MC

IR

MC

MC

MC

MC

MC

MC

MC

MC

MC

IL

LD

NL

NL

NL

NL

NL

NL

NL

NL

NL

NL

PI

IN

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

PL

NL

NL

NL

NL

NL

NL

NL

NL

LD

LD

LD

TD

----DR

DR

--------

TA

-----SA

SA

SA

------

TB

-----SB

SB

SB

------

MB

----CT

RG

--------

FSUF

----------------------F=B

A+B

--------

MD

----FC

FC

--------

FSUA

NW

NW

WR

WR

SW

NW

NW

NW

NW

NW

NW

MM

PC

------RG

------

MW

NW

NW

NW

NW

NW

WR

NW

NW

NW

NW

NW

b) [1,5 Val] Defina o fluxograma ASM correspondente a uma micro-rotina, conjunto de micro-instruções, que permita

implementar a seguinte instrução:

MULM DR, Op

M[DR] ← M[DR] x Op

Sugestão: Implemente a multiplicação através de Op somas do M[DR].

Nota: Neste caso pode utilizar o número de registos auxiliares que entender e não apenas R4

7 de 7