Trabalho 5: Projeto Elétrico, Leiaute e Análise de um

Oscilador em Anel

Dieison Soares Silveira

Universidade Federal do Rio Grande do Sul – UFRGS

Instituto de Informática

Programa de Pós-Graduação em Computação

[email protected]

1. Introdução

Este trabalho apresenta o projeto elétrico e o leiaute de um oscilador em anel

CMOS. O oscilador projetado utiliza cinco estágios de inversores CMOS estáticos de

mesmo tamanho, sendo esses inversores os desenvolvidos no primeiro trabalho da

disciplina. As simulações elétricas foram realizadas utilizando o esquemático após a

extração de elementos parasitas a partir do leiaute desenvolvido. Essas simulações

elétricas tiveram como targets dois níveis de tensão: 3,3 V e 1,0 V. Nesse projeto foram

aplicadas as regras de leiaute e os parâmetros do PDK (Physical Design Kit) da empresa

AMS para tecnologia CMOS 0,35µm.

A Seção 2 apresenta a metodologia utilizada no trabalho, identificando

ferramentas e parâmetros utilizados. Além disso, as restrições de projeto determinadas

para esse trabalho são apresentadas nessa seção. A Seção 3 apresenta a caracterização

elétrica do oscilador projetado, apresentando o diagrama esquemático utilizado e o

testbench utilizado. A Seção 4 apresenta o leiaute desenvolvido e a extração dos

parasitas desse leiaute. A Seção 5 apresenta a análise dos tempos de resposta para o

oscilador em anel para os dois níveis de tensão utilizados. Por fim, a Seção 6 apresenta

os resultados de potência dissipada, teórica e real, e a energia consumida pelo oscilador

em anel.

2. Metodologia e restrições do trabalho

Os resultados apresentados nesse trabalho foram obtidos através do software de

EDA Virtuoso da Cadence utilizando o simulador elétrico SPECTRE™. Na

caracterização elétrica foram adotados os seguintes passos:

Projeto lógico e elétrico do oscilador em anel CMOS

Projeto de leiaute do oscilador em anel CMOS

Cálculo dos tempos de resposta para as duas tensões utilizadas

Cálculo da potência média dissipada e RMS para frequência de chaveamento

atingida pelo oscilador

Cálculo da energia média consumida pelo oscilador durante um período

completo de oscilação para as duas tensões utilizadas

Trilhas de alimentação de Metal M1 com largura de 2µm

Altura da célula de 10 µm

Não utilizar polígonos de Metal M3 e M4

Fazer o leiaute minimizado, permitindo interconexão pelo abutment

Utilizar o comprimento mínimo de canal permitido pelas regras de leiaute

3. Caracterização elétrica

Considerando a metodologia e as restrições de projeto apresentados na Seção 2,

o projeto esquemático do oscilador em anel foi elaborado. As larguras de canal adotadas

para os inversores que compõem o oscilador em anel foram: 2 µm para os transistores

NMOS e 3 µm para os transistores PMOS. A Figura 1 apresenta o esquemático do

oscilador em anel com os cinco inversores.

Figura 1. Esquemático do oscilador em anel CMOS

A partir da Figura se pode perceber que existe apenas as entradas de

alimentação, VDD e GND, para o oscilador. Isto ocorre porque este oscilador utiliza

realimentação, onde a saída do quinto inversor está conectada na entrada do primeiro

inversor, isso acaba gerando um sinal de saída sem a necessidade de um sinal de

entrada.

Após as etapas iniciais de projeto esquemático e definição do símbolo, um

projeto esquemático de testbench foi desenvolvido. Esse projeto foi utilizado na

caracterização elétrica do oscilador em anel. A Figura 2 apresenta uma ilustração do

testbench utilizado. Pode também ser observado nesta figura a tensão de alimentação

que foi utilizada, neste caso de 1V, porém em outra análise foi utilizada a tensão de

3,3V.

Figura 2. Testbench utilizado na caracterização elétrica do oscilador

4. Leiaute e extração de parasitas do oscilador em anel

Antes da extração das características elétricas do oscilador em anel, foi realizada

a definição e verificação do seu leiaute sob as regras de leiaute e os parâmetros do PDK

(Physical Design Kit) da empresa AMS para tecnologia CMOS 0.35μm (processo

C35B4), considerando ainda todas as decisões de projeto já citadas nas seções

anteriores.

O leiaute proposto para o oscilador em anel pode ser visualizado na Figura 3.a.

Neste leiaute foi utilizado duas trilhas de metal para GND e uma para VDD com três

inversores no primeiro track e dois no segundo. A trilha de VDD foi colocada no centro

do leiaute e foi compartilhada pelos cinco inversores. Desta forma, minimizando os

elementos parasitas do circuito. Após todas as verificações, a versão extraída desse

leiaute, contendo os componentes parasitas modelados pela ferramenta, pode ser

visualizada na Figura 3.b. A largura dessa célula é de 9,35 μm, totalizando uma área

total de 187 (μm)², uma vez que este leiaute utiliza dois tracks de 10 μm.

(a)

(b)

Figura 3. Leiaute (a) e leiaute extraído com elementos parasitas (b) do oscilador

em anel CMOS

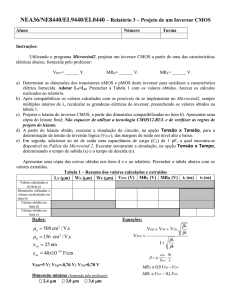

5. Análise dos tempos de resposta

Para caracterização dos tempos de resposta do oscilador em anel, uma análise

transiente dos sinais de saída dos inversores internos no testbench (Figura 2) foi

realizada. Desta forma, é possível obter os valores de tempo de subida e descida dos

sinais (Trise e Tfall, respectivamente), além da propagação de atraso H-L e L-H (Tphl e

Tplh). Utilizando as definições em Rabaey [Rabaey et al. 2004], esses valores podem ser

calculados conforme a Figura 4.

Figura 4. Definições de tempos de resposta

O atraso Tp das portas projetadas é dado como a média do pior atraso de todas

as possibilidades de Tphl e Tplh, considerando as seguintes condições de estresse:

temperatura ambiente e tensão nominal de alimentação VDD = 3,3V e 1,0V. Assim, é

preciso especificar quais análises de transição serão realizadas. As curvas obtidas na

análise transiente aplicada ao circuito para os dois níveis de tensão podem ser vistas nas

Figuras 5 e 6.

Figura 5. Curvas das saídas dos inversores com VDD = 3,3V

Figura 6. Curvas das saídas dos inversores com VDD = 1,0V

As Figuras 5 e 6 apresentam as curvas da análise transiente para as duas tensões

avaliadas, 3,3V e 1,0V. Na Figura 5 o gráfico temporal varia de 0 a 3 ns e pode ser visto

que a saída do quinto inversor fica estável a partir de 1,2 ns. Na Figura 6 o gráfico

temporal mostra um intervalo de tempo muito maior, de 0 a 400 ns, quando comparado

ao gráfico da Figura 5. Isto se deve ao fato que a tensão utilizada no oscilador da Figura

6 é menor que da Figura 5, para a mesma largura nos inversores. Desta forma, o

desempenho do oscilador com tensão de 1,0V é inferior ao desempenho do oscilador

com tensão de 3,3V, sendo que a saída desse oscilador fica estável somente após 385 ns.

A Tabela 1 apresenta os tempos de resposta para o oscilador em anel Tphl, Tplh,

Tr, Tf e Tp médio para os dois níveis de tensão avaliados, utilizando as informações

extraídas do leiaute. Além disso, é apresentada na Tabela 1 a frequência de oscilação

(Fosc) e a frequência de oscilação teórica (Fteórico) esperada como função dos atrasos e

número de estágios do oscilador. Para o cálculo da Fteórico foi utilizada a equação 1, onde

Tp é o tempo médio de propagação do inversor inv1x do segundo trabalho; N é o

número de estágios do oscilador em anel; e o fator 2 se deve ao fato de que para um

ciclo completo é necessário uma transição low-to-high e uma high-to-low. A equação 2

apresenta a fórmula para o cálculo que foi utilizado para estimar a frequência de

oscilação (Fosc) do oscilador em anel.

(1)

(2)

Tabela 1. Tempos de resposta do oscilador em anel CMOS

Tensão

Tr

Tf

Tphl

Tplh

Tp

Fosc

Fteórico

3,3 V

1,0 V

114 ps

864 ps

63 ps

326 ps

208 ps

2219 ps

208 ps

2219 ps

208 ps

2219 ps

1923 MHz

180 MHz

2941 MHz

434 MHz

Conforme pode ser observado na Tabela 1, os tempos de resposta obtidos para o

oscilador em anel com tensão de 1,0 são sempre mais lentos quando comparados aos

tempos obtidos com tensão em 3,3V. Isto se deve ao fato de que quanto maior for a

diferença de tensão entre o gate e source, menor é a resistência do canal e maior é a

corrente. Desta forma, tensões maiores fazem com que a resposta dos transistores sejam

mais rápidas.

Outro fato a ser observado na Tabela 1 é a diferença entre a Fosc e a Fteórica. A

Fteórico foi obtida considerando o Tp médio do inversor com resultados do leiaute

extraído, porém com fan-in e fan-out = 0. Dessa forma, já era esperado que a Fteórica

fosse maior que a Fosc, uma vez que para a Fteórica não foram consideradas as conexões

entre os inversores que compõem o oscilador em anel.

6. Potência e energia média consumida

A potência média e a energia consumida pelo oscilador em anel para as duas

tensões foram calculadas considerando a análise transiente utilizando as frequências

apresentadas na Tabela 1. Além desses resultados, são apresentados os resultados para

potência média teórica, a qual foi estimada utilizando as informações de potência obtida

pelo inversor inv1x. As equações 3 e 4 apresentam as fórmulas utilizadas para o cálculo

da potência média (Potav) e potência média teórica (Potteórica). Onde, isupply é a corrente

que está sendo transferida da tensão Vsupply sobre um intervalo de tempo t ϵ [0, T], e N é

o número de estágios utilizados no oscilador em anel.

∫

(3)

(4)

Para o cálculo do consumo de energia média, considerou-se um período

completo de oscilação para os dois níveis de tensão. Sendo para a tensão de 1,0V o

período T = 2219 ps e para a tensão de 3,3V o período T = 208 ps. A Tabela 2 sumariza

os resultados de potência e energia obtidos através das simulações para os dois níveis de

tensão utilizados.

Tabela 2. Resultados de potência média, RMS e energia consumida pelo

oscilador em anel CMOS

Tensão

1,0 V

3,3 V

Potência

Média

4,29 µW

2,31 mW

Potência

RMS

8,30 µW

2,45 mW

Potência

Teórica

8,6 µW

96,75 µW

Consumo

Energético

0,0095 pJ

0,48 pJ

Pode ser observado na Tabela 2 que os resultados estimados para potência

teórica são bem diferentes dos resultados medidos pela ferramenta para o oscilador em

anel. Isto já era esperado, uma vez que no cálculo da potência teórica muitos

componentes não estão sendo considerados, tais como: parasitas entre as células,

conexões e compartilhamento de trilha de VDD. Além disso, o inversor inv1x que

serviu de base para obtenção dos resultados teóricos possui na sua entrada uma fonte de

tensão que produz um pulso de entrada, o qual acaba gerando uma dissipação de

potência diferente quando comparado aos inversores utilizados no oscilador em anel.

Esse pulso de entrada acaba afetando principalmente os resultados para tensão de 1,0 V,

o qual está em um cenário mais suscetível a este estímulo. Isto faz com que o resultado

de potência teórica seja maior que a potência real nesse cenário. Já para os resultados

com tensão a 3,3V os componentes parasitas do leiaute completo do oscilador foram

predominantes, fazendo com que o resultado de potência média real fosse 25 vezes

maior que a potência teórica.

Assim, fica clara a importância que os resultados de leiaute possuem sobre o

processo de concepção de um circuito integrado. Expandindo esses resultados a um

nível de complexidade maior, essas diferenças que foram observadas para esta célula

devem se tornar ainda maiores. Dessa forma, a extração de componentes parasitas tornase essencial para obter resultados confiáveis de tempo e dissipação de potência do

circuito.

Referências

Rabaey, J. M., Chandrakasan, A., and kikolic, B. (2003). Digital Integrated Circuits: A

Design Perspective. Prentice Hall, 2nd edition.

AMS 0.35 µm CMOS C35 Design Rules, revisão 2.0, 2003.