Estudo da estrutura física do transistor de potência LDMOS

Gustavo Cortezi Espringman, Kimon Stylianos Pediatidakis, Michele Rodrigues Hempel Lima

FEI – Fundação Educacional Inaciana

[email protected]/ [email protected]

Resumo: Este trabalho de iniciação científica tem o objetivo de estudar

a estrutura física de um transistor LDMOS e comparar seu equivalente a

um transistor convencional. Foram feitas simulações referente aos dois

tipos de transistores variando sua largura, comprimento, espessura e

dopagem, assim foram feitos gráficos de corrente em função da tensão.

1. Introdução

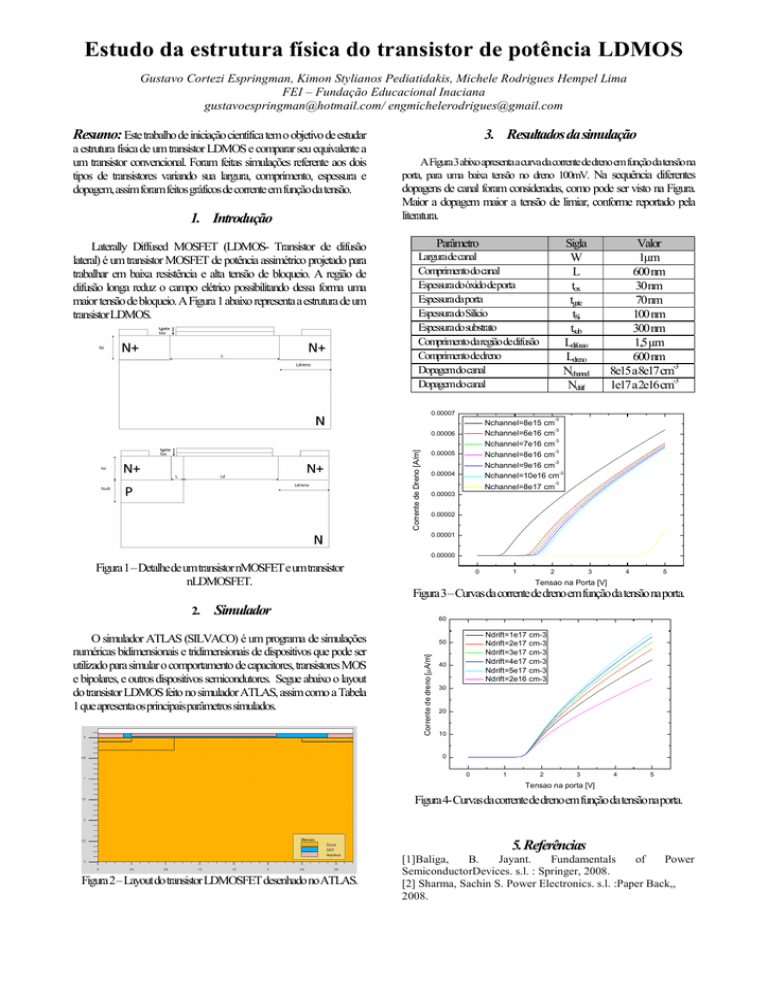

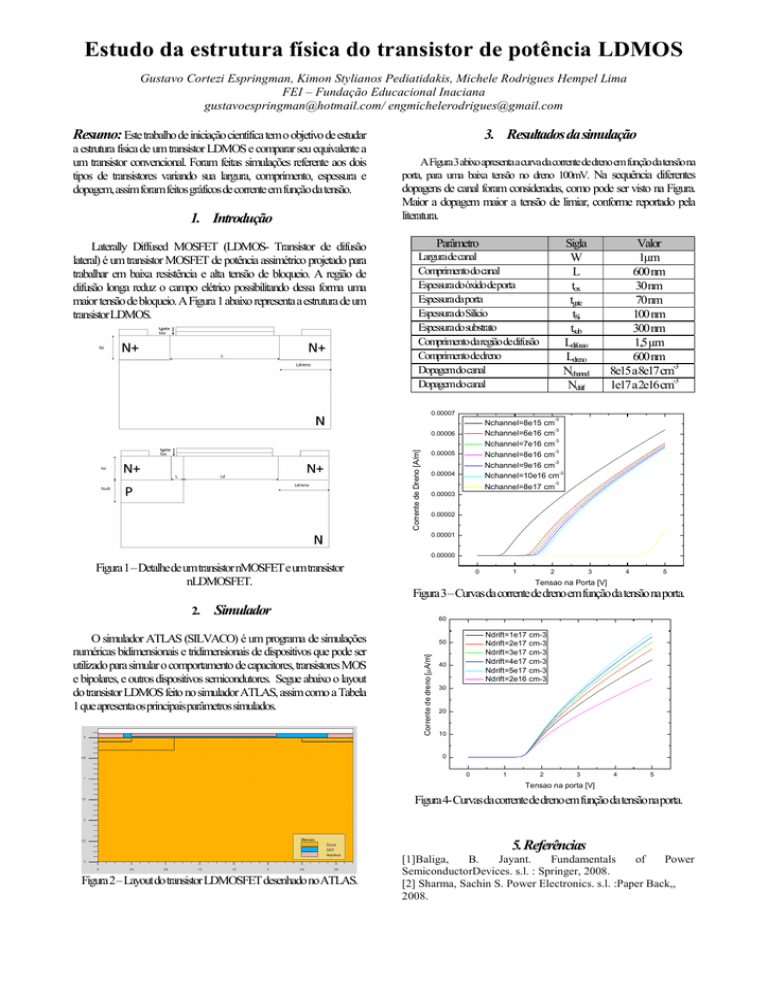

Laterally Diffused MOSFET (LDMOS- Transistor de difusão

lateral) é um transistor MOSFET de potência assimétrico projetado para

trabalhar em baixa resistência e alta tensão de bloqueio. A região de

difusão longa reduz o campo elétrico possibilitando dessa forma uma

maior tensão de bloqueio. A Figura 1 abaixo representa a estrutura de um

transistor LDMOS.

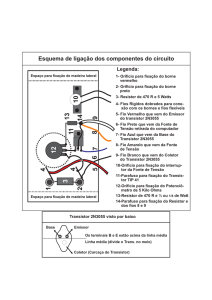

3. Resultados da simulação

A Figura 3 abixo apresenta a curva da corrente dedreno em função da tensão na

porta, para uma baixa tensão no dreno 100mV. Na sequência diferentes

dopagens de canal foram consideradas, como pode ser visto na Figura.

Maior a dopagem maior a tensão de limiar, conforme reportado pela

literatura.

Parâmetro

Sigla

W

L

tox

tgate

tSi

tsub

Ldifusao

Ldreno

Nchannel

Ndrift

Larguradecanal

Comprimento do canal

Espessuradoóxido deporta

Espessuradaporta

EspessuradoSilício

Espessurado substrato

Comprimento daregião dedifusão

Comprimento dedreno

Dopagemdocanal

Dopagemdocanal

Valor

1µm

600 nm

30 nm

70 nm

100 nm

300 nm

1,5 µm

600 nm

8e15 a 8e17 cm-3

1e17 a 2e16 cm-3

0.00007

-3

Nchannel=8e15 cm

-3

Nchannel=6e16 cm

-3

Nchannel=7e16 cm

-3

Nchannel=8e16 cm

-3

Nchannel=9e16 cm

-3

Nchannel=10e16 cm

-3

Nchannel=8e17 cm

Corrente de Dreno [A/m]

0.00006

0.00005

0.00004

0.00003

0.00002

0.00001

0.00000

Figura 1 – Detalhe de um transistor nMOSFET e um transistor

nLDMOSFET.

2

3

4

5

Figura 3 – Curvas da corrente de dreno em função da tensão na porta.

Simulador

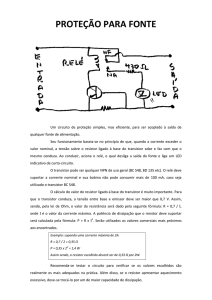

O simulador ATLAS (SILVACO) é um programa de simulações

numéricas bidimensionais e tridimensionais de dispositivos que pode ser

utilizado para simular o comportamento de capacitores, transistores MOS

e bipolares, e outros dispositivos semicondutores. Segue abaixo o layout

do transistor LDMOS feito no simulador ATLAS, assim como a Tabela

1 que apresenta os principais parâmetros simulados.

1

Tensao na Porta [V]

60

Ndrift=1e17 cm-3

Ndrift=2e17 cm-3

Ndrift=3e17 cm-3

Ndrift=4e17 cm-3

Ndrift=5e17 cm-3

Ndrift=2e16 cm-3

50

Corrente de dreno [A/m]

2.

0

40

30

20

10

0

0

1

2

3

4

5

Tensao na porta [V]

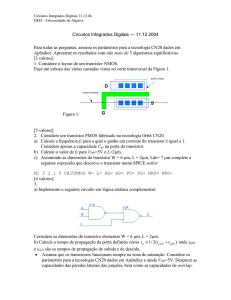

Figura 4- Curvas da corrente de dreno em função da tensão na porta.

5. Referências

Figura 2 – Layout do transistor LDMOSFET desenhado no ATLAS.

[1]Baliga,

B.

Jayant.

Fundamentals

of

Power

SemiconductorDevices. s.l. : Springer, 2008.

[2] Sharma, Sachin S. Power Electronics. s.l. :Paper Back,,

2008.