ÁREA:

CV ( )

CHSA ( )

ECET ( )

DESCRIÇÃO, VALIDAÇÃO E PROTOTIPAGEM DE BLOCO MÚLTI-NÚCLEOS

PARA PROJETO DE MICROPROCESSADORES MANY-CORE BASEADOS EM

REDES EM CHIP

Tiago dos Santo Patrocínio (Bolsista PIBIC/CNPq), Ivan Saraiva Silva (Orientador,

Departamento de Computação/UFPI)

Introdução

O projeto tem como finalidade o desenvolvimento de um subsistema de memória capaz de

trazer melhorias à arquitetura uVMP (UFPI’s Virtualizable Multicore Plataform)[6] trabalhada no

laboratório CESLa e registrada pelo NINTEC (Núcleo de Inovação e Transferência de Tecnologia).

Embora sejam apresentados siginificativos avanços nas arquiteturas de processadores e

memórias nos ultimos anos, ainda encontra-se barreiras. O subsistema é desenvolvido para substituir

o estado atual do componente presente na arquitetura, agregando avanços tecnológicos e resultando

em melhorias em relação ao desempenho do projeto. Para tanto, o projeto leva em consideração a

utilização de redes em chip, mais precisamente a rede SoCIN [1]. Ademais, tendo em vista problemas

relacionados a arquiteturas many-cores, recebem destaque os denominados Memory Wall [2] e

Power Wall [3], sendo proposto pelo projeto soluções que reduzam seus efeitos..

Metodologia

O projeto está sendo desenvolvido no Laboratório CESLa (Circuits and Embedded System

Laboratory) do Departamento de Computação da Universidade Federal do Piauí.

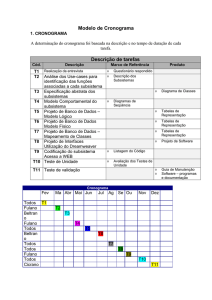

Até o presente momento, o cronograma está sendo seguido dentro do esperado. A

metodologia do plano de trabalho até dado momento consta em:

I.

Estudo das principais referencias bibliográficas do tema;

As referencias bibliográficas sobre o tema constam em artigos cientificos

de renomados autores da academia internacional

II. Estudo detalhado do modelo uVMP-SSC;

O modelo da arquitetura uVMP é obra dos integrantes do laboratório CESLa,

onde estão a disposição para auxiliar na estratégia e desenvolvimento do

trabalho.

III. Treinamento com as ferramentas;

As ferramentas à disposição são as placas de prototipagem DE0, DE2 e DE2-115

bem como os softwares Altera Quartus II e ModelSim, que em conjunto fornecem

o suficiente para a conclusão do plano de trabalho.

IV. Proposição da arquitetura do subsistema e da interface de rede;

A arquitetura do subsistema de memória leva em consideração o sistema de

redes em chip SoCIN. Além disso, visa reduzir ou solucionar problemas

relacionados à arquiteturas many-core.

V. Descrição do subsistema e da interface na linguagem VHDL de descrição de hardware;

Nesta etapa do desenvolvimento do trabalho, a arquitetura é descrita na

linguagem VHDL de descrição de hardware, viabilizando a prototipagem e

ÁREA:

CV ( )

CHSA ( )

ECET ( )

validação sobre as ferramentas disponíveis.

VI. Validação isolada;

É feita a validação do componente da memória de forma isolada, analisando seu

desempenho e integridade dos dados introduzidos.

VII. Validação integrada;

É feita a validação do componente da memória integrada ao modelo arquitetura

uVMP, analisando seu desempenho geral.

Arquitetura

O estudo das referências bibliográficas e do uVMP (UFPI’s Virtualizable Multicore Plataform)

forneceram a base necessária para a proposição de metas e técnicas de implementação do

subsistema de memória. A figura 1 apresenta o modelo utilizado nesse estudo.

Figura 2 – Esquema de configuração de núcleos escravos.

O uVMP propõem uma arquitetura multi-core com suporte a virtualização de recursos de

hardware, tornando possível a configuração do espaço endereçável. A arquitetura é composta por 1

núcleo mestre e 8 núcleos escravos, sendo que a função principal do mestre é de configurar e

agrupar núcleos escravos para desempenhar determinadas tarefas. A figura X apresenta o esquema

de configuração, composto por registradores que possuem a informação dos espaços endereçáveis e

quais núcleos serão ativados para desempenhar a função.

Figura 2 – Esquema de configuração de núcleos escravos.

O núcleo mestre é capaz de configurar os núcleos escravos de duas formas. A primeira é

agrupar os núcleos escravos SCi e SCi+4 (com 0 ≤ i ≤ 3) possibilitando o compartilhamento de

memória. A segunda forma é configurar os núcleos com espaços endereçáveis de memória privada,

permitindo troca de informações através de instruções definidas na arquitetura.

O subsistema de memória desenvolvido nesse estudo substitui o modelo antigo na arquitetura

ÁREA:

CV ( )

CHSA ( )

ECET ( )

uVMP, provendo ao núcleos escravos melhorias significativas no desempenho, reduzindo os efeitos

causados pelo problema conhecido como Memory Wall e Power Wall..

Resultados e Discussão

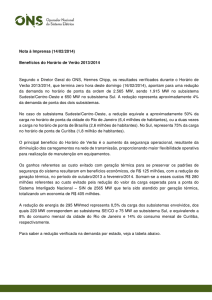

A implementação do subsistema de memória rendeu um aumento no desempenho geral da

arquitetura uVMP, contribuindo positivamente para a capacidade de processamento de aplicações em

paralelo. As tabelas apresentam resultado em ciclos das aplicações utilizadas na arquitura com a

implementação do subsistema de memória integrado. A aplicações utilizadas foram Multiplicação de

Matrizes e Merge Sort, ambas utilizando memória privada ou compartilhada.

Application

Execution Cycles

Comp. Cycles

Commu. Cycles

Matrix (S)

16053

26080

3074

Matrix (P)

11080

26736

10626

Matrix (SP)

11832

13469

9122

Merge sort (S)

3710

4364

963

Merge sort (P)

3942

4384

1488

Matrix/Merge

11832

31226

10706

Conclusão

As atividades desempenhadas durante o projeto junto ao apoio e suporte dos integrantes do

Laboratório CESLa (Circuits and Embedded System Laboratory) contribuiram positivamente para o

meu aprimoramento como discente. Acreditamos que as pesquisas desempenhadas e resultados

obtidos venham a ampliar a participação do Departamento de Computação na comunidade

acadêmica nacional e internacional, contribuindo, portanto, com avanços os tecnológicos para

industria e demais áreas relacionadas.

Referências

[1] ZEFERINO, c.a.; SUSIN, a.a., "SoCIN: A Parametric and Scalable Network-on-chip, "Integrated

Circuits and Systems Design, 2003. sbcci 2003. Proceedings. 16th Symposium on , vol., no.,

pp.169,174, 8-11 sept. 2003. doi: 10.1109/sbcci.2003.1232824.

[2] WULF, W. A. and MCKEE, S. A. Hitting the memory wall: Implications of the obvious. SIGARCH

Comput. Archit. News 23, 1 (march 1995), 20-24.6

[3] KURODA, T. Cmos design challenges to power wall. Microprocesses and Nanotechnology

Conference, 2001 International , VOL., NO., PP.6,7, OCT. 31 2001-NOV. 2 2001

[4] CHE, Z. Power-Efficient And Low-Latency Memory Access For Cmp Systems With Heterogeneous

Scratchpad On-Chip Memory. Master of science thesis. University of kentucky. College of engineering.

2013

[5] J. Hu, C. J. XUE, Q. ZHUGE, W.-C. TSENG, AND E. H.-M. SHA, “Towards Energy Efficient Hybrid

On-Chip Scratch Pad Memory With Non-Volatile Memory,” In Design, Automation & Test in Europe

Conference & Exhibition (DATE), 2011, PP. 1–6.

[6] SILVA, I. S.; NEPOMUCENO, R. MAFUTA, T. CARVALHO, E. S. Uvmp: Virtualizable Multi-core

Platform. XXXVIII Conferencia Latinoamericana en Informatica (CLEI), PP. 1 – 6, 2012.

[7] TOTA, S.V. ; CASU, M.R. ; RUO ROCH, M. ; ROSTAGNO, L. ; ZAMBONI, M. Medea: a hybrid

shared-memory/message-passing multiprocessor noc-based architecture. Design, automation & test

in europe conference & exhibition, PP. 45 – 50. March 2010.

Palavras-chave: Many-Core; Redes em Chip; MP-SoC.