CENTRO UNIVERSITÁRIO POSITIVO

NÚCLEO DE CIÊNCIAS EXATAS E TECNOLÓGICAS

ENGENHARIA DA COMPUTAÇÃO

PDA BASEADO NO MICROPROCESSADOR NIOS II COM

SISTEMA OPERACIONAL UCLINUX EMBARCADOS EM

FPGA

Roberto Sant’Ana Junqueira

Monografia apresentada à disciplina de Projeto Final como requisito parcial à conclusão

do Curso de Engenharia da Computação, orientada pelo Prof. Valfredo Pilla Jr.

UNICENP/NCET

Curitiba

2007

TERMO DE APROVAÇÃO

Roberto Sant’Ana Junqueira

PDA BASEADO NO MICROPROCESSADOR NIOS II COM SISTEMA OPERACIONAL

UCLINUX EMBARCADOS EM FPGA

Monografia aprovada como requisito parcial à conclusão do curso de Engenharia da Computação

do Centro Universitário Positivo, pela seguinte banca examinadora:

Prof. Valfredo Pilla Jr. (Orientador)

Prof. Edson Pedro Ferlin

Prof. Nestor Cortez Saavedra Filho

Curitiba, 15 de Dezembro de 2007.

AGRADECIMENTOS

Primeiramente, agradeço a Deus pela saúde, paz, e oportunidade de viver.

À minha família, principalmente aos meus pais Helio e Clelia, que me proporcionaram muitas

oportunidades na vida e que sempre lutaram junto a mim para que obstáculos fossem vencidos.

Ao meu grande amigo, orientador e professor Valfredo Pilla Jr., que sempre com sabedoria,

discernimento e muito apoio me ajudou no desenvolvimento deste projeto.

A todos os professores do Curso de Engenharia da Computação do UnicenP, que não apenas

compartilharam

conhecimentos,

mas

também

despertaram

em

mim

a

pesquisa

e

desenvolvimento sempre com qualidade e ética profissional.

A todos os meus amigos e colegas que de alguma forma direta e indireta, influenciaram e

ajudaram na minha formação acadêmica e na conclusão deste projeto.

RESUMO

Este trabalho descreve o desenvolvimento de um PDA (Personal Digital Assistant) baseado na

arquitetura do microprocessador NIOS II embarcado em FPGA juntamente com o Sistema

Operacional uClinux.

Palavras chave: PDA, FPGA, NIOS II, uClinux, Cyclone II

PDA BASED ON MICROPROCESSOR NIOS II WITH UCLINUX OPERATION

SYSTEM EMBEDDED IN FPGA

ABSTRACT

This text describes the development of a PDA (Personal Digital Assistant) based on the NIOS II

Microprocessor architecture embedded in FPGA together with the uClinux Operational System.

Key words: PDA, FPGA, NIOS II, uClinux, Cyclone II

SUMÁRIO

CAPÍTULO 1 - INTRODUÇÃO .................................................................................................. 11 1.1 – Objetivos ........................................................................................................................... 12 1.2 – Motivação ......................................................................................................................... 12 CAPÍTULO 2 – FUNDAMENTAÇÃO TEÓRICA ..................................................................... 13 2.1 – O Dispositivo FPGA ......................................................................................................... 13 2.2 – O Kit de Desenvolvimento DE2 ....................................................................................... 14 2.3 – O Processador NIOS II ..................................................................................................... 15 2.4 – O Sistema Operacional uClinux........................................................................................ 17 2.4.1 – A História do uClinux ........................................................................................... 17 2.4.2 – A Arquitetura do uClinux ...................................................................................... 17 CAPÍTULO 3 – ESPECIFICAÇÃO DO PROJETO .................................................................... 19 3.1 – Especificação do Software ................................................................................................ 19 3.2 – Especificação do Hardware............................................................................................... 19 3.2.1 – Arquitetura do Núcleo do Processador NIOS II .................................................... 19 3.2.2 – Memória Cache do Processador NIOS II .............................................................. 20 3.3 – Especificação da Validação do Software .......................................................................... 21 3.4 – Especificação da Validação do Hardware......................................................................... 21 3.5 – Recursos Necessários ........................................................................................................ 22 3.6 – Viabilidade Técnico-econômica ....................................................................................... 22 CAPÍTULO 4 – DESENVOLVIMENTO E IMPLEMENTAÇÃO ............................................. 23 4.1 – Os Módulos de Hardware Utilizados ................................................................................ 23 4.1.1 – Núcleo do Processador NIOS II (cpu_0) ............................................................... 23 4.1.2 – Interface de Acesso à Mem. Flash (tri_state_bridge_0 & cfi_flash_0) ................. 23 4.1.3 – Controlador da Memória SDRAM (sdram_0) ....................................................... 24 4.1.4 – Controlador da Memória Flash (epcs_controller) ................................................. 25 4.1.5 – Interface JTAG de Debug via Software (jtag_uart_0) .......................................... 25 4.1.6 – Controlador de Comunicação UART (uart_0) ...................................................... 26 4.1.7 – Temporizador 0 (timer_0) ..................................................................................... 26 4.1.8 – Temporizador 1 (timer_1) ..................................................................................... 27 4.1.9 – Pinos de Entrada Paralela (button_pio) ................................................................. 28 4.1.10 – Controlador da Memória SRAM (sram_0).......................................................... 29 4.1.11 – Controlador Ethernet (DM9000A) ...................................................................... 29 4.1.12 – Controlador USB (ISP1362)................................................................................ 29 4.1.13 – Controlador VGA (vga_controller_0) ................................................................. 29 4.1.14 – Controlador PS/2 (ps2_0) .................................................................................... 30 4.2 – O Projeto de Hardware no Quartus II ............................................................................... 30 4.2.1 – O Projeto no SOPC ................................................................................................ 30 4.2.2 – O Esquemático Final do Quartus II ....................................................................... 31 4.3 – O Kernel do uClinux ......................................................................................................... 33 4.3.1 – Compilando o Kernel do uClinux.......................................................................... 33 4.4 – Embarcando o Sistema ...................................................................................................... 37 CAPÍTULO 5 – VALIDAÇÃO E RESULTADOS ...................................................................... 39 CAPÍTULO 6 - CONCLUSÃO .................................................................................................... 44 CAPÍTULO 7 - REFERÊNCIAS BIBLIOGRÁFICAS ................................................................ 45 CAPÍTULO 8 – ANEXOS ............................................................................................................ 47 8.1 – Artigo Científico ............................................................................................................... 48 8.2 – Manual .............................................................................................................................. 49 LISTA DE FIGURAS

Fig. 2.1 – Estrutura Geral de uma FPGA. ..................................................................................... 13 Fig. 2.2 – Kit DE2 de Desenvolvimento. ...................................................................................... 14 Fig. 3.1 – Diagrama em Blocos do Hardware ............................................................................... 19 Fig. 3.2 – Núcleo do Processador NIOS II .................................................................................... 20 Fig. 3.3 – Memória Cache NIOS II ............................................................................................... 21 Fig. 4.1 – Configurações da Interface de Acesso à Memória Flash .............................................. 24 Fig. 4.2 – Configurações do Controlador de Memória SDRAM .................................................. 24 Fig. 4.3 – Configurações da Interface de Debug via Software ..................................................... 25 Fig. 4.4 – Configurações do Controlador de Comunicação UART .............................................. 26 Fig. 4.5 – Configurações do Temporizador 0................................................................................ 27 Fig. 4.6 – Configurações do Temporizador 1................................................................................ 28 Fig. 4.7 – Configurações dos Pinos de Entrada Paralela ............................................................... 28 Fig. 4.8 – Configurações do Controlador VGA ............................................................................ 30 Fig. 4.9 – Módulos de Hardware Integrados via SOPC ................................................................ 31 Fig. 4.10 – Projeto Completo no Modo de Esquemático do Quartus II ........................................ 32 Fig. 4.11 – Integrando arquivo de Descrição do Hardware ao Kernel do uClinux ....................... 33 Fig. 4.12 – Wizard de seleção de Hardware .................................................................................. 34 Fig. 4.13 – Sumário do Wizard de Configuração.......................................................................... 34 Fig. 4.14 – Execução do menuconfig ............................................................................................ 34 Fig. 4.15 – Interface Inicial do menuconfig .................................................................................. 35 Fig. 4.16 – Configurações do Kernel ............................................................................................ 35 Fig. 4.17 – Configuração das Aplicações do Kernel ..................................................................... 36 Fig. 4.18 – Construção do Sistema de Arquivos e Pastas ............................................................. 36 Fig. 4.19 – Linha de Comando para compilação do Kernel .......................................................... 37 Fig. 4.20 – Criando a Imagem do Kernel ...................................................................................... 37 Fig. 5.1 – uClinux sendo inicializado via Terminal USB ............................................................. 39 Fig. 5.2 – Sistema Operacional reconhecendo Pendrive automaticamente................................... 40 Fig. 5.3 – Sistema sendo acessado via FTP................................................................................... 40 Fig. 5.4 – Sistema sendo acessado via navegador de internet ....................................................... 41 Fig. 5.5 – Sistema sendo executado em modo gráfico .................................................................. 41 Fig. 5.6 – Sistema executando aplicativo de relógio ..................................................................... 42 Fig. 5.7 – Sistema executando jogo nTetris .................................................................................. 42 Fig. 5.8 – Sistema executando aplicativo de visualização de imagens ......................................... 43 LISTA DE TABELAS

TABELA 2.1 – Tipos de Núcleo do Processador NIOS II ........................................................... 16

TABELA 3.1 – Relação de custos dos recursos utilizados ........................................................... 22

LISTA DE SIGLAS

NCET- Núcleo de Ciências Exatas e Tecnológicas

UNICENP – Centro Universitário Positivo

PDA – Personal Digital Assistant

ASIC – Application Specific Integrated Circuit

FPGA – Field Programmable Gate Array

JPEG – Joint Photographic Experts Group

USB – Universal Serial Bus

CPLD – Complex Programmable Logic Device

RAM – Random Access Memory

SRAM – Static Random Access Memory

SDRAM – Synchronous Dynamic Random Access Memory

SD Card – Security Digital Card

LED – Light-Emitting Diode

CODEC – Coder-Decoder

VGA – Video Graphics Array

DAC – Digital-to-Analog Converter

IrDA – Infrared Data Association

RISC – Reduced Instruction Set Computer

DMIPS – Dhrystone Million Instructions Per Second

CPU – Central Processing Unit

ULA – Unidade Lógica e Aritmética

MMU – Memory Management Unit

SCADA – Supervisory Control and Data Acquisition

TCP/IP – Transmission Control Protocol / Internet Protocol

GPL – General Public License

IRQ – Interrupt Request

SOPC – System On a Programmable Chip

PLL – Phase-Locked Loop

FTP – File Transfer Protocol

CAPÍTULO 1 - INTRODUÇÃO

Há essencialmente dois enfoques para a execução de programas em hardware: a construção de

um circuito específico, por exemplo, um ASIC (Application Specific Integrated Circuit), ou

então o uso de microprocessadores programados por software. Nestes dois extremos, há

vantagens e desvantagens. Um ASIC, por ter hardware projetado especificamente para a

execução do programa (ou então blocos funcionais montados de forma específica), é

extremamente rápido para executar o programa. Por outro lado, como não é possível modificá-lo

após a fabricação do circuito, qualquer mudança que seja necessária implica reprojeto e

refabricação do chip. Além disso, caso haja a refabricação do circuito, ele precisará ser

substituído em todos os sistemas em que tenha sido implantado (DEVEGILI et al., 2004).

No outro extremo estão os microprocessadores programados por software. Nestes, há um

conjunto de instruções e o programa a ser executado é especificado em termos destas instruções.

Caso o programa precise ser alterado, basta que sejam modificadas as instruções sem que seja

necessário alterar o microprocessador. Entretanto, devido ao processo de carga e decodificação

das instruções, aliado à genericidade do projeto do circuito, o desempenho de um

microprocessador, sob o ponto de vista de tempo de execução, é mais lento do que de um ASIC.

Ademais, um programa está limitado às instruções definidas pelo microprocessador, não sendo

possível alterá-las ou incluir novas instruções (DEVEGILI et al., 2004).

A computação reconfigurável é um meio termo entre estes dois extremos, buscando conciliar a

rapidez de execução de soluções em hardware específico e a flexibilidade dos

microprocessadores. Para isto, são utilizados dispositivos programáveis, notadamente FPGAs

(Field Programmable Gate Array). Nestes dispositivos, há um conjunto de blocos lógicos e uma

rede de interconexão, ambos programáveis. Desta forma, um circuito pode ser especificado e

sintetizado em um dispositivo programável, acarretando um tempo de execução mais rápido do

que uma solução baseada em microprocessador. Por outro lado, com dispositivos programáveis

que sejam reconfiguráveis, é possível implementar mudanças no projeto do circuito sem que seja

necessária a remanufatura física do circuito (DEVEGILI et al., 2004).

Existem vários soluções de projetos baseadas em computação reconfigurável, uma das

possibilidades é a síntese de um microprocessador em um dispositivo reconfigurável. Este é o

caso do microprocessador NIOS II, utilizado como arquitetura neste trabalho (DEVEGILI et al.,

2004).

11

1.1 – Objetivos

O objetivo principal deste trabalho é desenvolver um PDA utilizando FPGA com o

microprocessador NIOS II e o Sistema Operacional uClinux embarcados. Este PDA contém

alguns aplicativos (editor de texto, visualizador de imagens JPEG, jogo de raciocínio, etc.), que

podem ser acessados pela interface de teclado e visualizados na interface de vídeo; é possível

armazenar e ler dados em discos de memória FLASH (Pendrives, etc.) através da interface USB.

1.2 – Motivação

Nos dias atuais a utilização de Microcomputadores, Laptops e PDAs se faz presente e necessária

para quaisquer que sejam as necessidades, sendo elas, trabalho, estudo ou entretenimento.

Com a evolução dos sistemas embarcados, os PDAs veem se destacando cada vez mais no

mundo da informação, pois possuem grande poder de processamento e armazenamento, além de

interfaces de comunicação variadas, por exemplo, infra-vermelho, wireless, bluetooh e USB, e

também leitores de cartões multimídia. Apesar de estarem cada vez mais difundidos, os PDAs

ainda possuem um custo elevado, pois a tecnologia empregada no desenvolviento destes

“pequenos gigantes” ainda tem um custo elevado, pois são criadas arquiteturas dedicadas para os

mesmos.

A grande motivação deste trabalho de desenvolver um PDA utilizando NIOS II como

microprocessador embarcado em FPGA rodando o Sistema Operacional uClinux, é o fato de

poder estudar o funcionamento de arquiteturas embarcadas em FPGAs integradas com sistemas

operacionais de código-fonte aberto, e fazer com que este sistema operacional controle os

dispositivos que estão acoplados ao sistema.

12

CAPÍTULO 2 – FUNDAMENTAÇÃO TEÓRICA

2.1 – O Dispositivo FPGA

Uma FPGA é mais flexível que uma CPLD (Complex Programmable Logic Device), pois

permite a implementação de muitas lógicas complexas, e pode ser utilizada para a

implementação de circuitos lógicos digitais que se equivalem a milhões de Portas Lógicas

(NAVABI, 2007).

Uma FPGA possui muitos blocos lógicos pequenos ligados por canais de conexão, cada um

destes blocos lógicos consiste em um elemento lógico muito pequeno. Cada elemento lógico

possui apenas um flip-flop que é configurado e controlado individualmente. A complexidade

lógica de cada elemento lógico contém de 10 à 20 portas lógicas (NAVABI, 2007).

Outro recurso adicional na estrutura da FPGA são os blocos de memória que podem ser

configurados como memória RAM (Random Access Memory) (NAVABI, 2007).

Fig. 2.1 – Estrutura Geral de uma FPGA.

FONTE: Adaptada de LIMA (1999).

Como mostra a Fig. 2.1, uma FPGA é um arranjo de muitos blocos lógicos interligados por meio

de canais de conexão horizontal e vertical. Os blocos do tipo RAM podem também ser utilizados

13

para implementação lógica ou podem ser configurados para formar bancos de memória de

tamanhos variados (NAVABI, 2007).

2.2 – O Kit de Desenvolvimento DE2

O Kit de Desenvolvimento DE2 da Altera, Figura 2.2, possui características que permitem a

criação e implementação de uma vasta gama de aplicações, desde simples circuitos indo até

projetos complexos multimídia.

Fig. 2.2 – Kit DE2 de Desenvolvimento.

FONTE: ALTERA (2007).

A placa do Kit de Desenvolvimento é composta pelos seguintes componentes (ALTERA, 2007):

•

Altera Cyclone II EP2C35F672C6 FPGA

•

Altera EPCS16 – Dispositivo de configuração Serial

•

USB Blaster para programação

•

512 Kbytes SRAM (Static Random Access Memory)

•

8 Mbytes SDRAM (Synchronous Dynamic Random Access Memory)

•

4 Mbytes Flash Memory

•

Soquete para SD Card

•

Botões

•

Interruptores

•

LEDs (Light-Emitting Diode) vermelhos

•

LEDs verdes

•

Osciladores de 50 MHz, 27 MHz e conector para oscilador externo

•

CODEC (Coder-Decoder) de Áudio de 24 bits

14

•

VGA (Video Graphics Array) DAC (Digital-to-Analog Converter) de 10 bits

•

TV Decoder (NTSC/PAL)

•

Controlador Ethernet 10/100

•

Controlador USB com conectores do Tipo A e do Tipo B

•

Transceiver RS-232

•

Transceiver IrDA (Infrared Data Association)

•

Conector PS/2

•

Dois barramentos expansores de 40 pinos com proteção de Diodos

2.3 – O Processador NIOS II

O processador Nios II é um processador RISC (Reduced Instruction Set Computer) que

possui conjunto de instruções, caminho de dados e espaço de endereçamento todos com tamanho

de 32 bits, 32 registradores de propósito geral, 5 registradores de controle, 32 fontes externas de

interrupção, módulo de depuração auxiliado por hardware e suporte para acessar dispositivos de

E/S além de chips de memória (ALTERA, 2007).

A arquitetura do processador é do tipo load/store e possui a ordenação dos bits de forma little

endian. A frequência de clock depende muito das características personalizadas pelo projetista e

podem variar de 165 à 200 MHz, obtendo uma performance de até 250 DMIPS (Dhrystone

Million Instructions per Second) (ALTERA, 2007).

Os modos de endereçamento suportados pela arquitetura do NIOS II são (ALTERA, 2007):

•

Endereçamento por registrador: o endereço encontra-se em um registrador;

•

Endereçamento por deslocamento: o endereço é calculado com a soma do conteúdo do

registrador com um valor de 16 bits com sinal positivo ou negativo;

•

Endereçamento imediato: o endereço é passado diretamente na instrução;

•

Endereçamento indireto por registrador: o endereço esta na memória apontada pelo

conteúdo do registrador.

•

Endereçamento absoluto: utiliza endereçamento por deslocamento com o registrador

“r0”, no qual o valor é sempre 0x00.

15

Uma das características que diferenciam o NIOS II da maioria dos processadores para sistemas

embarcados é o fato de ele ser um processador com núcleo controlado por software e

configurável, o que permite que características sejam adicionadas ou removidas do processador.

Como o processador tem esta característica de ser configurável, é possível que um sistema

embarcado que o utilize tenha os seguintes componentes personalizados pelo projetista

(ALTERA, 2007):

•

Periféricos padrões: temporizadores, interface de comunicação serial, pinos de E/S,

controladores de memória SDRAM, e interfaces para outras memórias;

•

Periféricos personalizados: para realizar alguma função específica de código que

consome a maioria dos ciclos da CPU (Central Processing Unit) ;

•

Mapa de endereços: da mesma forma que é possível criar controladores de memórias ou

periféricos personalizados, o mapa de endereços também precisa ser configurável de

modo que se possa endereçar corretamente todos os dispositivos;

•

Instruções personalizadas: permite a adição de instruções na ULA (Unidade lógica e

aritmética).

Mesmo sendo possível personalizar todos os componentes referenciados acima, a Altera já

disponibiliza algumas “versões” do NIOS II , como mostra a Tabela 2.1, a fim de facilitar o

trabalho dos projetistas: o Nios II/e, voltado para projetos em que o tamanho do núcleo deve ser

o menor possível e a velocidade de execução de instruções não é um aspecto crítico; o Nios II/f,

que tem por objetivo acelerar a execução das instruções independentemente do aumento que

pode acarretar no tamanho do núcleo do processador; e o Nios II/s, que busca equilibrar o

tamanho do núcleo do processador com a velocidade de execução das instruções, sendo um meio

termo entre os dois anteriores (DEVEGILI et al., 2004).

TABELA 2.1 – Tipos de Núcleo do Processador NIOS II

FONTE: Adaptada de ALTERA (2007).

16

2.4 – O Sistema Operacional uClinux

O Sistema Operacional uClinux ou “micro-controlador Linux” é a variante mais popular da

tendência dominante Linux, especialmente desenvolvido para microprocessadores sem MMU

(Memory Management Unit). A falta de MMU é um fator muito comum em microprocessadores

de baixo custo, em que o preço dos componentes é crucial. O Sistema Operacional uClinux é

totalmente livre de royalties e é uma solução de código-fonte aberto (NIKKANEN, 2003).

2.4.1 – A História do uClinux

O projeto uClinux iniciou-se em 1997, com a meta de criar-se uma versão derivado do Linux

Kernel 2.0 para microcontroladores de baixo custo. Foram Jeff Dione e Kenneth Albanowski

juntamente com um grupo de desenvolvedores, que vislumbraram sobre a possibilidade de

embarcar o Sistema Operacional Linux em controladores de rede sem MMU, para que se

pudesse manipular a comunicação entre a Rede e o Sistema de Comunicação. A primeira versão

do pequeno Sistema Operacional foi criada para o processador Motorola 68000, no qual era

baseado no microprocessador MC68328 Dragonball que era utilizado como controlador SCADA

(Supervisory Control and Data Acquisition) em 1997/98. A primeira versão pública da

comunidade open-source foi liberada como um Sistema Operacional alternativo para Palm Pilot

em fevereiro de 1998 (NIKKANEN, 2003).

2.4.2 – A Arquitetura do uClinux

O Sistema Operacional uClinux é o mais popular para sistemas embarcados. O seu Kernel

suporta diferentes plataformas de CPU, incluindo ColdFire, Axix ETRAX, ARM, Atari 68k,

NIOS e muitos outros. Ele tem crescido exponencialmente com cada vez mais e mais

microprocessadores sem MMU recebendo seus próprios ports. A diferença principal se

comparado com o Linux é a falta de MMU e o fato de ser desenvolvido para soluções muito

compactas. Da mesma forma que o Linux, uClinux tem um forte suporte a redes incluindo uma

completa Stack TCP/IP (Transmission Control Protocol / Internet Protocol) e suporte a uma

grande variedade de protocolos de rede. Ele também tem suporte a vários diferentes sistemas de

17

arquivos, incluindo alguns destinados para aplicações embarcadas. Tenta-se manter a

compatibilidade do uClinux com Linux o máximo possível. Isto significa que diferentes

aplicações desenvolvidas sobre a GPL (General Public License) devem também estar adaptadas

para suportar versões Linux sem MMU, usualmente isto requer pequenas mudanças. Isto

logicamente esta limitado fisicamente pelo hardware do sistema embarcado, devido a carência de

compatibilidade de alguns periféricos (NIKKANEN, 2003).

18

CAPÍTULO 3 – ESPECIFICAÇÃO DO PROJETO

3.1 – Especificação do Software

O software deste projeto é a imagem do Kernel do uClinux que deve ser customizado e

compilado para total compatibilidade com o Hardware embarcado na FPGA.

3.2 – Especificação do Hardware

A Figura 3.1 apresenta uma visão geral do hardware do sistema em forma de diagrama em

blocos, demonstrando como as interfaces de conexão e memórias externas estão conectadas à

FPGA.

Fig. 3.1 – Diagrama em Blocos do Hardware

3.2.1 – Arquitetura do Núcleo do Processador NIOS II

Na Figura 3.2 é apresentada a estrurura interna do Núcleo do Processador NIOS II em forma de

diagrama em blocos. É importante salientar que, como o NIOS II é um processador configurável

19

pelo projetista, os componentes básicos mostrados na Fig. 3.2 não são necessariamente

implementados via hardware, podendo ser emulados via software ou simplesmente omitidos,

desde que a configuração final permita a execução do conjunto de instruções do NIOS II

(DEVEGILI et al., 2004).

Fig. 3.2 – Núcleo do Processador NIOS II

FONTE: DEVEGILI et al. (2004)

3.2.2 – Memória Cache do Processador NIOS II

Como pode ser visto na Figura 3.3, a arquitetura do Processador NIOS II suporta que memórias

cache, implementadas dentro do núcleo do processador, sejam ligadas nas portas mestre de dados

e de instruções, melhorando assim o tempo de acesso médio às memórias. Assim como os outros

componentes básicos, as memórias cache são configuráveis pelo projetista.

20

Fig. 3.3 – Memória Cache NIOS II

FONTE: DEVEGILI et al. (2004)

3.3 – Especificação da Validação do Software

A validação do software se faz pela perfeita integração dos elementos criados em linguagem de

descrição de hardware com o Kit de Desenvolvimento DE2, além de que o Kernel gerado deve

conseguir acessar os dispositivos de hardware.

3.4 – Especificação da Validação do Hardware

A validação do hardware se faz pelo sucesso na compilação do projeto do Quartus II e pelo total

funcionamento das Memórias, interface de Rede, interface PS/2 e interface de vídeo.

A validação do hardware esta totalmente atrelada à validação do software, sendo que só é

possível validar o hardware através de acessos via o Sistema Operacional uClinux.

21

3.5 – Recursos Necessários

Software:

•

Altera Quartus II Subscription Versão 6.1

•

Alterar Nios II Embedded Design Suite Versão 6.1

•

Altera MegaCore IP

•

Distribuição Linux CentOS-5

Hardware:

•

Kit Altera DE2 NIOS

•

Monitor 17” SVGA

•

Teclado alfa-numérico PS/2

•

Pendrive de 512 Mbytes

3.6 – Viabilidade Técnico-econômica

Para desenvolvimento do projeto, os principais recursos foram disponibilizados pelo Curso de

Engenharia da Computação. Porém visando contabilizar o custo total do projeto, todos os

recursos utilizados foram listados na Tabela 3.1, sem levar em consideração ferramentas de

desenvolvimento como o microcomputador e os softwares envolvidos. Considerou-se também o

tempo de trabalho no desenvolvimento do projeto, desde a fase de pesquisa até a documentação

final.

TABELA 3.1 – Relação de custos dos recursos utilizados

22

CAPÍTULO 4 – DESENVOLVIMENTO E IMPLEMENTAÇÃO

A implementação deste projeto tem como objetivo criar um sistema capaz de executar a

distribuição linux uClinux e alguns aplicativos que devem conter na imagem do Kernel gerado,

isto é feito através da integração de blocos de descrição de hardware e ajuste dos mesmos.

Entende-se por ajustes a definição das configurações além de números de interrupções e

endereços de acesso base e final de cada módulo.

4.1 – Os Módulos de Hardware Utilizados

4.1.1 – Núcleo do Processador NIOS II (cpu_0)

O Núcleo utilizado neste projeto é do Tipo Nios II/f e está configurado da seguinte forma:

•

Memória de Cache de Instruções de 4 Kbytes

•

Memória de Cache de Dados de 2 Kbytes com tamanho de 4 bytes cada linha de dados

•

Clock de entrada de 100 MHz (atingindo até 101 DMIPS)

•

Módulo de depuração JTAG Nível 1

•

Endereço de interrupções base: IRQ (Interrupt Request) 0

•

Endereço de interrupções final: IRQ 31

•

Módulo de depuração com Endereço base: 0x00680000

•

Módulo de depuração com Endereço final: 0x006807FF

4.1.2 – Interface de Acesso à Mem. Flash (tri_state_bridge_0 & cfi_flash_0)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00000000

•

Endereço final: 0x003FFFFF

A Fig. 4.1 apresenta as configurações utilizadas para a interface de acesso à memória Flash.

23

Fig. 4.1 – Configurações da Interface de Acesso à Memória Flash

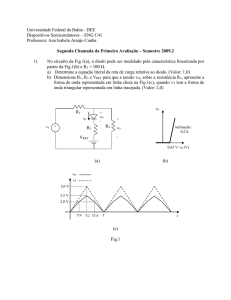

4.1.3 – Controlador da Memória SDRAM (sdram_0)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00800000

•

Endereço final: 0x00FFFFFF

A Fig. 4.2 apresenta as configurações utilizadas para o módulo de controle da memória SDRAM.

Fig. 4.2 – Configurações do Controlador de Memória SDRAM

24

4.1.4 – Controlador da Memória Flash (epcs_controller)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00680800

•

Endereço final: 0x00680FFF

•

IRQ 0

4.1.5 – Interface JTAG de Debug via Software (jtag_uart_0)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x006810F0

•

Endereço final: 0x006810F7

•

IRQ 1

A Fig. 4.3 apresenta as configurações utilizadas para a Interface de Debug via Software.

Fig. 4.3 – Configurações da Interface de Debug via Software

25

4.1.6 – Controlador de Comunicação UART (uart_0)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00681000

•

Endereço final: 0x0068101F

•

IRQ 2

A Fig. 4.4 apresenta as configurações utilizadas para o Controlador de Comunicação UART.

Fig. 4.4 – Configurações do Controlador de Comunicação UART

4.1.7 – Temporizador 0 (timer_0)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00681020

•

Endereço final: 0x0068103F

•

IRQ 3

26

A Fig. 4.5 apresenta as configurações utilizadas para o Temporizador 0.

Fig. 4.5 – Configurações do Temporizador 0

4.1.8 – Temporizador 1 (timer_1)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00681040

•

Endereço final: 0x0068105F

•

IRQ 4

A Fig. 4.6 apresenta as configurações utilizadas para o Temporizador 1.

27

Fig. 4.6 – Configurações do Temporizador 1

4.1.9 – Pinos de Entrada Paralela (button_pio)

Este módulo é parte integrante do software Quartus II 6.1 e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00681090

•

Endereço final: 0x0068109F

•

IRQ 5

A Fig. 4.7 apresenta as configurações utilizadas para os Pinos de Entrada Paralela.

Fig. 4.7 – Configurações dos Pinos de Entrada Paralela

28

4.1.10 – Controlador da Memória SRAM (sram_0)

Este módulo é parte integrante do CD de instalação do Kit DE2 da Altera, e está customizado da

seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00600000

•

Endereço final: 0x0067FFFF

4.1.11 – Controlador Ethernet (DM9000A)

Este módulo é parte integrante do CD de instalação do Kit DE2 da Altera, e está customizado da

seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x006810F8

•

Endereço final: 0x006810FF

•

IRQ 6

4.1.12 – Controlador USB (ISP1362)

Este módulo é parte integrante do CD de instalação do Kit DE2 da Altera, e está customizado da

seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x006810B0

•

Endereço final: 0x006810BF

•

IRQ 7 & IRQ 8

4.1.13 – Controlador VGA (vga_controller_0)

Este módulo é parte integrante do kit de desenvolvimento Lancelot da Microtronix, está

adaptado para funcionar com o kit DE2 da Altera, e está customizado da seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00682000

•

Endereço final: 0x0068200F

A Fig. 4.8 apresenta as configurações utilizadas para o Controlador de Vídeo.

29

Fig. 4.8 – Configurações do Controlador VGA

4.1.14 – Controlador PS/2 (ps2_0)

Este módulo é parte integrante do CD de instalação do Kit DE2 da Altera, e está customizado da

seguinte forma:

•

Clock de entrada de 100 MHz

•

Endereço base: 0x00682010

•

Endereço final: 0x00682017

•

IRQ 9

4.2 – O Projeto de Hardware no Quartus II

4.2.1 – O Projeto no SOPC

Todos os módulos apresentados anteriormente foram configurados e integrados ao projeto

utilizando-se a ferramenta do Quartus II chamada SOPC (System On a Programmable Chip). A

Fig. 4.9 apresenta como ficou o projeto após a integração de todos estes módulos.

30

Fig. 4.9 – Módulos de Hardware Integrados via SOPC

4.2.2 – O Esquemático Final do Quartus II

Para conclusão do Projeto de Hardware no Quartus II foi necessária a criação de módulos

auxiliares

como:

PLLs

(Phase-Locked

Loop)

para

serem

utilizadas

como

divisores/multiplicadores de clock; circuito de Reset para poder haver a reinicialização do

sistema; além de um circuito de configuração e inicialização de alguns pinos de interface.

Depois de finalizado os testes foram adicionados ao projeto o restante dos componentes que

compõe o Kit de Desenvolvimento Altera DE2, com o único objetivo de que associados seus

pinos com a FPGA todos que não estivessem sendo utilizados seriam configurados por segurança

para modo Tri-State.

A Fig. 4.10 apresenta como ficou o Esquemático final do Projeto no Quartus II com a integração

dos módulos criados via SOPC e os módulos criados diretamente no Quartus.

31

Fig. 4.10 – Projeto Completo no Modo de Esquemático do Quartus II

32

4.3 – O Kernel do uClinux

Inicialmente deve-se instalar a distribuição do Kernel do uClinux em algum Sistema Operacional

Linux. O Sistema Operacional utilizado para compilar o Kernel do uClinux é o CentOS versão 5.

O CentOS é uma distribuição Linux baseada nos códigos-fonte da Red Hat Enterprise Linux e é

mantido pelo projeto “CentOS Project”.

A distribuição do uClinux utilizada é a “uClinux-dist-20070130”. Esta distribuição contém o

pacote completo do código-fonte do uClinux, juntamente com o Kernel (versões: 2.0.39, 2.4.32 e

2.6.19), as bibliotecas e o código-fonte das aplicações compatíves com o mesmo.

4.3.1 – Compilando o Kernel do uClinux

O primeiro passo é configurar qual é a arquitetura de Hardware que compõe o Projeto. Isto é

feito através do arquivo gerado pelo Quartus II que contém a extensão “.ptf”. Neste projeto o

nome o arquivo é “HardwareNiosII.ptf”, este arquivo contém a descrição completa do sistema de

hardware criado no SOPC, isto inclui configurações e parâmetros personalizados. A Fig. 4.11

apresenta como integrar este arquivo de descrição de hardware ao kernel do uClinux.

Fig. 4.11 – Integrando arquivo de Descrição do Hardware ao Kernel do uClinux

A execução da linha de comando mostrada na Fig. 4.11 faz com que um pequeno wizard de

seleção de hardware seja iniciado. Como mostra a Fig. 4.12 este pequeno wizard é composto por

três passos, onde no primeiro é solicitada a seleção do processador que deve ser utilizado na

compilação do kernel, como o projeto contém apenas um processador NIOS II, apenas o mesmo

é listado e deve ser selecionado; o segundo passo lista todos os dispositivos disponíveis no

projeto com o qual pode-se armazenar a imagem do kernel do uClinux, como o projeto contém

apenas uma memória Flash, apenas a mesma é listada e deve ser selecionada; e o terceiro passo

lista todos os controladores de memórias disponíveis no projeto com o qual pode-se executar o

kernel do uClinux, como o projeto contém 3 tipos de memórias, todas os três controladores são

listados, mas deve-se selecionar o Controlado da Memória SDRAM.

33

Fig. 4.12 – Wizard de seleção de Hardware

A Fig. 4.13 apresenta um sumário com as configurações realizadas no wizard anterior.

Fig. 4.13 – Sumário do Wizard de Configuração

O próximo passo é a execução da linha de comando: “make menuconfig”, como mostra a Fig.

4.14, esta linha de comando executará o wizard de configurações das opções do kernel, com as

quais podemos ou não personalizar.

Fig. 4.14 – Execução do menuconfig

A Fig. 4.15 apresenta a interface inicial do “menuconfig”, aonde se deve selecionar:

34

•

Versão kernel que se deseja utilizar (2.6.19 neste projeto)

•

Versão da Biblioteca libc que se deseja utilizar

•

Opções que se deseja configurar e customizar

Fig. 4.15 – Interface Inicial do menuconfig

A Fig. 4.16 apresenta a interface de configuração do kernel, aonde se pode configurar os device

drivers, tipos de sistemas de arquivos, interfaces de rede, características do processador, opções

de criptografia, entre outros.

Fig. 4.16 – Configurações do Kernel

35

A Fig. 4.17 apresenta a interface de configuração das aplicações que acompanharão o kernel,

sejam elas aplicações padrão ou customizadas.

Fig. 4.17 – Configuração das Aplicações do Kernel

O próximo passo é executar a construção do sistema de arquivos e pastas do kernel através da

linha de comando: “make romfs”. A Fig. 4.18 apresenta como isto deve ser feito.

Fig. 4.18 – Construção do Sistema de Arquivos e Pastas

Executados todos os passos anteriores o kernel esta apto à ser compilado por inteiro. Através da

linha de comando: “make”, como mostra a Fig. 4.19, todos os módulos que foram selecionados e

36

configurados anteriormente serão compilados. Este processo leva entre 5 a 7 minutos para ser

finalizado.

Fig. 4.19 – Linha de Comando para compilação do Kernel

Após a compilação completa do kernel do uClinux, deve-se finalmente gerar a imagem do

Kernel, esta é a imagem que será copiada para memória Flash do sistema e será descompactada e

executada na memória SDRAM, para gerarmos esta imagem devemos executar a linha de

comando: “make linux image”, como mostra a Fig. 4.20. A Imagem gerada possui o nome

“zImage” e seu tamanho pode variar de acordo com os device drivers e aplicativos que foram

integrados e customizados no Kernel.

Fig. 4.20 – Criando a Imagem do Kernel

4.4 – Embarcando o Sistema

Para embarcar tanto a arquitetura de hardware na FPGA (HardwareFPGA.sof) como o imagem

do Kernel do uClinux (zImage) geradas, foi utilizado o software “Nios II 6.1 Command Shell”.

Primeiramente deve-se converter o arquivo HardwareFPGA.sof para que ele possa ser

armazenado na memória flash e posteriormente gravado na FPGA.

A linha de comando para esta conversão é: sof2flash --epcs --input=HardwareFPGA.sof -output=HardwareFPGA.flash

37

Depois de gerado o arquivo HardwareFPGA.flash deve-se envia-lo para o Controlador de

Memória Flash, pois este será o encarregado de gravar o sistema de hardware na FPGA.

A linha de comando para esta gravação é: nios2-flash-programmer --epcs --base=0x00680800

HardwareFPGA.flash

Podemos perceber que o endereço utilizado como base é o endereço do controlador de Memória

Flash.

O próximo passo é converter a imagem do Kernel em arquivo .flash para que o mesmo fique

armazenado na memória flash.

A linha de comando para esta conversão é: elf2flash --base=0x00000000 --end=0x003FFFFF -reset=0x00000000 --input=zImage --output=uclinux.flash

--boot= $SOPC_KIT_NIOS2/components/altera_nios2/boot_loader_cfi.srec

Podemos perceber que os endereços utilizados como base e final são os endereços de acesso à

Memória Flash.

E, por fim, o último passo é gravar a imagem já convertida na Memória Flash.

A linha de comando para esta gravação é: nios2-flash-programmer --base=0x00000000 ext_

uclinux.flash

38

CAPÍTULO 5 – VALIDAÇÃO E RESULTADOS

Os resultados finais do projeto foram totalmente satisfatórios, tendo em vista que todas as

funcionalidades propostas originalmente foram alcançadas com sucesso, além de outras

características que não constavam na proposta original, mas que também obtiveram sucesso de

funcionamento. A Fig. 5.1 demonstra o Sistema Operacional uClinux sendo inicializado via

terminal de acesso USB.

Fig. 5.1 – uClinux sendo inicializado via Terminal USB

39

A Fig. 5.2 apresenta o Sistema Operacional uClinux reconhecendo automaticamente o pendrive

da Kingston de 512 Mbytes, no momento exato em que ele é conectado na porta USB do Kit

DE2 da Altera.

Fig. 5.2 – Sistema Operacional reconhecendo Pendrive automaticamente

A Fig. 5.3 apresenta o sistema sendo acessado via FTP (File Transfer Protocol) por outro

computador da rede.

Fig. 5.3 – Sistema sendo acessado via FTP

A Fig. 5.4 apresenta o sistema sendo acessado via navegador de internet.

40

Fig. 5.4 – Sistema sendo acessado via navegador de internet

A Fig. 5.5 apresenta o Sistema Operacional uClinux sendo executado no modo gráfico.

Fig. 5.5 – Sistema sendo executado em modo gráfico

41

A Fig. 5.6 apresenta o sistema executando um aplicativo de relógio.

Fig. 5.6 – Sistema executando aplicativo de relógio

A Fig. 5.7 apresenta o sistema executando o jogo nTetris.

Fig. 5.7 – Sistema executando jogo nTetris

42

A Fig. 5.8 apresenta o sistema executando um aplicativo de visualização de imagens.

Fig. 5.8 – Sistema executando aplicativo de visualização de imagens

43

CAPÍTULO 6 - CONCLUSÃO

O sistema se mostrou bastante eficiente e com bom desempenho (percepção humana) se

comparado a PDAs existentes no mercado (Palm, Pocket, etc.), mas devido a uma Memória

Flash de tamanho pequeno a imagem do Kernel fica limitada, não permitindo adicionar maiores

recursos e aplicativos, além de que, como o Processador NIOS II não possui MMU, e a Memória

SDRAM possui um tamanho pequeno, foi identificado que a execução de alguns aplicativos ao

mesmo tempo pode ocasionar invasão de área de Memória causando o travamento do sistema e

obrigando que o mesmo seja reiniciado.

A utilização apesar de fácil é mais intuitiva para usuários que já conheçam e já utilizaram

alguma distribuição Linux, pois este tipo de Sistema Operacional tem suas particularidades se

comparadas a outros que estão no mercado.

Como melhorias futuras, poderia citar a confecção de um Kit de desenvolvimento que contenha

uma Memória Flash e uma Memória SDRAM de maior capacidade, pois os aplicativos e device

drivers que se pode agregar na imagem do Kernel ficam limitados de acordo com o espaço

disponível para armazenamento e execução respectivamente, além de a expansão das interfaces,

por exemplo: mouse USB, unidades de armazenamento IDE em vez da utilização de uma

Memória Flash de tamanho maior, interface de áudio, interface de rede wireless, interface

touchscreen.

44

CAPÍTULO 7 - REFERÊNCIAS BIBLIOGRÁFICAS

UNIVERSIDADE FEDERAL DO PARANÁ. Normas para apresentação de documentos

científicos. Editora UFPR, volume 6, 2003.

ALTERA

CORPORATION.

Cyclone

II

Device

Handbook.

Disponível

em:

http://www.altera.com/literature/hb/cyc2/cyc2_cii5v1.pdf. Acessado em: Novembro de 2007.

ALTERA CORPORATION. NIOS II Processor Reference Handbook. Disponível em:

http://www.altera.com/literature/hb/nios2/n2cpu_nii5v1.pdf. Acessado em: Novembro de 2007.

ALTERA CORPORATION. NIOS II Software Developer’s Handbook. Disponível em:

http://www.altera.com/literature/hb/nios2/n2sw_nii5v2.pdf. Acessado em: Novembro de 2007.

ALTERA CORPORATION. QUARTUS II Version 7.1 Handbook. Disponível em:

http://www.altera.com/literature/hb/qts/quartusii_handbook.pdf. Acessado em: Novembro de

2007.

ALTERA CORPORATION. DE2 Development and Education Board User Manual.

Disponível em: http://www.altera.com/education/univ/materials/boards/DE2_UserManual.pdf.

Acessado em: Novembro de 2007.

DEVEGILI, A. J.; et al. O PROCESSADOR ALTERA NIOS II. Campinas, 2004. Trabalho

Final da Disciplina Arquitetura de Computadores I.

NAVABI, Z. Embedded Core Design with FPGAs. McGraw-Hill. New York, 2007.

LIMA, F. G. Projeto com Matrizes de Células Lógicas Programáveis. Porto Alegre, 1999.

Dissertação (Mestrado).

NIKKANEN, K. uClinux as an embedded Solution. 2003. Bachelor's Thesis

PERRY, D. L. VHDL: Programming by Examples. McGraw-Hill. New York, 2002.

YAGHMOUR, K., Building Embedded Linux Systems. O’REILLY, 2003.

45

AMORE R. d’. VHDL: Descrição e Síntese de Circuitos Digitais. LTC. Rio de Janeiro, 2005.

RUBINI, A.; CORBET, J. Linux Device Drivers. O’REILLY, 2001.

BROWN, S. D. VRANESIC, Z. G., Fundamentals of Digital Logic with Verilog Design.

McGraw-Hill. New York, 2003.

46

CAPÍTULO 8 – ANEXOS

47

8.1 – Artigo Científico

48

8.2 – Manual

49