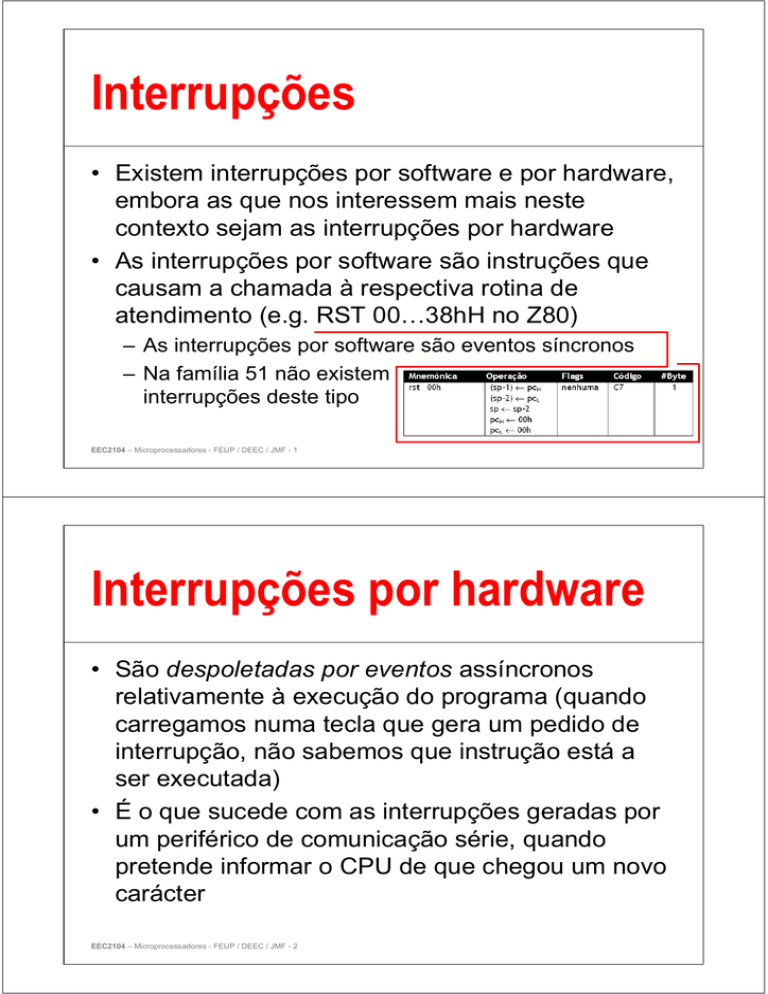

Interrupções

• Existem interrupções por software e por hardware,

embora as que nos interessem mais neste

contexto sejam as interrupções por hardware

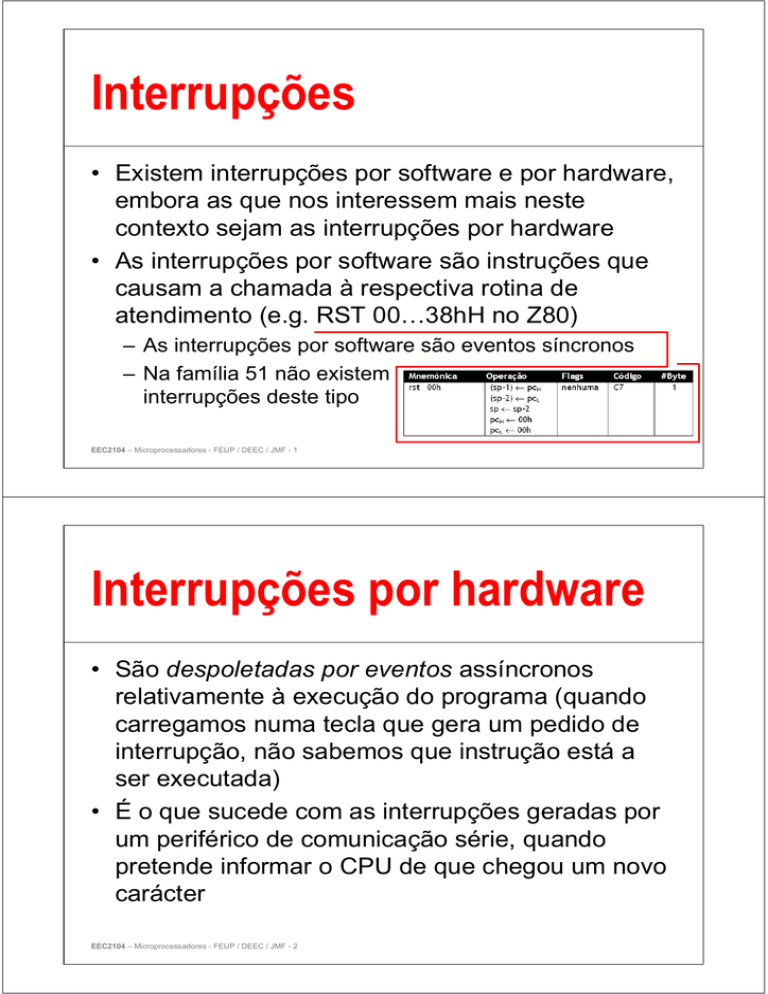

• As interrupções por software são instruções que

causam a chamada à respectiva rotina de

atendimento (e.g. RST 00…38hH no Z80)

– As interrupções por software são eventos síncronos

– Na família 51 não existem

interrupções deste tipo

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 1

Interrupções por hardware

• São despoletadas por eventos assíncronos

relativamente à execução do programa (quando

carregamos numa tecla que gera um pedido de

interrupção, não sabemos que instrução está a

ser executada)

• É o que sucede com as interrupções geradas por

um periférico de comunicação série, quando

pretende informar o CPU de que chegou um novo

carácter

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 2

Event driven applications

• Esta designação aplica-se nos casos em que não

existe acção enquanto não ocorrer um evento que

a determine

• São comuns nos embedded real-time systems

• Um sistema diz-se em tempo real quando é capaz

de responder e processar um evento num

intervalo de tempo pré-determinado

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 3

Latência das interrupções

• Esta latência corresponde ao intervalo de tempo

que decorre entre o pedido de interrupção e o

início ao seu atendimento – depende de vários

factores:

– Arquitectura do CPU (e.g. quando é que o CPU vê se

existem pedidos pendentes e dá início ao atendimento)

– Existirem ou não sequências de código que não

admitem o atendimento de interrupções

– Existência de interrupções de prioridade superior

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 4

Exemplo (não se refere à

família 51)

Nota: Este exemplo corresponde

a um sistema de interrupções

vectorizadas (o endereço de

atendimento é fornecido pelo

controlador de interrupções)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 5

Atendimento das

interrupções

• A maioria dos CPU verifica se existem pedidos de

interrupção pendentes quando termina a

execução de cada instrução

• Quando as interrupções estão habilitadas, o CPU

guarda o endereço da próxima instrução na stack

e carrega o PC com o endereço da rotina de

atendimento (ISR, interrupt service routine)

• Na família 51 estes endereços estão pré-definidos

(serão apresentados adiante)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 6

Segmentos críticos

• Neste exemplo, a sequência de instruções 1 a 4

não pode ser interrompida sem corrermos o risco

de funcionamento incorrecto

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 7

Prioridade das interrupções

• É possível atender múltiplas interrupções em

simultâneo (i.e. uma interrupção pode interromper

outra interrupção)

• O aninhamento (nesting) de interrupções requer a

existência de prioridades, que podem ser:

– Multi-nível (prioridades fixas)

– Multi-nível (prioridades dinâmicas)

– Nível único

Nota: Neste caso será possível

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 8

que uma interrupção interrompa

outra? E será possível atender

umas e ignorar outras? (máscaras)

Interrupções activas ao

nível

• Uma interrupção activa ao nível só é reconhecida

se o pino estiver no nível activo quando o CPU

verifica a existência de pedidos pendentes

– Podem perder-se os pedidos que deixem de estar

activos antes da verificação ser efectuada

– Também podem ocorrer múltiplos atendimentos

enquanto o pino continuar no nível lógico activo

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 9

Interrupções activas à

transição

• Nas interrupções activas à transição o pedido é

registado, o que elimina os problemas anteriores

• As interrupções deste tipo

são preferíveis quando os

pedidos são muito longos

ou muito curtos

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 10

Interrupções não

vectorizadas

• Quando o endereço da rotina de atendimento é

comum a mais do que uma fonte de interrupção, é

necessário determinar a sua origem

• Esta situação é frequente nas interrupções

geradas pelos periféricos de comunicação série

(nas interrupções por envio ou recepção)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 11

As interrupções na

família 51

/INT0

0

1

IT0

IE0

TF0

/INT1

0

1

IT1

TF1

TI

RI

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 12

IE1

Fontes de

interrupção

IE0 e IE1 são flags de interrupção

que pertencem ao registo TCON

(SFR com endereço 88H)

Gestão das interrupções

• O código executado pelo microcontrolador pode

activar / desactivar (set / clear) todas as flags de

interrupção

• Cada fonte de interrupção pode ser habilitada /

inibida individualmente (registo IE nos SFR)

• A cada fonte de interrupção pode ser atribuída

uma prioridade alta ou baixa (registo IP nos SFR)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 13

/INT0

0

1

Interrupções externas

IT0

IE0

TF0

/INT1

0

1

IT1

TF1

TI

RI

• /INT0 e /INT1 podem ser activos ao nível (0) ou à

transição (↓), de acordo com o conteúdo do

registo TCON (SFR com endereço 88H)

• Se as interrupções forem activas à transição, as

flags que as geram são limpas pelo hardware

quando a respectiva rotina é executada (caso

contrário, terá que ser o código do utilizador a

fazê-lo)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 14

IE1

/INT0

Interrupções dos T/C

0

1

IT0

IE0

TF0

/INT1

0

1

IT1

IE1

TF1

TI

RI

• As interrupções pedidas pelos temporizadores /

contadores são geradas por TF0 e TF1 e

activadas por rollover nos respectivos registos

(excepto T/C 0 em modo 3, como se verá mais

tarde)

• Quando é gerada uma interrupção proveniente

dos T/C, a flag que a gerou é limpa pelo hardware

quando a rotina de atendimento é executada

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 15

Interrupções da

comunicação série

/INT0

0

1

IT0

TF0

/INT1

0

1

IT1

TF1

TI

RI

• Os pedidos de interrupção do periférico de

comunicação série resultam do OR entre as flags

RI (recepção) e TI (transmissão)

• Nenhuma destas flags é limpa pelo hardware

quando a respectiva rotina é executada (o código

da rotina tem primeiro que identificar a causa da

interrupção e depois limpar a flag)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 16

IE0

IE1

O registo IE (end. SFR A8H)

– endereçável ao bit

• Este registo permite-nos habilitar / inibir cada

fonte de interrupção:

IE.7 IE.6 IE.5 IE.4 IE.3 IE.2 IE.1 IE.0

EA

-

-

ES

ET1 EX1 ET0 EX0

– EA inibe todas as interrupções se estiver em 0; se

estiver em 1, estarão habilitadas as que tiverem o bit

IE.x em 1

– ES: periférico série; ET1 e ET0: T/C 1 e 0; EX1 e EX0:

externas (pinos /INT1 e /INT0)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 17

O registo IP (end. SFR B8H)

– endereçável ao bit

• Este registo permite-nos atribuir a cada fonte de

interrupção uma prioridade alta ou baixa:

IP.7 IP.6 IP.5 IP.4 IP.3 IP.2 IP.1 IP.0

-

-

-

PS

PT1 PX1 PT0 PX0

– Uma fonte de interrupção terá prioridade alta quando o

bit IP.x estiver em 1 e baixa quando estiver em 0

– PS: periférico série; PT1 e PT0: T/C 1 e 0; PX1 e PX0:

externas (pinos /INT1 e /INT0)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 18

O registo TCON (end. SFR

88H) – endereçável ao bit

• Para além de controlar os T/C, este registo está

também relacionado com as interrupções

externas:

TC.7 TC.6 TC.5 TC.4 TC.3 TC.2 TC.1 TC.0

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

– IEx: O hardware activa (set) esta flag à transição

descendente em /INTx e limpa-a (clear) quando a

respectiva rotina de atendimento é executada

– ITx: Se estiver em 1 a interrupção em /INTx é activa à

transição descendente; se não, é activa ao nível 0.

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 19

Atendimento das

interrupções

• Ao atender uma interrupção, o hardware do

80C51 determina a execução de uma instrução

LCALL para a respectiva rotina de atendimento:

– Endereços de atendimento: IE0 - 0003H; TF0 - 000BH;

IE1 - 0013H; TF1 - 001BH; RI ou TI - 0023H

– LCALL força o PC na stack, mas quaisquer outros

registos (e.g. ACC, PSW, ...) terão que ser guardados

pelo código do utilizador

– A flag associada à interrupção é limpa pelo hardware

nuns casos, mas noutros terá que o código a fazê-lo

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 20

Retorno das interrupções

• A execução da rotina de atendimento continua até

que seja encontrada uma instrução RETI (return

from interrupt):

– RETI informa o processador que terminou o

atendimento à interrupção e extrai da stack o endereço

de retorno

– RET (retorno de subrotina) faria algo semelhante, mas

manter-se-ia a indicação de estar em curso o

atendimento a uma interrupção (qual é o problema?)

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 21

Exemplo (KEIL):

Interrupções via /INT0

; código para ilustrar o atendimento de interrupções

; externas em /INT0, activas à transição

cseg

at

0

salta:

jmp

inicio

; uma vez que 0003H tem que conter o código de atendimento

; a /INT0, em 0000 cabe apenas uma instrução de salto

cseg

at

0003h

intext0:

inc

r1

reti

; o atendimento a /INT0 apenas incrementa o R1, pelo que o

; seu conteúdo nos diz quantas interrupções foram atendidas

cseg

at

0010h

inicio:

mov

r1,#0

mov

tcon,#01

mov

ie,#81h

; programa o funcionamento das interrupções via /INT0

ciclo:

mov

a,p0

add

a,p1

mov

p2,a

jmp

ciclo

; está sempre a colocar em P2 o valor de P1+P0

end

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 22

Int. via /INT0: Visualização

no dScope

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 23

Trabalho do dado (Stop via

/INT0)

• Que alterações são necessárias para implementar

o botão de Stop através de /INT0? (para libertar a

tecla que era usada

para este efeito)

Como deve ser feita a

inicialização? Que

tarefas deverão ser

realizadas pela rotina

de atendimento?

EEC2104 – Microprocessadores - FEUP / DEEC / JMF - 24