Arquitetura e Organização de Computadores – EL66C – 1a. Prova – 24/11/14

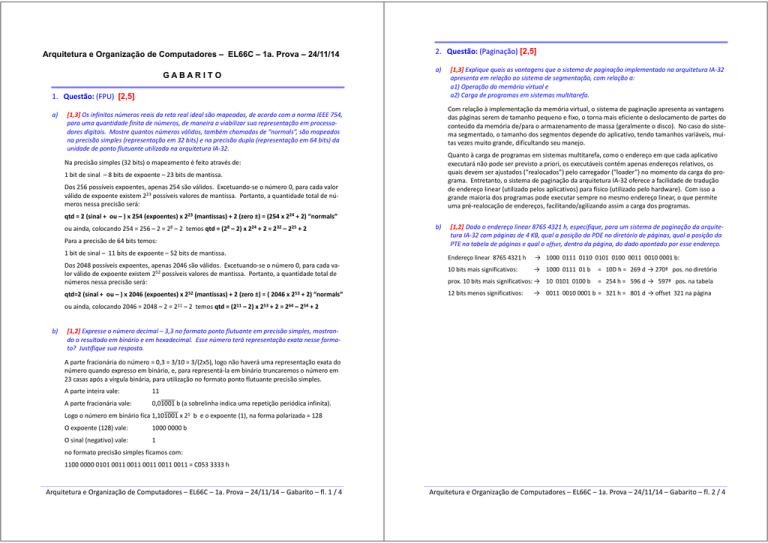

2. Questão: (Paginação) [2,5]

a)

GABARITO

1. Questão: (FPU) [2,5]

a)

[1,3] Explique quais as vantagens que o sistema de paginação implementado na arquitetura IA-32

apresenta em relação ao sistema de segmentação, com relação a:

a1) Operação da memória virtual e

a2) Carga de programas em sistemas multitarefa.

Com relação à implementação da memória virtual, o sistema de paginação apresenta as vantagens

das páginas serem de tamanho pequeno e fixo, o torna mais eficiente o deslocamento de partes do

conteúdo da memória de/para o armazenamento de massa (geralmente o disco). No caso do sistema segmentado, o tamanho dos segmentos depende do aplicativo, tendo tamanhos variáveis, muitas vezes muito grande, dificultando seu manejo.

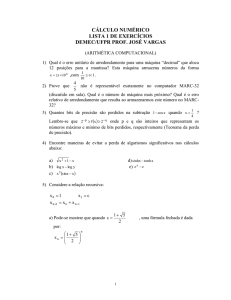

[1,3] Os infinitos números reais da reta real ideal são mapeados, de acordo com a norma IEEE 754,

para uma quantidade finita de números, de maneira a viabilizar sua representação em processadores digitais. Mostre quantos números válidos, também chamados de “normals”, são mapeados

na precisão simples (representação em 32 bits) e na precisão dupla (representação em 64 bits) da

unidade de ponto flutuante utilizada na arquitetura IA-32.

Quanto à carga de programas em sistemas multitarefa, como o endereço em que cada aplicativo

executará não pode ser previsto a priori, os executáveis contém apenas endereços relativos, os

quais devem ser ajustados (“realocados”) pelo carregador (“loader”) no momento da carga do programa. Entretanto, o sistema de paginação da arquitetura IA-32 oferece a facilidade de tradução

de endereço linear (utilizado pelos aplicativos) para físico (utilizado pelo hardware). Com isso a

grande maioria dos programas pode executar sempre no mesmo endereço linear, o que permite

uma pré-realocação de endereços, facilitando/agilizando assim a carga dos programas.

Na precisão simples (32 bits) o mapeamento é feito através de:

1 bit de sinal – 8 bits de expoente – 23 bits de mantissa.

Dos 256 possíveis expoentes, apenas 254 são válidos. Excetuando-se o número 0, para cada valor

válido de expoente existem 223 possíveis valores de mantissa. Portanto, a quantidade total de números nessa precisão será:

qtd = 2 (sinal + ou – ) x 254 (expoentes) x 223 (mantissas) + 2 (zero ±) = (254 x 224 + 2) “normals”

ou ainda, colocando 254 = 256 – 2 = 28 – 2 temos qtd = (28 – 2) x 224 + 2 = 232 – 225 + 2

Para a precisão de 64 bits temos:

1 bit de sinal – 11 bits de expoente – 52 bits de mantissa.

Dos 2048 possíveis expoentes, apenas 2046 são válidos. Excetuando-se o número 0, para cada valor válido de expoente existem 252 possíveis valores de mantissa. Portanto, a quantidade total de

números nessa precisão será:

qtd=2 (sinal + ou – ) x 2046 (expoentes) x

252

(mantissas) + 2 (zero ±) = ( 2046 x

253

+ 2) “normals”

b)

[1,2] Dado o endereço linear 8765 4321 h, especifique, para um sistema de paginação da arquitetura IA-32 com páginas de 4 KB, qual a posição da PDE no diretório de páginas, qual a posição da

PTE na tabela de páginas e qual o offset, dentro da página, do dado apontado por esse endereço.

Endereço linear 8765 4321 h

→ 1000 0111 0110 0101 0100 0011 0010 0001 b:

10 bits mais significativos:

→ 1000 0111 01 b

prox. 10 bits mais significativos: → 10 0101 0100 b

12 bits menos significativos:

= 10D h = 269 d → 270ª pos. no diretório

= 254 h = 596 d → 597ª pos. na tabela

→ 0011 0010 0001 b = 321 h = 801 d → offset 321 na página

ou ainda, colocando 2046 = 2048 – 2 = 211 – 2 temos qtd = (211 – 2) x 253 + 2 = 264 – 254 + 2

b)

[1,2] Expresse o número decimal – 3,3 no formato ponto flutuante em precisão simples, mostrando o resultado em binário e em hexadecimal. Esse número terá representação exata nesse formato? Justifique sua resposta.

A parte fracionária do número = 0,3 = 3/10 = 3/(2x5), logo não haverá uma representação exata do

número quando expresso em binário, e, para representá-la em binário truncaremos o número em

23 casas após a vírgula binária, para utilização no formato ponto flutuante precisão simples.

A parte inteira vale:

11

A parte fracionária vale:

0,01001 b (a sobrelinha indica uma repetição periódica infinita).

Logo o número em binário fica 1,101001 x 21 b e o expoente (1), na forma polarizada = 128

O expoente (128) vale:

1000 0000 b

O sinal (negativo) vale:

1

no formato precisão simples ficamos com:

1100 0000 0101 0011 0011 0011 0011 0011 = C053 3333 h

Arquitetura e Organização de Computadores – EL66C – 1a. Prova – 24/11/14 – Gabarito – fl. 1 / 4

Arquitetura e Organização de Computadores – EL66C – 1a. Prova – 24/11/14 – Gabarito – fl. 2 / 4

3. Questão: (Interrupções e Descritores) [2,5]

4. Questão: (Cache, Memórias) [2,5]

a)

a)

[1,3] Liste os vários eventos que ocorrem no hardware de um sistema da arquitetura IA-32 quando ocorre uma interrupção no momento que o sistema está executando um aplicativo em modo

protegido, o qual tem nível de privilégio de usuário. Suponha que o descritor de interrupção apontado pela interrupção contenha um “Interrupt Gate Descriptor”.

n em Xn representa a largura (ou profundidade) em bits, suportada pela memória.

Internamente, uma memória DDRn com arquitetura Xn-prefetch, faz leituras/escritas simultâneas

de Xn bits a cada clock.

Quando o sistema está executando em modo protegido com nível de privilégio de usuário e ocorre

uma interrupção, ocorre inicialmente uma mudança de privilégio para o nível de privilégio de supervisor.

Externamente, essa mesma memória disponibiliza n bits em seus pinos a cada meio clock permitindo um total X leituras consecutivas sem atraso realizadas a cada meio clock, ou seja Xn bits lidos

em X clocks/2 ou X/2 clocks.

Com isso há uma mudança de pilha, e os valores dos registradores SS (Stack Segment Register) e

ESP (Extended Stack Pointer), que descrevem a pilha de nível de usuário, são salvos na nova pilha,

do nível de privilégio do supervisor.

A tecnologia DDR utiliza 2n-prefetch. A DDR2 4n-prefetch. As tecnologias DDR3 e DDR4 utilizam

ambas 8n-prefetch.

A seguir, o registrador EFLAGS e o endereço de retorno (conteúdo de CS e EIP), são salvos na nova

pilha.

Caso a interrupção tenha sido causada por uma exceção de software, a qual tem um código de

erro, então também o código de erro será armazenado na nova pilha.

Finalmente, o hw passará a executar a rotina apontada pelo descritor de interrupção correspondente.

[1,3] Explique o que significa dizer que uma memória DDRn suporta uma arquitetura Xn-prefetch.

Indique também qual o valor de X para as tecnologias de memória DDR, DDR2, DDR3 e DDR4.

b)

[1,2] Um sistema da arquitetura IA-32 dispõe de uma cache L2, unificada, de 2048 KB, associativa por conjuntos, com 8 vias. Sabe-se que cada linha de cache é composta 64 bytes. Qual será a

largura, em bits, de cada via do diretório dessa cache – considere apenas os bits do diretório utilizados na comparação de endereço, sem contar os bits de válido ou LRU. Quais dos 32 bits de um

endereço linear acessado serão utilizados para comparar com o conteúdo de cada via do diretório?

Cada via da cache conterá 2048 KB / 8 = 256 KB = 218 bytes / via.

b)

[1,2] Desenhe o layout, em bits, do registrador de segmento CS, indicando sua finalidade e sua

largura, em bits, e explicando qual o significado de cada conjunto dos bits que o integram, quando

o sistema opera em modo protegido.

Índice para descritor

15

..

TI CPL

3 2 1 .. 0

Em modo protegido o registrador de segmento CS contém um seletor que aponta para um descritor do código que está em execução, em uma tabela de descritores, que pode ser a GDT (tabela

global de descritores) ou uma LDT (tabela local de descritores). Sua largura é de 16 bits, sendo

que:

•

os bits 0 e 1 codificam o privilégio do programa em execução CPL (“Current Privilege Level”).

•

o bit 2 discrimina entre tabela global (TI=0) ou tabela local (TI=1) de descritores.

Cada linha contém 64 bytes = 26 bytes. Logo cada via conterá 218 / 26 = 212 linhas = 4096 linhas.

Dado um endereço linear de 32 bits, teremos:

bits 0:5 –

(6 bits)

– determinam 1 de 64 bytes dentro da linha.

bits 6:17 –

(12 bits)

– determinam 1 de 4096 linhas dentro da via.

bits 18:31 –

(14 bits)

– utilizados para comparar com os 14 bits de cada via do diretório.

Portanto, cada via do diretório deverá ter 14 bits para comparação, os quais serão comparados com

os bits 18:31 do endereço linear acessado.

os bits 3 a 13 (13 bits) representam o índice que aponta para 1 de 213 = 8192 possíveis descritores na tabela em questão

•

Arquitetura e Organização de Computadores – EL66C – 1a. Prova – 24/11/14 – Gabarito – fl. 3 / 4

Arquitetura e Organização de Computadores – EL66C – 1a. Prova – 24/11/14 – Gabarito – fl. 4 / 4