ATENÇÃO:

O material a seguir é parte de uma das aulas da apostila

de MÓDULO 4 que por sua vez, faz parte do CURSO

de ELETROELETRÔNICA ANALÓGICA -DIGITAL

que vai do MÓDULO 1 ao 4.

A partir da amostra da aula, terá uma idéia de onde o

treinamento de eletroeletrônica poderá lhe levar.

Você poderá adquirir o arquivo digital da apostila

completa (16 aulas), ou ainda na forma impressa que

será enviada por por correio. Entre na nova loja

virtual CTA Eletrônica e veja como:

www.lojacta.com.br

Além de ter a apostila e estuda-la, torne-se aluno e

assim poderá tirar dúvidas de cada uma das questões

dos blocos atrelados a cada uma das aulas da apostila,

receber as respostas por e-mail, fazer parte do

ranking de módulos e após a conclusão do módulo

com prova final, participar do ranking geral e poder

ser chamado por empresas do ramo de eletroeletrônica.

Saiba mais como se tornar um aluno acessando nossa

página de cursos:

www.ctaeletronica.com.br/web/curso.asp

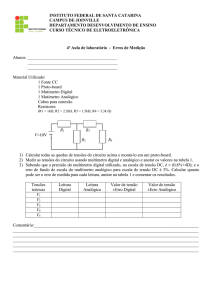

APOSTILA

MÓDULO - 4

ELETRÔNICA DIGITAL - 4

AULA

13

Conversor Digital-Analógico e Analógico-Digital

A quantidade de bit´s e a taxa de amostragem

Resolução, Aliasing, Dither, Oversampling

Comparador Digital (CD4063) - CAF Digital

Multiplicadores e Divisores de Frequência

Defasador digital de 90º

CONVERSOR DIGITAL - ANALÓGICO

A eletrônica digital tornou-se a base para um grande

avanço tecnológico e de grande ajuda no

processamento e transmissão de sinais. O grande

problema é que em nosso dia a dia, todos os

sentidos humanos e campos eletromagnéticos que

nos rodeiam, são analógicos e portanto não podem

ser processados corretamente por circuitos digitais.

A solução para este problema foi criar circuitos que

transformem os sinais analógicos em sinas digitais

e também circuitos que transformem os sinais

digitais novamente em sinais analógicos, que

possam ser “compreendidos” pelos seres humanos

ou máquinas de diversos tipos. Vamos começar

com os Conversores Digitais-Analógicos (D/A).

figura 1

memórias (chamado de registrador paralelo).

Esses códigos paralelos (S0, S1, S2 e S3) são

transferidos ao conversor DA (Digital-Analógico),

que pode ser representando pela montagem M1-3,

onde os códigos na entrada do circuito,

determinarão que os resistores assumam valores

tais que colocarão uma realimentação ao

operacional e com isso, será determinada uma

tensão de saída, que poderá variar em 16

possibilidades. Após o conversor DA, teremos que

ter o filtro final (low-pass-filter) para que as

variações entre os 16 patamares de tensão possam

ser as mais suaves possíveis.

Na figura 3, temos a diagramação em blocos de um

circuito conversor digital-analógico.

IN

IN

DAC

OUT

CONVERSOR

Série/Paralelo

Registrador de

deslocamento

OSCILADOR

CLOCK

A simbologia utilizada para o conversor DAC

(Conversor Digital-Analógico), pode ser vista na

figura 1, enquanto a simbologia para o conversor

ADC (Conversor Analógico-Digital), pode ser vista

na figura 2.

figura 2

IN

ADC

OUT

Fizemos um estudo anterior onde vimos que os

sinais digitais série quando processados, podem

ser convertidos em código paralelo. Assim, o

primeiro passo será transformar os sinais digitais

seriais em códigos binários paralelos (conversor

série-paralelo ou registrador de deslocamento);

depois devemos criar um segundo clock (clock

paralelo) que deverá ser uma divisão do clock serial

pelo número de bits do sinal paralelo, visando

armazenar o código paralelo em outro conjunto de

ELETRÔNICA

S0

S1

S2

S3

REGISTRADOR

PARALELO

S0

S1

S2

S3

CONVERSOR

D/A

BUFFER

OUT

figura 3

CONVERSOR SÉRIE-PARALELO: Este 1° bloco

representa um circuito conversor de sinais seriais

numa saída de dados digitais paralelos (registrador

de deslocamento), que foi estudado anteriormente

na aula 12. Podemos imaginar que este bloco seja o

mesmo circuito da figura 1, aula 12.

OSCILADOR CLOCK E DIVISOR: Na figura 3a e

3b (aula 12) tínhamos o circuito de clock formado a

partir de um oscilador e posteriormente um circuito

de divisão para gerar o clock do sinal paralelo, cuja

frequência deve ser um submúltiplo do clock; esta

divisão será tantas vezes quanto for o número de

bits da saída paralela.

REGISTRADOR PARALELO: responsável por ter

em sua entrada uma série de variações ou

deslocamento de bit´s, cujas variações serão

passadas e memorizadas para a saída, até que

novo pulso de clock mude a saída. O circuito pode

ser visto na figura 47 da aula 11.

CONVERSOR A/D: O conversor Digital-Analógico

propriamente dito pode ser visto na figura 4, sendo

este baseado em tensões discretas geradas a partir

FONTES - AMPLIF. DE POTÊNCIA - VALVULAS - OPERACIONAIS - ELETRÔNICA DIGITAL

165

APOSTILA

MÓDULO - 4

de divisores de tensão.

Inicialmente os dados binários irão chavear

transistores (1 para cada bit) que formarão um

divisor resistivo com R15 (R1, R2, R3 e R4); este

divisor resistivo irá determinar o ganho do 1°

Amplificador, quanto menor o resistor equivalente

entre R1 a R4 maior será o ganho do amplificador e

consequentemente maior será a tensão de saída

(sinal analógico).

+B

REFORÇADOR

BOOSTER

SAÍDA

ANALÓGICA

2

P1

1

R5

FILTRAGEM

R15

FILTRAGEM: ainda na figura 3 (página anterior)

teremos um capacitor na saída do circuito que

filtrará (LPF) as altas frequências geradas pelo sinal

digital, integrando o sinal analógico.

Teremos então na saída um sinal analógico cuja

amplitude dependerá da codificação binária da

entrada digital. Este sinal normalmente é serial,

mas os conversores comerciais, geralmente

possuem apenas entrada paralela, sendo

necessário o circuito conversor série paralelo

compatível com o clock serial e com uma saída

paralela com o mesmo número de bits da entrada

do conversor D/A.

Na figura 5, podemos ver o conversor DigitalAnalógico, montado no módulo 1 (M1-3), que

mostra de forma muito simples, como dados

paralelos, colocados nas chaves (aqui serão níveis

de tensão de 12V ou 0V) SW1, SW2, SW3 e SW4,

serão combinados de forma a gerar uma tensão DC

em 16 níveis diferentes que após deverá ser filtrada.

-B

CONVERSOR ANALÓGICO - DIGITAL

R4

4

A4

2

3

A3

R2

R3

A2

R1

figura 4

1

A1

4,2V

ENTRADA PARELELA DIGITAL

Na saída do 1° amplificador já teremos um sinal

digital convertido em sinal analógico; o

potenciômetro P1 ajustará a tensão de referência

do amplificador (entrada não-inversora),

determinando a tensão de 1/2 Vcc da saída do

amplificador (nível DC do sinal analógico).

BUFFER: Na figura 3, temos um segundo

amplificador, que servirá de reforço para o sinal

analógico, dando ganho em corrente e ajustando

sua amplitude.

166

Vamos ver como poderemos converter os sinais (tensão)

analógicos numa codificação binária digital para ser

processado ou transmitido por circuitos digitais.

Vamos pegar como exemplo de um sinal analógico, uma

senoide como mostra a figura 6.

figura 6

1,2V

Este sinal analógico pode ter infinitos valores entre o pico

máximo e o pico mínimo (amplitude do sinal). O primeiro

passo será determinar quantos bits terá nossa saída digital;

quanto mais bits maior será a resolução e

qualidade do sinal digital. Estes bits

gerarão um número de combinações,

figura 5

determinando os níveis discretos de

tensão; como exemplo vamos fixar a

saída digital em 4 bits. Estes 4 bits

determinarão uma saída com 16 níveis

de tensão.

Como no nosso exemplo temos 3 Vpp

vamos supor que a amplitude máxima

seja 5V e a mínima 0V permitindo sinais

de até 5 Vpp. Dividindo 5V em 15

intervalos (16 níveis) teremos 5V/15 =

0,333V por nível, formando os níveis

discretos como mostra a figura 7.

O próximo passo é determinar a

frequência do clock serial que irá

determinar a qualidade de preservação

do sinal analógico em códigos digitais;

quanto maior a frequência mais pontos

de amostragem teremos e

consequentemente melhor fidelidade do

FONTES - AMPLIF. DE POTÊNCIA - VALVULAS - OPERACIONAIS - ELETRÔNICA DIGITAL

ELETRÔNICA

APOSTILA

MÓDULO - 4

sinal digital comparado com o sinal analógico.

figura 7

NÍVEIS ANALÓGICOS QUANTIZADOS

5V

DIGITAL

1111

de amostragem) devemos retirar do sinal analógico as

amostras analógicas e finalmente quantizarmos o sinal

analógico em níveis discretos pré-fixados (16 níveis para 4

bits); transformando o sinal analógico num sinal

quantizado, como mostra a figura 10.

figura 10

16 NÍVEIS

PARA 4 BITS

0011

0010

0001

0000

1V

0,66V

0,33V

0V

Por outro lado qual deverá ser a frequência mínima de

amostragem (clock) para representarmos um sinal

analógico. Podemos voltar ao nosso exemplo da figura 6, e

pegarmos uma frequência de amostragem qualquer e

olharmos o sinal quantizado a partir desta amostragem,

como nos mostra a figura 8.

figura 8

SINAL ANALÓGICO

COM PONTOS DE AMOSTRAGEM

SINAL QUANTIZADO

PELOS PONTOS

Depois podemos passar os níveis do sinal para o código

binário correspondente, através de um arranjo de várias

portas lógicas gerando o respectivo código binário para

cada nível, gerando um sinal digital de 4 bits paralelos,

como mostra o diagrama em blocos da figura 11.

PARTE DO SINAL

DESCARACTERIZADO

Podemos ver que para as baixas frequências o sinal

quantizado ainda representa o sinal analógico, mas nas

altas frequências o sinal quantizado descaracterizou

completamente o sinal analógico.

Como o sinal analógico pode ser genericamente

representado por um ciclo acendente (semiciclo positivo) e

outro decendente (semiciclo negativo) teremos que ter no

mínimo dois pontos de amostragem no mesmo ciclo do sinal

analógico; como a frequência é dada por ciclos em

segundos teremos que ter no mínimo uma frequência de

amostragem igual ao dobro da maior frequência do sinal

analógico (figura 9).

figura 9

SINAL ANALÓGICO

COM PONTOS DE AMOSTRAGEM

SINAL ANALÓGICO

COM PONTOS DE AMOSTRAGEM

Existe um teorema matemático que prova que a taxa

mínima de amostragem digital para mantermos a

representação de um sinal analógico é de 2,3 vezes a maior

frequência do sinal amostrado; mas na prática os

conversores comerciais utilizam a taxa mínima de apenas 2

vezes.

Se nosso exemplo da figura 6 for um sinal de áudio

podemos prever que a maior frequência audível para o ser

humano é 20kHz portanto neste caso a menor frequência

de amostragem deverá ser de 46 kHz (clock mínimo); é

claro que se pudermos utilizar um clock com frequências

superiores a esta, teremos uma melhoria no sinal nas altas

frequências

Agora que escolhemos também a frequência do clock (taxa

ELETRÔNICA

QUANTIZADOR

LPF

CONVERSOR

A/D

SAÍDAS

DIGITAIS

SINAL

ANALÓGICO

figura 11

OSCILADOR

CLOCK

Este diagrama representa todo o “tratamento” necessário

para transformarmos um sinal analógico em níveis binários

digitais.

LPF e BUFFER : O LPF serve, como já comentado, para

limitar a máxima frequência digitalizada dependendo da

frequência de amostragem e normalmente é formado por

capacitores e indutores; o BUFFER é o circuito reforçador

formado basicamente por transistores amplificadores ou

operacionais.

CHAVE SAMPLE & HOLD : Esta chave serve para retirar

uma amostragem (sample) e fazer a retenção (hold) do

mesmo para o circuito de quantização.

CIRCUITO QUANTIZADOR : Ele transformará as amostras

do sinal analógico em níveis discretos de acordo com a

frequência de amostragem e número de bits.

CONVERSOR A/D : Este circuito é o que realmente

transforma os níveis quantizados numa combinação

binária, ele é formado por comparadores de tensão,

geralmente implementados com operacionais, e depois sua

codificação binária é gerada pela associação de portas

lógicas, como ilustra a figura 12.

OSCILADOR: Este pode ser gerado a partir de astáveis ou

osciladores a cristais subdivididos até gerar a frequência de

amostragem e o clock digital (paralelo).

Estes tipos de conversores Analógico-digital foram

utilizados em quase todos os tipos de aparelhos eletrônicos;

mas com a evolução digital/eletrônica foram criados novos

tipos de conversores mais eficientes, baseado em

contadores e comparadores. Estes novos conversores

FONTES - AMPLIF. DE POTÊNCIA - VALVULAS - OPERACIONAIS - ELETRÔNICA DIGITAL

167

APOSTILA

MÓDULO - 4

figura 12

+B

CIRCUITO

LÓGICO

SAÍDAS

DIGITAIS

Entrada

quantizada

estão baseados no diagrama em blocos simplificado da

figura 13.

figura 13

LPF

SAÍDA

DIGITAL

PARALELA

BUFFER

SINAL

ANALÓGICO

CONVERSOR

D/A

OSCILADOR

CLOCK

CLOCK

DIGITAL

Neste diagrama podemos ver o sinal analógico entrando

também no circuito através do LPF e logo após um buffer ou

reforçador; daí, o sinal analógico vai para um comparador

para identificar a combinação binária correspondente ao

sinal analógico e mandá-la para o registrador e daí para a

saída digital.

O circuito contador irá criar as combinações binárias a partir

do zero até chegar a todos os bits com nível 1, passando

necessariamente pela combinação binária correspondente

ao nível analógico. Na saída do contador temos um

conversor D/A que passará esta combinação binária em

nível analógico, e este será comparado com o nível

analógico que está saindo do booster.

Caso os níveis sejam diferentes nada ocorrerá e o circuito

contador continuará gerando combinações digitais até

coincidir com o nível analógico; quando ocorrer esta

coincidência o circuito comparador irá resetar o contador e

disparar o registrador mandando para a saída do nosso

conversor A/D a combinação binária correta.

Temos ainda o oscilador que irá determinar a taxa de

amostragem deste conversor através do clock do contador e

também irá gerar através de subdivisão o clock digital do

sinal paralelo.

Este conversor aumentará a qualidade do sinal digitalizado

e também poderá ser implementado apenas com circuitos

digitais diminuindo o uso de componentes analógicos como

capacitores, indutores e diodos. Na figura 14 temos um

exemplo de um conversor analógico digital baseado neste

diagrama em blocos.

Neste circuito temos um conversor A/D de 4 bits com uma

entrada analógica e uma saída digital paralela (4 bits). Para

entender o circuito temos como exemplo uma entrada

analógica com 13V de tensão.

O circuito contador está funcionando através dos pulsos de

clock cuja frequência deverá ser bem maior que a

frequência do sinal analógico (mínimo 2,3 vezes); quando a

saída do contador chegar a combinação binária 1101, o

conversor D/A irá gerar na entrada inversora do operacional

uma tensão um pouco maior que 13V, fazendo a saída deste

ir para nível baixo, bloqueando os pulsos de clock do

contador, mantendo-o na combinação 1101. Ao mesmo

tempo através do inversor os F/F’s (registrador) receberão

um pulso de clock, mandando esta combinação binária

(1101) para a saída do conversor. Na figura 15, temos uma

foto de um integrado conversor digital analógico.

figura 15

figura 14

CLK

CLK

(13V)

(3V)

168

CK

F/F

"D"

SAÍDAS

DIGITAIS

1

F/F

"D"

1

F/F

"D"

0

F/F

"D"

1

FONTES - AMPLIF. DE POTÊNCIA - VALVULAS - OPERACIONAIS - ELETRÔNICA DIGITAL

(MSB)

bit's

correspondentes

a 13V

(LSB)

ELETRÔNICA

APOSTILA

MÓDULO - 4

APÊNDICE - CONVERSORES DIGITAIS ANALÓGICOS - CONCEITOS

Resolução

A resolução do conversor, indica o número de

valores discretos capaz de produzir toda a gama de

valores analógicos. Os valores são normalmente

armazenados eletronicamente de forma binária,

portanto, a resolução é normalmente expressa em

bits . Em consequência, o número de valores

discretos disponíveis, ou "níveis", normalmente é

uma potência de dois. Por exemplo, um ADC

(Conversor Analógico-digital) com uma resolução

de 8 bits pode codificar uma entrada analógica para

256 diferentes níveis, desde 28 = 256. Os valores

podem representar a variação de 0 a 255 (ou seja,

inteiro sem sinal) ou de -128 a 127 (ou seja, inteiro

com negativo e positivo), dependendo da aplicação.

Resolução também pode ser definida

eletricamente, e expressa em volts . A variação

mínima de tensão necessária para garantir uma

mudança no nível de código de saída é chamado o

LSB (bit menos significativo, uma vez que esta é a

tensão representada por uma mudança na LSB). A

resolução Q da ADC é igual à variação de tensão

LSB. A resolução da tensão de um ADC é igual à sua

gama de medição de tensão global, dividido pelo

número de intervalos discretos de tensão:

Alguns exemplos:

Exemplo 1

Esquema de codificação como na figura 1

Escala completa gama de medida = 0 a 10 volts

Resolução do ADC é de 12 bits: 2 12 = 4096 níveis

de quantização (códigos)

ADC resolução da tensão, Q = (10 V - 0 V) / 4096 =

10 V / 4096 ≈ ≈ 0,00244 V 2,44 mV.

Exemplo 2

Esquema de codificação como na figura 2

faixa de medição completa = escala de -10 a 10

volts

ELETRÔNICA

Resolução do ADC é de 14 bits: 2 14 = 16384 níveis

de quantização (códigos)

ADC resolução tensão é, Q = (10 V - (-10 V)) / 16384

= 20 V / V 16384 ≈ ≈ 0,00122 1,22 mV.

Exemplo 3

Esquema de codificação como na figura 3

faixa de medição completa = escala 0 a 7 volts

Resolução do ADC é de 3 bits: 2 3 = 8 níveis de

quantização (códigos)

ADC resolução tensão é, Q = (7 V - 0 V) / 7 = 7 V / 7 =

1 V = 1000 mV

Na maioria das ADCs, o código de saída menor ("0"

em um sistema sem assinatura) representa uma

faixa de tensão que é 0,5 Q , ou seja, metade da

resolução da tensão ADC (Q). O maior código

representa um intervalo de 1,5 Q como na figura 2

(se isso fosse 0,5 Q , também, o resultado seria

como na figura 3). Os outros N - 2 códigos são todos

iguais em largura e representa a resolução da

tensão ADC ( Q ), calculado acima. Fazendo isso,

FONTES - AMPLIF. DE POTÊNCIA - VALVULAS - OPERACIONAIS - ELETRÔNICA DIGITAL

169

APOSTILA

MÓDULO - 4

os centros de código em uma tensão de entrada que

representa o M ª divisão da faixa de tensão de

entrada. Esta prática é chamada de operação "midtread".

A exceção a esta convenção é usada no

processador Microchip PIC, onde todos os passos

M são de igual largura, como mostrado na figura 1.

Esta prática é chamada operação de "Mid-Rise com

Offset".

Erro de quantização

Erro de quantização (ou ruído de quantização) é a

diferença entre o sinal original e o sinal digitalizado.

Assim, a magnitude do erro de quantização no

instante de amostragem é entre zero e metade de

um LSB. O erro de quantização ocorre devido à

resolução finita da representação digital do sinal, e

é uma imperfeição inevitável em todos os tipos de

ADCs.

Na prática, a resolução útil de um conversor é

limitada pela melhor relação sinal/ruído (SNR), que

pode ser alcançado por um sinal digitalizado.

Não-linearidade

Todos os ADCs sofrem de erros de não-linearidade,

causados por suas imperfeições físicas, causando

em sua saída um desvio na função linear (ou

alguma outra função, no caso de um ADC nãolinear, propositalmente) de sua entrada. Às vezes,

estes erros podem ser atenuados por calibração, ou

evitado através de testes.

Parâmetros importantes para a linearidade são

“não-linearidade integral” (INL) e “não-linearidade

diferencial” (DNL). Estes parâmetros “nãolinearidades” reduzem a gama dinâmica dos sinais

que podem ser digitalizados pelo ADC, reduzindo

também a resolução efetiva da ADC.

tipo de resposta

ADCs Lineares

A maioria dos ADCs são de um tipo conhecido como

lineares. O termo linear implica que na gama de

valores de entrada tem uma relação linear com o

valor de saída

ADCs Não-lineares

Se a função densidade de probabilidade de um sinal

a ser digitalizado é uniforme, então a relação sinalruído em relação ao ruído de quantização é o

melhor possível. Mas, isso não é frequentemente o

caso, pois é comum para passar o sinal através da

sua função de distribuição cumulativa (CDF), antes

da quantização. Isto é bom porque as regiões que

são mais importantes sejam quantizadas com uma

melhor resolução. No processo de-quantização

(retirar a quantização), o CDF inverso é necessário.

Este é o mesmo princípio por trás do compressores

utilizado em alguns gravadores de fitas magnéticas

e outros sistemas de comunicação, e está

relacionada com a entropia de maximização.

Por exemplo, um sinal de voz tem uma distribuição

Laplaciano. Isto significa que a região em torno dos

níveis mais baixos, perto de 0, tem mais informação

do que as regiões com maior amplitude. Devido a

isso, ADCs logarítmicas são muito comuns em

sistemas de comunicação de voz para aumentar o

alcance dinâmico dos valores representáveis,

mantendo a fidelidade granular fina na região de

baixa amplitude.

Precisão

Os ADC´s tem várias fontes de erros. Erro de

Quantização (supondo que o dispositivo está

destinado a ser linear) e não-linearidade são

intrínsecos a qualquer conversão analógica-digital.

Há também o chamado erro de abertura que é feito

quando um jitter (variação rápida) de clock é

mostrada na digitalização de um sinal com variação

de tempo (não é um valor constante).

Esses erros são medidos em uma unidade

chamada LSB, que é uma abreviação de bit menos

significativo. No exemplo acima de um conversor de

8bit´s, um erro de um LSB é 1/256 da gama

completa de sinal, ou cerca de 0,4%.

170

Erro de abertura

Imagine que estamos digitalizando uma onda

senoidal x ( t ) = A sin (2ð f 0 t ) . Desde que a

amostragem de tempo real de incerteza devido ao

clock jitter é Ä t , o erro causado por este fenômeno

pode ser estimada como.

O erro é zero para a DC, pequeno em baixas

frequências, mas significativa quando as

frequências altas têm grandes amplitudes. Este

efeito pode ser ignorado se for afogada pela erro de

quantização . requisitos Jitter pode ser calculado

através da seguinte fórmula:, Onde q é um número

de bits ADC.

ADC- Resolução

A tabela da página seguinte, mostra que não vale a

pena usar um preciso ADC de 24 bits para

gravação de som, se não houver um clock com jitter

(tremulação) ultra baixo. Deve-se considerar, tendo

em conta este fenômeno antes de escolher um

ADC.

O jitter de clock é causada por ruído de fase. A

resolução de ADCs com uma largura de banda de

digitalização entre 1 MHz e 1 GHz é limitada pela

instabilidade.

Quando a amostragem de sinais de áudio é de 44,1

kHz, o filtro anti-aliasing deve ter eliminado todas as

frequências acima de 22kHz. A frequência de

entrada (neste caso, 22 kHz), com a frequência de

clock do ADC, é o fator determinante no que diz

respeito à instabilidade de desempenho.

Taxa de amostragem

O sinal analógico é constante em um tempo, sendo

necessário converter isso em um fluxo de valores

FONTES - AMPLIF. DE POTÊNCIA - VALVULAS - OPERACIONAIS - ELETRÔNICA DIGITAL

ELETRÔNICA