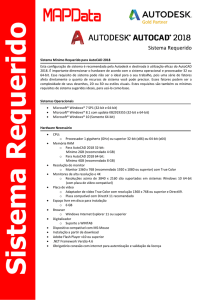

Projetos de Sistemas Digitais

com VHDL – Parte I

Modelamento Comportamental

Prof. Dr. Leonardo Mesquita

Departamento de Engenharia Elétrica

DEE/FE-G/UNESP

Versão 1.0 - 2005

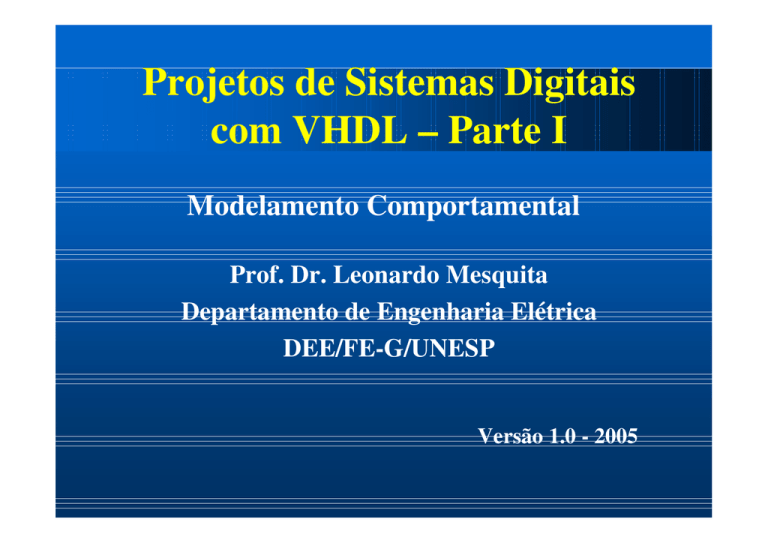

Estilos de Modelamento

A melhor forma de visualizar o que representa um estilo

de modelamento é analisar o diagrama Y proposto por

Gajski-Kbun.

Comportamental

Estrutural

Fisica

Estilo de Modelamentoestrutural

Descreve um sistema digital pela especificação das

interconexões dos componentes que compõem o

sistema.

Estilo de Modelamentoestrutural

A função entrada/saída está implicitamente definida,

pois as funções de entrada/saída dos componentes

virtuais podem ser obtidas, e como tem-se o

diagrama de conexões pode-se definir a relação entre

entrada/saída da descrição como um todo.

Estilo de Modelamentocomportamental

Define a função de entrada/saída especificando um

conjunto de funções de transferências matemáticas.

A descrição comportamental define o que um projeto

digital faz, mas não necessariamente como o projeto é

implementado.

Estilo de Modelamento

Diferenças entre o modelamento VHDL usando

estilo estrutural ou comportamental.

Estilo de Modelamento

I.

II.

Descrição da interface é idêntica.

Modelamento estrutural

•

Relação de entrada/saída é realizada usando

instrução de posicionamento de componente.

III. Modelamento comportamental

•

Usa uma instrução de atribuição de sinal

para implementar a relação de entrada/saída

do sistema.

Estilo de Modelamentocomportamental

Modelo VHDL

Comportamental

Estrutural

Algorítmo

Data flow

Conditional Concurrent Signal

Assigment Statement

A forma básica da instrução é:

Exemplo:

Conditional Concurrent Signal

Assigment Statement

A forma completa da instrução é:

Condition representa uma expressão booleana.

Conditional Concurrent Signal

Assigment Statement

• A opção ELSE é opcional, ou seja, essa

instrução pode ser reduzida a uma simples

instrução concorrente de atribuição de sinal.

• A instrução é executada sequencialmente.

• As condições devem ser expressões

booleanas, logo os operandos desta

expressão devem ser do tipo booleano

(verdadeiro ou falso).

Conditional Concurrent Signal

Assigment Statement

Modelo VHDL de um circuito multiplexador 2X1

usando instrução condicional de sinal.

Relational Operator

Operadores lógicos: not, and, or, nand, nor, xor, xnor*

- Operam com dados do tipo bit ou boolean.

- bit: representa informação binária sendo usado

para expressar operações de álgebra de chaveamento.

- boolean: representa valor verdade (verdadeiro

ou falso) sendo usado para expressar condições.

Relational Operator

Os operandos são binários e produz o resultado do tipo

boolean (verdadeiro ou falso).

- São usados para testar uma dada situação.

Operador

Definição

=

Igualdade

/=

Diferente

<

Menor

<=

Menor ou igual

>

Maior

>=

Maior ou igual

Relational Operator

A ordem de prioridade dos operadores usados na

linguagem são mostrados na tabela abaixo:

not

= /= < <= > >=

and or nand nor xor xnor*

xnor : VHDL’93.

Select Concurrent Signal

Assignment Statement

A syntax da instrução:

Select Concurrent Signal

Assignment Statement

I.

Discriminant

•

II.

Tipo que possua valores discretos, ou seja, um

conjunto finito de valores que possam ser

contados.

Choices

•

Todos os valores possiveis para o objeto

discriminado.

III. Expression

•

Valor ou espressão que será colocado na saída

quando uma determinada condição for

verdadeira.

Select Concurrent Signal

Assignment Statement

Select Concurrent Signal

Assignment Statement

Quando o discriminante possui muitos valores

possiveis pode-se usar características da linguagem

para reduzir o código.

Select Concurrent Signal

Assignment Statement

I.

Expression1 when b”000”,

•

II.

Expression1 será obtido quando comando for igual a 000.

Expression2 when b”010” to b“100”,

•

Expression2 será obido quando comando for igual a 010,

011 e 100.

III. Expression3 when b”001”|b”101”,

•

Expression3 será obtida quando comando for igual a 001 e

101.

IV. Expression4 when others;

•

Expression4 será obtida para todas as outras possibilidades

do sinal comando.

Bit_Vector

• Tipo pré-definido de informação sendo um

arranjo (vetor) de dados.

• Um arranjo de dados em VHDL possui três

características fundamentais:

• Tipo dos elementos que o compõem;

• O comprimento do arranjo;

• Indice.

Bit_Vector

• Informação é do tipo BIT.

• O comprimento do arranjo não é definido

sendo que o usuário tem liberdade de

estabelecer o mesmo.

• Os indíces são números naturais.

Bit_Vector

Elementos individuais podem ser acessados usando-se

o seu indíce individual. Exemplo:

i(3): bit 3 do sinal previamente descrito.

Bit_Vectorvalor

Para condensar a representação de sinais do tipo

bit_vector pode-se representar a informação binária

na forma octal ou hexadecimal.

Símbolo

B

O

X

Base

Binário

Octal

Hexadecimal

X”FA” = B”11111010”

O”37”= B”011111”