Guião 2

Portas de Entrada/Saı́da

João Paulo Sousa

[email protected]

2.1

2.2

Introdução e objectivos . . . . . . . . . . . . . . .

Constituição interna e modo de funcionamento

2.2.1 Portas P1 e P3 . . . . . . . . . . . . . . . . . . .

2.2.2 Portas P0 e P2 . . . . . . . . . . . . . . . . . . .

2.3 Interface com o exterior . . . . . . . . . . . . . .

2.3.1 Caracterı́sticas eléctricas das portas . . . . . . .

2.3.2 Entradas simples e com isolamento . . . . . . . .

2.3.3 Saı́da sem isolamento para um LED . . . . . . .

2.3.4 Saı́das com isolamento óptico . . . . . . . . . . .

2.1

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

. . . . . .

. . . . . .

. . . . . . .

. . . . . . .

. . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

. . . . . . .

1

2

2

3

3

3

4

5

5

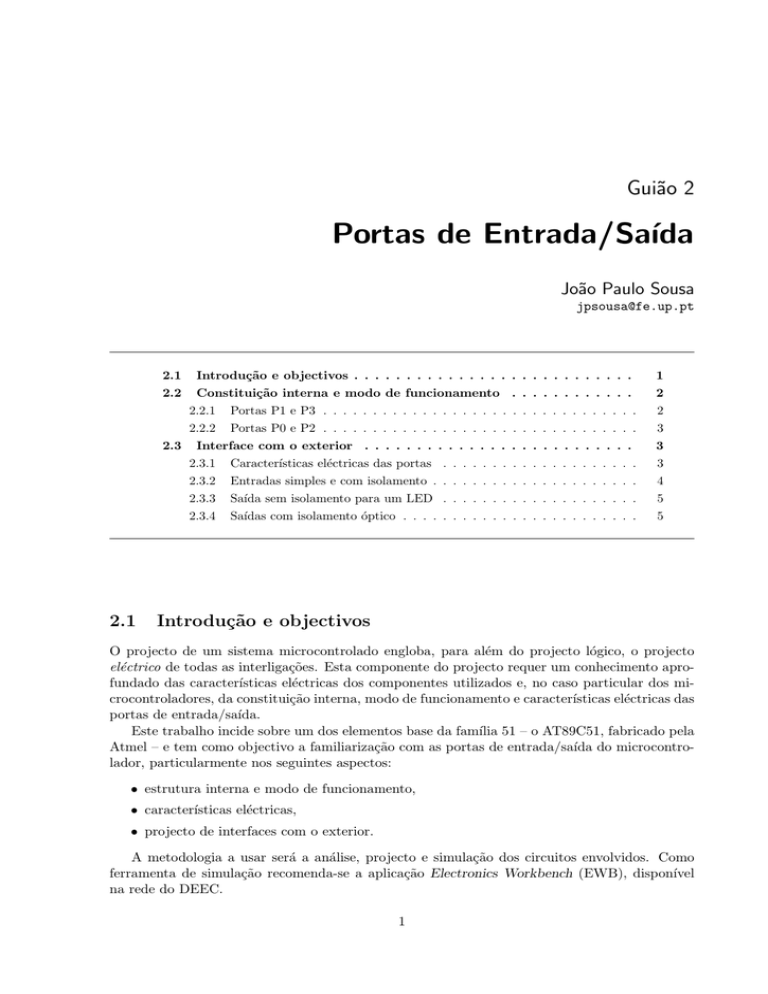

Introdução e objectivos

O projecto de um sistema microcontrolado engloba, para além do projecto lógico, o projecto

eléctrico de todas as interligações. Esta componente do projecto requer um conhecimento aprofundado das caracterı́sticas eléctricas dos componentes utilizados e, no caso particular dos microcontroladores, da constituição interna, modo de funcionamento e caracterı́sticas eléctricas das

portas de entrada/saı́da.

Este trabalho incide sobre um dos elementos base da famı́lia 51 – o AT89C51, fabricado pela

Atmel – e tem como objectivo a familiarização com as portas de entrada/saı́da do microcontrolador, particularmente nos seguintes aspectos:

• estrutura interna e modo de funcionamento,

• caracterı́sticas eléctricas,

• projecto de interfaces com o exterior.

A metodologia a usar será a análise, projecto e simulação dos circuitos envolvidos. Como

ferramenta de simulação recomenda-se a aplicação Electronics Workbench (EWB), disponı́vel

na rede do DEEC.

1

Ainda que de nı́vel introdutório, assume-se a existência de conhecimentos prévios sobre esta

familia de microcontroladores. Como elementos de estudo recomendam-se [2, páginas 40 a 43],

[3, páginas 565 e seguintes] e [4, páginas 151 e seguintes] onde estes assuntos estão apresentados

em detalhe.

2.2

Constituição interna e modo de funcionamento

2.2.1

Portas P1 e P3

Todos os bits da porta P3 e alguns bits da porta P1, para além de funcionarem como bits de

entrada/saı́da, têm uma função alternativa, apresentada na tabela 2.1.

Bit

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

Função alternativa

Entrada de dados para a porta série (RxD)

Saı́da de dados da porta série (TxD)

Entrada de interrupção (INT0)

Entrada de interrupção (INT1)

Entrada de contagem de impulsos (T0)

Entrada de contagem de impulsos (T1)

Saı́da de controlo de escrita na memória de dados externa (WR)

Saı́da de controlo de leitura da memória de dados externa (RD)

P1.0

P1.1

Entrada de contagem de impulsos (T2)

Entrada para captura/recarregamento de valores (T2EX)

Tabela 2.1: Funções alternativas das portas P3 e P1

LR

Barramento interno

Barramento interno

Na figura 2.1 estão representadas as células de entrada/saı́da associadas a pinos sem e com

função alternativa. Os primeiros são constituı́dos simplesmente por um flip-flop, um amplificador

de saı́da em dreno aberto (MOSFET de canal N) com pull-up interno e um amplificador de

entrada; os segundos possuem portas lógicas adicionais que permitem encaminhar a função

alternativa do interior para o exterior do microcontrolador e vice-versa. A estrutura básica de

Vcc

D

ER

Q

Clk /Q

Pino

SA

LR

Vcc

D

ER

Q

Pino

Clk /Q

LP

EA

LP

SUC0203-02A

SUC0203-02B

(a) Pino sem função alternativa

(b) Pino com função alternativa

Figura 2.1: Células de entrada/saı́da associadas a pinos sem e com função alternativa

uma porta dispõe de três sinais de controlo que permitem: a escrita no registo (ER), a leitura

do registo (LR), e a leitura do pino (LP). Estes sinais internos são activados por instruções

especı́ficas do microcontrolador; por exemplo, a instrução MOV P1.7,C coloca o valor da flag

carry no bit mais significativo do barramento interno e seguidamente actua o sinal ER da célula

associada ao pino P1.7 para que esse valor seja transferido para o registo e, consequentemente,

2

para o pino associado. Esta estrutura permite sempre escrever e ler o registo interno mas só

permite ler o pino se o registo interno estiver no nı́vel lógico alto. Porquê?

Os sinais SA e EA – respectivamente saı́da alternativa e entrada alternativa – permitem

encaminhar a função alternativa do interior para o exterior do microcontrolador (sinal SA) e viceversa (sinal EA). Obviamente só existem nas células associadas a pinos com função alternativa.

Repare que só é possı́vel usar a função alternativa (seja ela de entrada ou de saı́da) se o registo

interno estiver no nı́vel lógico alto. Porquê?

2.2.2

Portas P0 e P2

A porta P0 pode funcionar como barramento de dados, multiplexado temporalmente com a

metade menos significativa do barramento de endereços, e a porta P2 como metade mais significativa do barramento de endereços. Em alternativa a estas funções ambas funcionam como

portas de entrada/saı́da normais. Confirme [2, pág. 40–41] que a porta P0 quando funciona

como porta de entrada/saı́da não tem pull-up interno. Que implicações tem esse facto no seu

modo de funcionamento?

2.3

Interface com o exterior

2.3.1

Caracterı́sticas eléctricas das portas

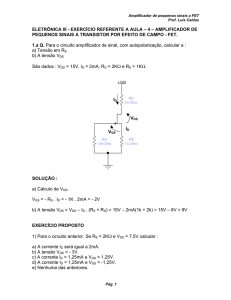

As caracterı́sticas eléctricas das portas do microcontrolador AT89C51 estão apresentadas na

tabela 2.2 e na figura 2.2. Se as condições de validade não forem verificadas os valores dos parâParâmetro

VIH

VIL

IIH

IIL

Valor

1.9V

0.9V

≈0

50µA

Observações e condições de validade

Valor mı́nimo para ser considerado um “1”

Valor máximo para ser considerado um “0”

VIL = 0.45V

VOH

VOH

VOH

VOL

4.5V

3.75V

2.4V

0.45V

IOH (debitada) inferior a 10µA (80µA para P0)

IOH (debitada) inferior a 25µA (300µA para P0)

IOH (debitada) inferior a 60µA (800µA para P0)

IOL (absorvida) inferior a 1.6mA (3.2mA para P0)

5

VOL - Tensão de saída no nível baixo (V)

VOH - Tensão de saída no nível alto (V)

Tabela 2.2: Caracterı́sticas eléctricas das portas para Vcc=5V

4

Portas P1, P2 e P3

3

2

0

10

20

30

40

50

60

70

80

90

100

2

1

Portas P1, P2 e P3

0

0.01

0.1

1

Porta P0

10

100

IOL - Corrente absorvida pela saída no nível baixo (mA)

IOH - Corrente debitada pela saída no nível alto (µA)

(a)

(b)

Figura 2.2: Curvas tensão-corrente quando as portas funcionam como saı́da

metros não são garantidos mas o circuito poderá ainda funcionar correctamente. Por exemplo,

3

uma corrente absorvida por uma saı́da superior a 1.6mA no nı́vel lógico “0” significa apenas que

a tensão nesse pino vai ser superior a 0.45V o que, por si só, não significa que o circuito a jusante

deixe de funcionar correctamente; tudo dependerá do que lá estiver ligado.

Por simples inspecção da figura 2.2 facilmente se conclui que a capacidade de absorver corrente é muito superior à capacidade de debitar corrente. Esta constatação é de grande importância no projecto de interfaces de saı́da.

Com base na curva tensão-corrente no nı́vel alto – figura 2.2(a) – estime um valor para a

resistência de pull-up. Na verdade não se trata de uma simples resistência mas sim de um

circuito activo com vários transı́stores MOSFET de canal P. Qual o motivo porque não existe

curva para a porta P0?

2.3.2

Entradas simples e com isolamento

Uma entrada digital sem isolamento é o circuito de interface mais simples mas infelizmente conduz a frequentes erros de projecto. Na figura 2.3 estão representadas quatro configurações para

ligar um interruptor (sensor) a uma porta de entrada mas nem todas funcionam correctamente.

8??

8??

8??

10k

Pino

Pino

4k7

Pino

Pino

SUC0203-02C

(a)

SUC0203-02D

SUC0203-02F

(b)

(c)

SUC0203-02E

(d)

Figura 2.3: Configurações para uma interface de entrada sem isolamento

Analise os circuitos e, se necessário, recorra ao simulador EWB para determinar qual (ou

quais) são as correctas. Explique porquê.

Considerando as caracterı́sticas de entrada apresentadas na secção anterior, que comentários

se podem tecer sobre o valor da resistência de pull-down da configuração (b) e da resistência de

pull-up da configuração (c)? De entre as configurações que funcionam qual é a mais eficiente em

termos energéticos?

Quando se trabalha em ambientes onde exista o perigo de aparecimento de sobre-tensões

induzidas ou de um modo geral sempre que exista uma grande diferença entre as tensões de

funcionamento dos circuitos exteriores e do microcontrolador, justifica-se uma entrada digital

com isolamento. A figura 2.4 representa uma configuração de princı́pio para ligar um interruptor

(sensor) a uma porta de entrada com isolamento óptico.

8??

RP

Pino

4N25

RD

"8

SUC0203-02G

Figura 2.4: Interface de entrada com isolamento óptico

Calcule o valor da resistência RD, de polarização do LED. Esse valor depende das caracterı́s4

ticas eléctricas do opto-acoplador (CTR – current transfer ratio, coeficiente de transferência de

corrente) e, obviamente, da tensão de funcionamento dos circuitos exteriores pelo que o projecto

do circuito apresentado requer o conhecimento dessa tensão (24V neste caso). A resistência RP

é sempre necessária? Porquê?

Nos casos em que se pretende uma gama alargada de tensões de funcionamento este circuito

não funciona de forma eficiente. Porquê? Apresente uma solução para uma entrada isolada

que permita valores de VOH compreendidos entre 10V e 50V. Sugestão: utilize uma fonte de

corrente com base num transı́stor JFET. Como se poderia proteger esta entrada contra inversões

de polaridade da alimentação dos circuitos exteriores?

Comprove a validade das suas soluções recorrendo ao simulador EWB. Para representar o

opto-acoplador poderá usar uma fonte de corrente controlada por corrente.

2.3.3

Saı́da sem isolamento para um LED

A implementação de uma saı́da digital para um LED é também um circuito de interface simples

que conduz a erros de projecto frequentes. A figura 2.5, representa quatro configurações para

ligar um LED (ou outra carga que consuma uma corrente da mesma ordem de grandeza) a uma

porta do microcontrolador mas nem todas funcionam correctamente. Em face das caracterı́sticas

8??

Pino

RP

RP

Pino

SUC0203-02J

SUC0203-02H

(a)

(b)

RC

Pino

RC

8??

Pino

RB1

RB

8??

RB2

SUC0203-02I

SUC0203-02K

(c)

(d)

Figura 2.5: Interfaces de saı́da simples

de saı́da das portas determine, justificando, quais as configurações correctas. Se necessário

recorra ao simulador EWB para confirmar as suas previsões. Para simplificar a simulação deve

substituir o transistor MOSFET por um inversor CMOS com saı́da em dreno aberto (HC-OD).

Com base nas configurações tipo apresentadas, projecte uma interface de saı́da para um LED

de baixo consumo (ID = 3mA, VD = 1.1V ) e outra para uma lâmpada incandescente (6V /5W ).

Tenha o cuidado de não ultrapassar a corrente máxima admissı́vel nas portas [1, pág. 37]. Os

parâmetros de saı́da da porta são afectados?

2.3.4

Saı́das com isolamento óptico

O isolamento óptico justifica-se agora pelas caracterı́sticas da carga. No caso de um relé – figura

2.6(a) – o comportamento indutivo da carga poderá fazer aparecer picos de tensão elevados nos

momentos de comutação.

A configuração de princı́pio apresentada não apresenta qualquer novidade. O dı́odo em

paralelo com o enrolamento do relé é necessário para possibilitar um caminho de fuga para a

energia armazenada na bobina nos momentos em que esta deixa de ser actuada.

5

No caso de uma carga funcionando na rede eléctrica de 230V a necessidade de isolamento

é obvia. A configuração de princı́pio mais simples – figura 2.6(b) – utiliza um opto-triac. A

desvantagem desta configuração é que não existe a garantia de que a comutação se faça nos

instantes em que a tensão da rede eléctrica passa por zero de modo a minimizar a interferência

electromagnética e, no caso de a carga ser uma lâmpada incandescente, maximizar o tempo de

vida do filamento.

Vcc

8??

V+

RP

RC

RP

Pino

Pino

SUC0203-02M

120

RB

4N25

SUC0203-02N

(a) Carga indutiva

BT139

MOC3020

1k

10nF

39

!8=?

(b) Carga a 230Vac

Figura 2.6: Interfaces de saı́da com isolamento

Com a ajuda do simulador EWB projecte uma interface para um relé de 12V supondo que

a corrente para o fazer atracar é de 24mA. Sabendo que a corrente necessária para o manter

atracado é apenas 1/4 desse valor que alterações ao projecto sugere?

Como projecto integrador de todo este guião apresente uma interface que permita a um

microcontrolador acender e apagar um conjunto de lâmpadas incandescentes totalizando 1kW

de potência, ligadas à rede eléctrica de 230Vac com funcionamento sincronizado pelos instantes

em que a tensão da rede passa por zero. Sugestão: use uma saı́da isolada opticamente para

controlar a carga e uma entrada isolada opticamente para detectar os instantes em que a tensão

da rede passa por zero.

Bibliografia

[1] ATMEL Semiconductors. AT89C51, 8 Bit Microcontroller with 4K Bytes Flash – Product

Data Sheet, Dezembro 1997.

[2] ATMEL Semiconductors. AT89 Series Hardware Description, Dezembro 1998.

[3] Paul Horowitz and Winfield Hill. The Art of Electronics. Cambridge University Press, 2

edition, 1990. ISBN 0–52–137095–7. Existe na biblioteca.

[4] Thomas Schultz. C and the 8051: building efficient Applications, volume 2. Prentice Hall,

1999. ISBN 0–13–521121–2. Ainda não existe na biblioteca.

6

Anexo: relembrando as fontes de corrente com JFET. . .

Para valores baixos de vDS , isto é, inferiores a vGS − VP , a relação entre iD e vDS num transistor

JFET é praticamente linear (zona ohmica) mas à medida que vDS sobe o transistor entra na

zona de saturação onde iD pouco depende de vDS mas praticamente só de vGS . Nesta zona o

transistor funciona como uma fonte de corrente controlada por vGS . É o que se passa no circuito

apresentado. A equação que rege o funcionamento do transistor na zona de saturação é:

vGS 2

= IDSS 1 −

(1 + λvDS )

VP

2

vGS

≈ IDSS 1 −

VP

iD

10..30V

ID

4N25

VGS

RS

(2.1)

ou, explicitando em ordem a vGS :

s

vGS = VP

1−

SUC0203-02P

iD

!

(2.2)

IDSS

com vGS = −RS × iD , imposta pelo circuito.

(2.3)

O valor de RS determina-se por (2.3) depois de impor um valor para a corrente iD e calcular por

(2.2) o valor de vGS correspondente. Os gráficos, retirados da folha de caracterı́sticas, permitem

conhecer os valores tı́picos de VP e IDSS para 3 transı́stores JFET de canal N de uso comum.

MGE789

6

ID

(mA)

5

MGE787

15

4

MGE788

30

ndbook, halfpage

dbook, halfpage

ndbook, halfpage

ID

(mA)

ID

(mA)

10

20

5

10

3

2

1

0

−4

−2

0

VGS (V)

0

−4

(a) BF245A

−2

VGS (V)

0

0

−10

(b) BF245B

MBH555

6

ID

(mA)

5

MBH554

30

MBH553

15

dbook, halfpage

ID

(mA)

ID

(mA)

VGS = 0 V

4

0

VGS (V)

(c) BF245C

dbook, halfpage

dbook, halfpage

−5

20

VGS = 0 V

10

VGS = 0 V

−0.5 V

3

−1 V

−0.5 V

2

10

−1 V

1

−1.5 V

0

0

10

VDS (V)

(d) BF245A

20

0

−1 V

5

−2 V

0

10

−2 V

−4 V

−2.5 V

VDS (V)

(e) BF245B

−1.5 V

−3 V

20

0

0

10

VDS (V)

(f) BF245C

Figura 2.7: Caracterı́sticas de entrada (a,b,c) e de saı́da (d,e,f) da série BF245

7

20