ELT413 – ELETRÔNICA ANALÓGICA II

ENGENHARIA ELÉTRICA

O

LABORATÓRIO N 2: AMPLIFICADOR EC (RETAS DE CARGA DC E AC, PONTO DE OPERAÇÃO ÓTIMO)

OBJETIVOS

Conceituar retas de carga DC e AC

Analisar amplificadores de potência classe A e

determinar o ponto de operação ótimo.

Analisar amplificador emissor comum utilizando

transistor PNP.

Atenção: apresentar, no início da aula de laboratório, os cálculos teóricos com as retas de carga DC

e AC do circuito. Analisar o circuito:

a) Sem carga e

b) Com carga RL=2kΩ

I - RETA DE CARGA DC E AC

A reta de carga DC é definida pela fonte VCC e

pelas resistências DC do coletor e do emissor

RDC = RC + RE

VCC = VCE + RDC .I C

VCE = VCC − RDC .I C

I C = (VCC − VCE ) / RDC

Dois pontos da reta de carga DC são

Para amplificadores de grandes sinais o ponto

de operação deve ficar no meio da reta de carga

AC para permitir a máxima amplitude sem ceifamento (máxima compliance).

VCEQ (OT ) =

I CQ (OT ) =

Rac

VCC

Rac + Rdc

VCC

Rac + Rdc

Nesta condição os ceifamentos de corte e de saturação ocorrerão simultaneamente.

Vce pp max = 2.VCE(Q)Ot

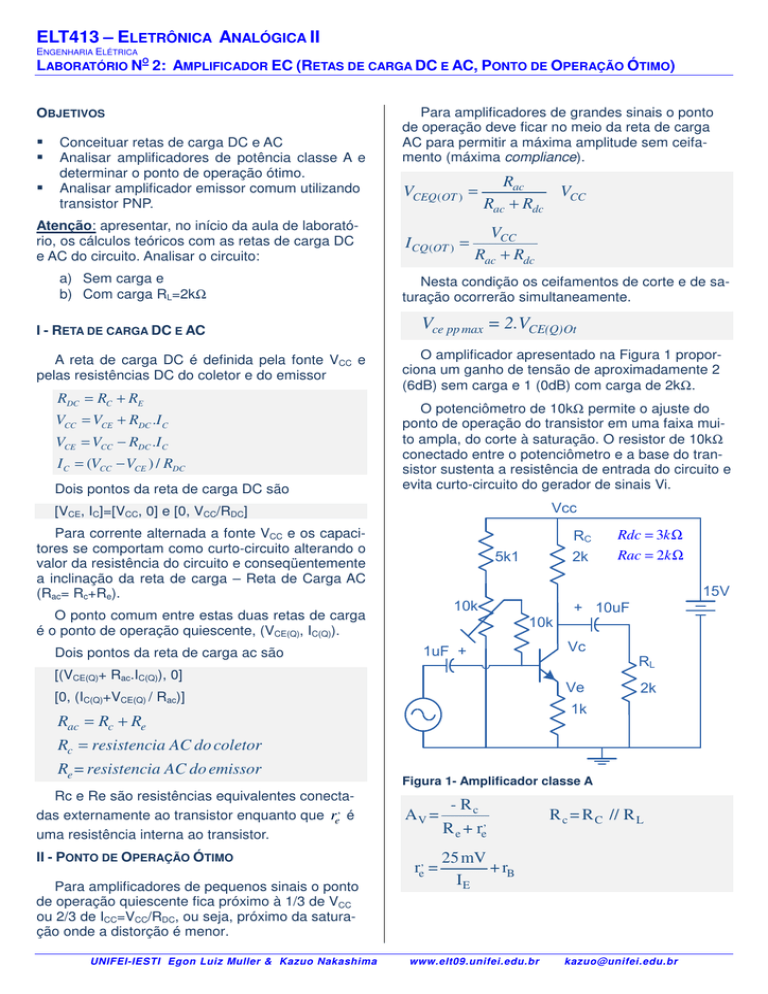

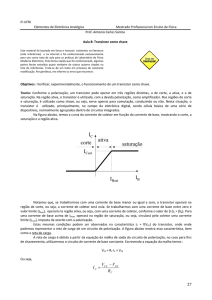

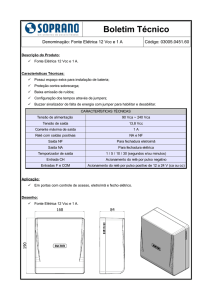

O amplificador apresentado na Figura 1 proporciona um ganho de tensão de aproximadamente 2

(6dB) sem carga e 1 (0dB) com carga de 2kΩ.

O potenciômetro de 10kΩ permite o ajuste do

ponto de operação do transistor em uma faixa muito ampla, do corte à saturação. O resistor de 10kΩ

conectado entre o potenciômetro e a base do transistor sustenta a resistência de entrada do circuito e

evita curto-circuito do gerador de sinais Vi.

Vcc

[VCE, IC]=[VCC, 0] e [0, VCC/RDC]

Para corrente alternada a fonte VCC e os capacitores se comportam como curto-circuito alterando o

valor da resistência do circuito e conseqüentemente

a inclinação da reta de carga – Reta de Carga AC

(Rac= Rc+Re).

RC

5k1

15V

10k

O ponto comum entre estas duas retas de carga

é o ponto de operação quiescente, (VCE(Q), IC(Q)).

Dois pontos da reta de carga ac são

2k

Rdc = 3k Ω

Rac = 2k Ω

+ 10uF

10k

1uF +

[(VCE(Q)+ Rac.IC(Q)), 0]

Vc

RL

Ve

[0, (IC(Q)+VCE(Q) / Rac)]

2k

1k

Rac = Rc + Re

Rc = resistencia AC do coletor

Re = resistencia AC do emissor

Rc e Re são resistências equivalentes conectadas externamente ao transistor enquanto que re, é

uma resistência interna ao transistor.

II - PONTO DE OPERAÇÃO ÓTIMO

Para amplificadores de pequenos sinais o ponto

de operação quiescente fica próximo à 1/3 de VCC

ou 2/3 de ICC=VCC/RDC, ou seja, próximo da saturação onde a distorção é menor.

UNIFEI-IESTI Egon Luiz Muller & Kazuo Nakashima

Figura 1- Amplificador classe A

AV =

re, =

- Rc

R e + re,

R c = R C // R L

25 mV

+ rB

IE

www.elt09.unifei.edu.br

[email protected]

Laboratório No2: Q ótimo

ELT413 - Eletrônica Analógica II

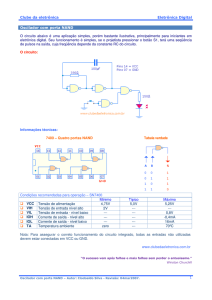

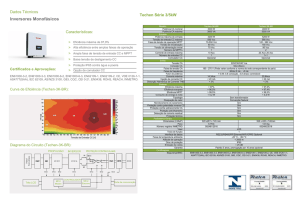

A Figura 2 apresenta a reta de carga DC e as retas de carga AC para VCE(Q) = 2V próximo à saturação, VCE(Q) = 12V próximo ao corte e VCE(Q) otimo = 6V

na condição de máxima amplitude do sinal de saída

sem ceifamento.

X=VCE 2V/DIV .

Y=IC 1mA/DIV

RDC=3k

Rac=2k

ICC=VCC/RDC

saturação ac

ac

tim

-o

ac

Rc

⋅ Vce(pp)

R ac

Ve(pp) =

Re

⋅ Vce(pp)

R ac

Vce(pp)max = 2.VCE(Q) Otimo

IV - GANHO DE TENSÃO MÁXIMO

Para aumentar o ganho de tensão do amplificador Emissor Comum (EC) devemos aumentar a relação entre a resistência do coletor e a resistência

do emissor.

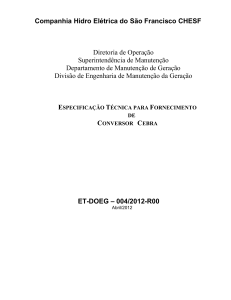

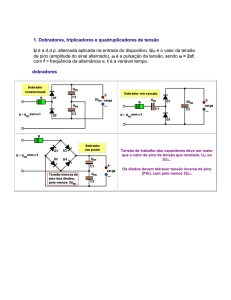

Uma solução é instalar um capacitor de desvio

em paralelo à resistência do emissor como mostra

a Figura 3.

o

ICC

5mA

Vc(pp) =

AV =

dc

-

Corte ac

Sat ac

Rc

re,

Esta solução proporciona o maior ganho de tensão para este circuito, porém apresenta forte distorção.

Vcc

VCC

15V

10k

Figura 2- Retas de carga DC e AC para o circuito da

Figura 1.

Neste exemplo particular, com o transistor polarizado próximo ao corte, VCEQ=12V, a amplitude

máxima de Vce sem ceifamento é 4 VPP , com ceifamento devido ao corte no semi-ciclo positivo para

transistor NPN e semi-ciclo negativo para transistor

PNP.

Com o transistor polarizado próximo à saturação, VCEQ=2V, a máxima amplitude de Vce sem ceifamento é 4 VPP , com ceifamento devido à saturação ocorrendo no semi-ciclo negativo para transistor NPN e semi-ciclo positivo para transistor PNP.

RC

2k

Rdc = 3k Ω

Rac = 1k Ω

15V

10k

+ 10uF

10k

Vc

1uF +

RL

2k

RE

CE

1k

100uF

Com o transistor polarizado no ponto Q ótimo a

amplitude máxima sem ceifamento é 12 VPP, ocorrento os ceifamentos por saturação e corte simultaneamente.

Figura 3 - EC com capacitor de desvio.

Vce corte ac = VCEQ + R ac . ICQ

A solução apresentada na Figura 4b é mais interessante uma vez que podemos ajustar o ganho de

tensão, atuando em RE2, sem alterar o circuito DC,

portanto sem alterar o ponto de operação do transistor.

Ic sat ac = ICQ + VCEQ / R ac

III - AMPLITUDE DA TENSÃO EM RL

A amplitude da tensão na carga RL é a mesma

do terminal do transistor onde ela está conectada,

coletor ou emissor, e é uma parcela proporcional

em relação à resistência AC total do circuito.

2

UNIFEI-IESTI

Egon Luiz Muller & Kazuo Nakashima

Para evitar esta distorção devemos instalar um

resistor no circuito ac do emissor. A Figura 4 apresenta duas soluções sem alterar o circuito DC.

A melhoria da linearidade é obtida com o sacrifício do ganho de tensão. Quanto maior for a resistência Re mais linear será o circuito e menor será o

ganho de tensão.

www.elt09.unifei.edu.br

[email protected]

Laboratório No2: Q ótimo

ELT413 - Eletrônica Analógica II

a) A tensão Vcc é pré-definida ou definida em função da tensão de saída desejada. O fator de

mérito do amplificador é obter o maior valor da

relação Vo-pp-max / Vcc

b) O ganho de tensão é definido pelo projeto.

Quanto maior for o ganho de tensão, maior será

a amplitude disponível na saída.

c) Quanto menor for a carga, ou seja, maior a relação RL/RC, maior será a amplitude da tensão

disponível na carga

d) Quanto maior a relação Rac/Rdc maior será a

amplitude disponível no sinal de saída. Esta relação diz respeito à relação RL/RC e ao capacitor

de desvio do emissor.

Figura 4 - EC linearizado, Av≅

≅-10

Atenção: Devido à necessidade de valor elevado de capacitância de desvio, esta solução deve

ser evitada para baixas freqüências. Considerar a

possibilidade de utilizar acoplamento direto como

os amplificadores diferenciais.

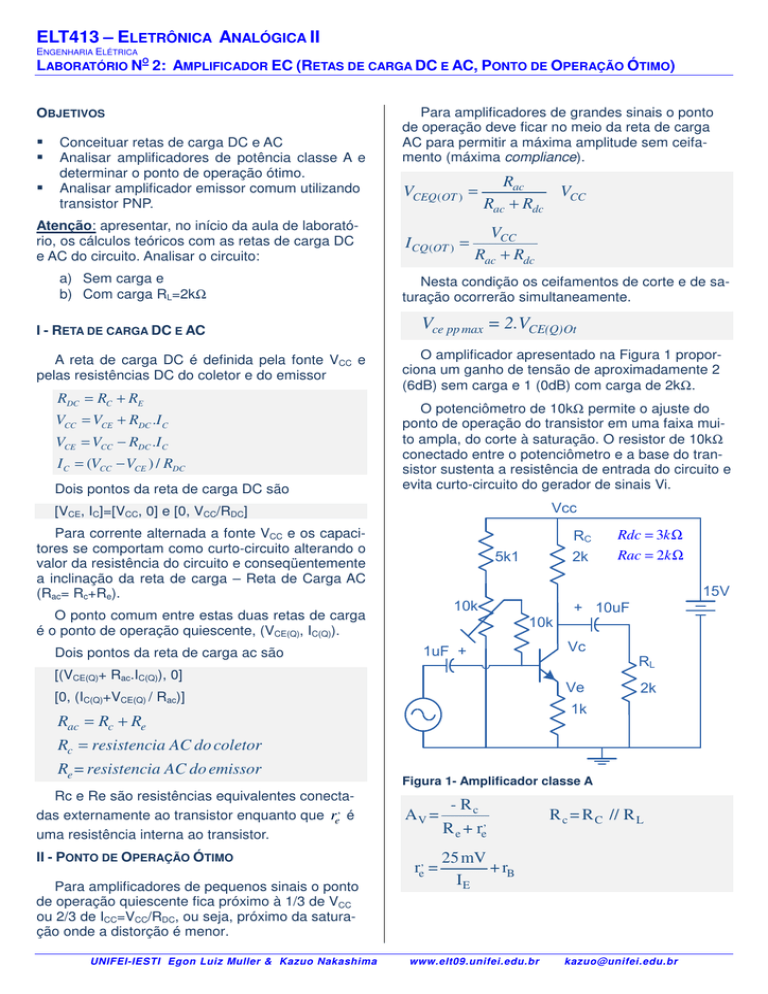

A solução apresentada na Figura 5 proporciona

o mesmo ganho de tensão que os circuitos apresentados na Figura 4, com maior “compliance” (devido à menor relação entre Rac e RDC) e sem a necessidade do capacitor de desvio; porém com menor estabilidade no ponto de operação devido ao

baixo valor de resistência dc no circuito do emissor.

Vcc

RC

2k

10k

Rdc = 2,1k Ω

Rac = 1,1k Ω

+ 10uF

10k

Vc

1uF +

RL

RE

100

Para uma carga extremamente leve, RL>>RC, teremos Rac≅Rdc, ou seja, Vce pp max ≅ VCC

Vc pp max =

Av

A v +1

VCC

p / Qot

Verificamos que quanto menor for o ganho de

tensão menor será a amplitude máxima disponível

em RL.

A relação Rac/Rdc tem grande influência na limitação da amplitude no sinal de saída. Esta relação

depende da relação RL/RC e da utilização do capacitor de desvio do emissor.

Vce pp max =2 VCE(Q)Ot

15V

10k

e) Nos amplificadores de grande sinal devemos polarizar o transistor no ponto Q ótimo, ou seja, o

ponto de operação deve ficar no centro da reta

de carga AC.

2k

Vce pp max

2 R ac

VCC

R ac +R dc

Rc

Vc pp max =

V

R ac ce pp max

=

A tensão pico a pico sem ceifamento disponível

no coletor do transistor é

Tabela 1- Vc pp max / VCC (valores aproximados Qot)

Figura 5- EC Av=-10 sem capacitor de desvio.

V – AMPLITUDE MÁXIMA DA TENSÃO DE SAÍDA

Nos amplificadores com acoplamento capacitivo,

a amplitude máxima disponível na carga depende

de: a) VCC, b) do ganho de tensão, c) da relação

RL/RC, d) da relação Rac/Rdc e e) do ponto de operação quiescente.

UNIFEI-IESTI

Egon Luiz Muller & Kazuo Nakashima

Av

RL>10.RC

RL=RC

1

0,50

0,4

2

0,66

0,5

5

0,83

0,587

10

0,91

0,625

www.elt09.unifei.edu.br

[email protected]

3

Laboratório No2: Q ótimo

ELT413 - Eletrônica Analógica II

A Figura 6 mostra que obtemos maior amplitude

sem ceifamento (maior compliance) se o ponto de

operação do transitor for ajustado no “ponto Q ótimo”.

A Figura 8 mostra que quanto menor a resistência RC maior será a amplitude disponível em RL, porém ao custo de um maior consumo de energia e

conseqüente redução da eficiência.

IC

VCC=15V

RC=1k; 2k; 5k

RL=2k

RE=0,1k

RDC=

Rac=

R

C=

1k

RC

=2k

RC=5k

VCE

Figura 6 – Ajuste no ponto de operação.

Se o ponto de operação estiver próximo ao corte, o ceifamento devido ao corte ocorrerá primeiro.

O sinal de saída será mais distorcido devido à influência maior de re. A única vantagem será o menor

consumo de energia para polarização do transistor.

Próximo à saturação a distorção é menor, porém o

consumo de energia é maior.

A Figura 7 mostra que quanto maior for o valor

da resistência RL (carga leve) maior será a amplitude disponível na saída. Nos três casos o ponto Q é

ótimo. Observe que o ponto de operação Q está no

meio da reta de carga AC.

IC

VCC=15V

RC=2k

RL=

RE=0,1k

RDC=2,1k

Rac=

VCC

Figura 8 – Reta de carga DC e retas de carga AC no

ponto ótimo. RDC variável e RL constante.

Durante o projeto geralmente a carga é prédefinida. O objetivo será, então, determinar qual o

valor de RC mais adequado.

Se não existir nenhuma outra restrição, um bom

critério para escolha de RC é adotar RC=RL.

Vc pp max/VCC ≅ 0,4 para Av=-1

Vc pp max/VCC ≅ 0,6 para Av=-10

Vce ppm max = 2.VCEQot

RC ≤RL 2.VCC /Vo pp - 2

V

VOPP ≤ CC

RC

+1

2.RL

(

)

V

RC ≤ 2.RL CC − 1

VOPP

Sugestão: vejam os projetos de amplificadores

operacionais “rail-to-rail” onde se consegue uma

excursão na tensão de saída de quase 100% de

VCC.

QOt

,2k

R L=0

R

L=

2k

RL

=2

0k

VCE

Figura 7 – Reta de carga DC e retas de carga AC no

ponto ótimo. RDC constante e RL variável.

4

UNIFEI-IESTI

Egon Luiz Muller & Kazuo Nakashima

www.elt09.unifei.edu.br

[email protected]

Laboratório No2: Q ótimo

ELT413 - Eletrônica Analógica II

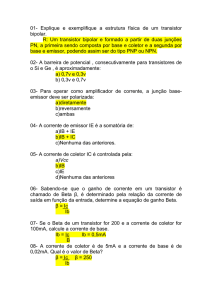

VI - AMPLIFICADOR EC COM TRANSISTOR PNP

Tabela 2- Ponto de operação e Ganho

Podemos construir quatro amplificadores idênticos utilizando os mesmos componentes passivos,

dois com transistor NPN e dois com transistor PNP.

RE

1k

100

10

1

0,1

A Figura 9 mostra os dois circuitos EC utilizando

transistor PNP. Observe que um circuito utiliza fonte

DC positiva e outro circuito uma fonte DC negativa.

RF1

RF2

VCC = − 15V

RF

200k

RC

2k

VC

Rdc=2,1kΩ

Rac=1,1kΩ

CO = 10µF

+

Vi +

VO

VB

RL

Ci

1µF

RE

100

hFE ≅ 165

ICQ

3,367 mA

4,322 mA

4,448 mA

4,462 mA

4,463 mA

Para permitir um ajuste no ponto de operação o

resistor RB deve ser substituído por resistor fixo de

20kΩ em série com um potenciômetro de no mínimo 200kΩ.

Podemos aumentar a resistência de entrada do

circuito se evitarmos a realimentação AC do coletor

para a base, ou seja, dividindo RB em duas partes e

instalando um capacitor de desvio.

2k

IC [mA]

IC =

VCC -VBE

RB

h FE

RF1

Vi

RF2

+

RE

100

VE

VCC = + 15V

Rdc=2,1kΩ

Rac=1,1kΩ

+ (R C + R E )

VCC = 15 V

VBE =0,7V

R C =2k Ω

RE = 0

R B = 200 k Ω

7,5

(4.28V ; 5.36mA ) hFE =300

(5.48V ; 4.76mA ) hFE =200

(7.85V ; 3.58mA ) hFE =100

5

VB

Ci

1µF

Av

0,975

9,26

59,73

131,2

149,0

VC CO =10µF

RF

200k

+

RC

2k

VO

0

RL

IC [mA]

5

2k

IC =

10

VCC = 15 V

VCC -VBE

RB

VBE =0,7V

+ (R C + R E )

R C =2k Ω

R E = 1k Ω

Figura 10- EC com transistor PNP (Av≅

≅-10)

1. Circuito simples.

2. Baixo consumo (corrente mínima para polarização).

3. Boa estabilidade do ponto de operação devido à

realimentação negativa DC.

4. Permite o ajuste do ganho de tensão sem alterar significantemente o ponto de operação.

15 V

Obs.: RB=300k

h FE

O circuito de polarização utilizado é por realimentação da tensão do coletor. Este tipo de polarização apresenta as seguintes vantagens:

VCE

R B = 300 k Ω

5

(4.28V ; 3.57mA ) hFE =300

(5.46V ; 3.18mA ) hFE =200

(7.85V ; 2.38mA ) hFE =100

5

10

VCE

15 V

Figura 11- Reta de carga DC e ponto de operação

O ganho de tensão pode ser ajustado alterando

apenas o resistor RE sem alteração significativa do

ponto de operação e da estabilidade deste ponto.

UNIFEI-IESTI

Egon Luiz Muller & Kazuo Nakashima

www.elt09.unifei.edu.br

[email protected]

5

Laboratório No2: Q ótimo

ELT413 - Eletrônica Analógica II

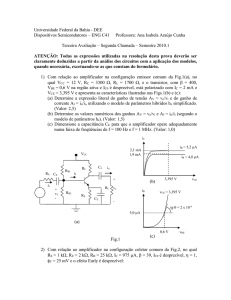

b) Para circuitos com polarização ajustável (circuito

da Figura 1).

VII - LABORATÓRIO

a) Para circuitos com polarização fixa (circuito da

Figura 10).

Desenhar a reta de carga DC e as retas de carga AC para o ponto Q ótimo (teórico) e para

ponto Q medido.

Calcular e/ou verificar experimentalmente Ganho de tensão e Amplitude máxima sem ceifamento

Ajustar o ponto de operação do transistor e medir ganho de tensão e amplitude máxima sem

ceifamento Vpp-max

Desenhar a reta de carga dc e as retas de carga ac para VCE(Q) = 3V, 12V e no ponto Q ótimo.

VCEQ

3

12

ICQ

Qot

Medido

mA

Av

VCEQ

V

ICQ

mA

Av

Vce

Vc

Vpp max

Ve

Vce

Vo

Vc

V pp max

Ve

Vo

Itajubá, MG, julho de 2016

6

UNIFEI-IESTI

V

Egon Luiz Muller & Kazuo Nakashima

www.elt09.unifei.edu.br

[email protected]