EE531W

-

Laboratório de Eletrônica Básica I

-

Prof. Anderson Spengler

Experiência 4: Relatório

Rodrigo de Castro Hernandes 092906

André Priolli Araujo

090393

Allan Gesner da Silva Nery 083186

Resultado Resultados do Exercício Preparatório da

quarta Experiência

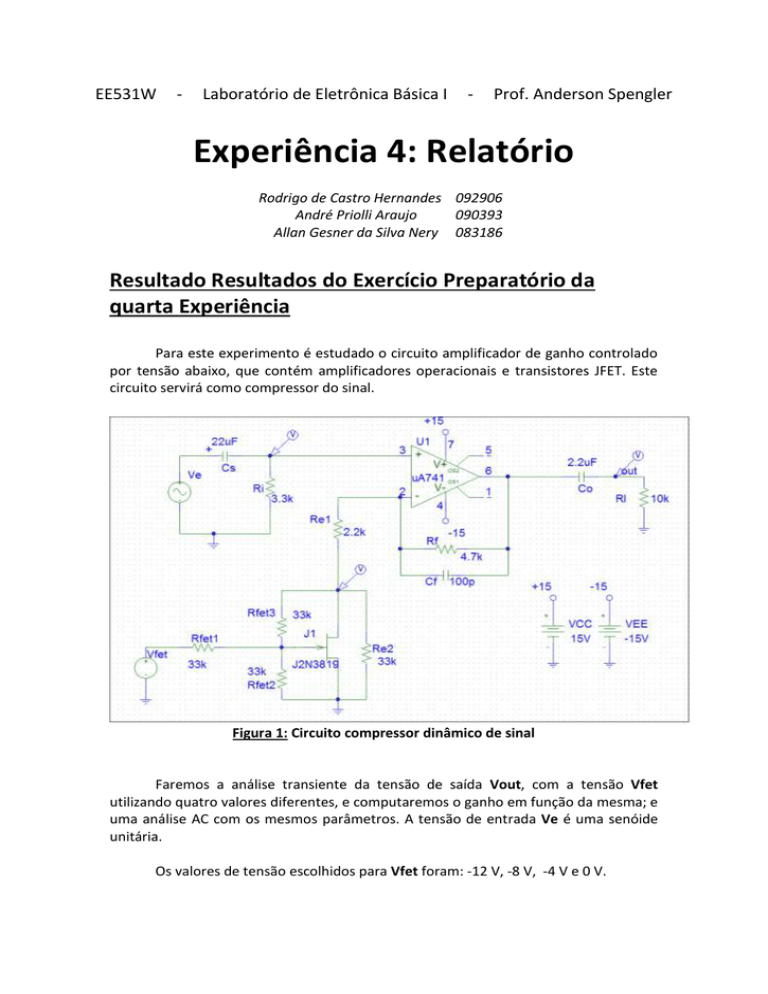

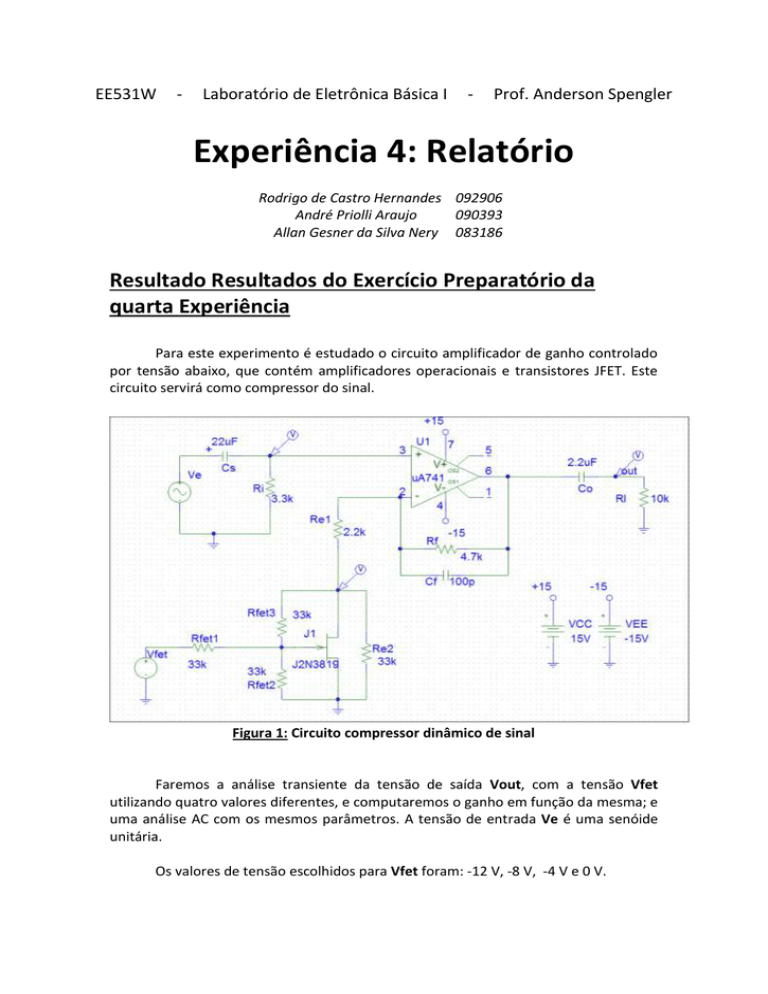

Para este experimento é estudado o circuito amplificador de ganho controlado

por tensão abaixo, que contém amplificadores operacionais e transistores JFET. Este

circuito servirá como compressor do sinal.

Figura 1: Circuito compressor dinâmico de sinal

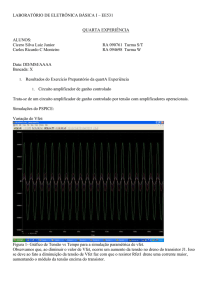

Faremos a análise transiente da tensão de saída Vout, com a tensão Vfet

utilizando quatro valores diferentes, e computaremos o ganho em função da mesma; e

uma análise AC com os mesmos parâmetros. A tensão de entrada Ve é uma senóide

unitária.

Os valores de tensão escolhidos para Vfet foram: -12 V, -8 V, -4 V e 0 V.

Figura 2: Análise de transiente do circuito compressor de tensão.

Através do gráfico percebemos que quando a tensão em Vfet é -12, o ganho é

muito pouco (aprox. 1,2 vezes a entrada) e quando muda para -8, o ganho aumenta

consideravelmente para aproximadamente 2,4 vezes o valor de entrada. Para os

valores de -4 e zero, o ganho do circuito é semelhante, com aproximadamente 3 vezes

o valor de entrada.

Figura 3: Análise AC do circuito compressor de tensão.

Para este gráfico percebe-se que os valores de freqüência em que o ganho é

máximo estão entre 50 Hz e 50 kHz, condizendo com sinais de som.

Circuito Analisado

Figura 4: Circuito compressor de sinal

O circuito compressor de sinal estudado contém, para os canais direito e

esquerdo:

Uma entrada (“IN L” ou “IN R”)

Um amplificador de ganho variável por potenciômetro – que neste

experimento foi fixado em ganho=2.

Um amplificador inversor, com retificação de meia-onda selecionando a parcela

negativa do sinal de entrada.

Ligado à saída deste amplificador-retificador, um capacitor que, sendo

carregado e lentamente descarregado, serve como um filtro de tensão.

Uma saída parcial (“OutDetL” ou “OutDetR”).

Um circuito compressor de sinal praticamente igual ao circuito estudado no

pré-relatório, cuja saída (“OutL” ou “OutR”) é a saída definitiva do circuito.

Este último componente tem como entrada Ve a senóide inicial com ganho

variado por potenciômetro (saída do 2º item, acima), e como entrada Vfet a saída

parcial (“OutDetL” ou “OutDetR”). Além disso, entre a entrada Base de seu transistor

JFET e o comum há uma entrada para Jumper, que se colocado gera um curto circuito

entre eles – fazendo o transistor ser cortado e, consequentemente, o ganho no

compressor ser constante.

Comportamento do Compressor de Sinal

Para verificar o comportamento geral do circuito, foram analisados os

transientes e medidos os ganhos em dois pontos cruciais dele: suas saídas parcial e

definitiva, utilizando o canal esquerdo.

A primeira medida, da saída parcial OutDetL, foi feita com “IN L” sendo uma

senóide de Vpp = 1V. O osciloscópio nos mostra que OutDetL é um sinal negativo

praticamente DC, como podemos ver na Figura 5 a seguir.

Figura 5: Forma de onda da saída parcial OutDetL.

Este sinal está no ânodo do Diodo retificador D2, e enxerga um capacitor , que

respectivamente retificam e filtram o sinal inconstante presente no cátodo do Diodo

D2, representado abaixo na Figura 6.

Figura 6: Forma de onda do sinal no cátodo.

Fizemos também, utilizando osciloscópio, gerador de tensão senoidal e o

software de aquisição, o gráfico que relaciona a saída OutDetL com a entrada IN L , na

Figura 7, revelando um ganho praticamente linear, conforme a figura abaixo:

Figura 7: Gráfico de OutDetL (ordenada) x IN L (abcissa).

As medidas na saída definitiva “OutL” foram realizadas primeiramente sem o

Jumper, o que nos mostrou um sinal de resposta distorcido do sinal de entrada, como

visto na Figura 8 a seguir.

Figura 8: Forma de onda deformada na saída OutL.

O ganho de OutL em relação a IN L também se mostrou variável, como visto no

gráfico da Figura 9, que teve seu comportamento grosseiramente ajustado para uma

reta.

Figura 9: Gráfico de ganho G (ordenada) x IN L (abcissa, Vpp).

Quando o Jumper foi colocado, estabeleceu-se um curto circuito entre a

entrada Base do transistor e o comum, fazendo com que Q1 seja cortado. A Figura 10

mostra o resultado experimental disto.

Figura 10: Gráfico de ganho G (ordenada) x IN L (abcissa, Vpp).

Como vemos na figura 10, o colocamento do Jumper faz com que o sinal fique

sem a deformação previamente encontrada, e o ganho seja constante. É como se toda

a parte do circuito que retifica, amplia e filtra o sinal para regular este ganho.