Universidade Federal de Itajubá

Instituto de Engenharia de Sistemas e Tecnologias da Informação

Engenharia da Computação

ELT403 – Eletrônica Aplicada II

Conversores de Dados

(Introdução e Conversores D/A)

Prof. Paulo C. Crepaldi

Prof. Leonardo B. Zoccal

Itajubá, Agosto de 2010

1

Considerações Gerais

Atualmente, é comum o uso de máquinas digitais (um computador pessoal,

por exemplo) para o controle e a supervisão de processos.

O processamento digital apresenta vantagens como a operação em tempo real

e a flexibilidade de mudanças que podem ser efetuadas por software.

Contudo, devemos ter em mente que os sinais provenientes deste processos

são sinais físicos e analógicos com temperatura, pressão, deslocamentos, etc.

Portanto, é necessário, antes de tudo, o uso de sensores e transdutores que irão

converter os sinais físicos em sinais elétricos. Não basta apenas esta

conversão para sinais elétricos mas, também, uma conversão adicional para

sinais elétricos que sejam corretamente interpretados pela máquina digital, ou

seja, é preciso o uso de conversores analógico-digitais (conversores A/D).

Se a máquina digital precisa intervir no processo, também é necessário um

caminho inverso de conversão, ou seja, os sinais digitais são convertidos em

sinais analógicos pelo uso de conversores digital-analógicos (conversores

D/A) e, na seqüência, entregues a circuitos especializados denominados de

atuadores. Os atuadores irão agir no processo de forma a se obter os

resultados desejados de operação.

2

Diagrama de blocos de um Sistema de Controle Digital

Sinal Elétrico

(analógico)

Sensores

Transdutores

Sinal Elétrico

(analógico)

Tratamento e

Condicionamento

Sinal Elétrico

(digital)

Conversão A/D

Sinal Elétrico

(digital)

Máquina Digital

Sinal Elétrico

(analógico)

Conversão D/A

Atuadores

Processo

(Variáveis Físicas: Pressão, Temperatura, etc)

O bloco de tratamento e condicionamento é fundamental para adequar

o sinal elétrico, proveniente dos sensores/transdutores, aos conversores

A/D. Suas principias funções são: Amplificação, Isolação,

Multiplexagem, Filtragem, Linearização e Excitação.

Os atuadores agem nos equipamentos presentes no processo. Os

atuadores mais comuns são dispositivos pneumáticos, hidráulicos e

eletro-eletrônicos de potência.

Neste curso, o objetivo será a análise dos conversores A/D e D/A.

3

Exemplo de um Sistema de Aquisição de Dados (PC-Based)

4

Exemplos de Sensores:

5

Exemplos de Sensores:

6

Exemplos de Sensores:

7

Exemplos de Sensores: Aplicações Biomédicas

8

Exemplos de Sensores: Aplicações Automotivas

9

Exemplos de Atuadores:

10

Exemplos de Atuadores:

11

Exemplos de Atuadores:

Atuadores Elétricos (Outras Empresas)

12

Exemplos de Atuadores:

13

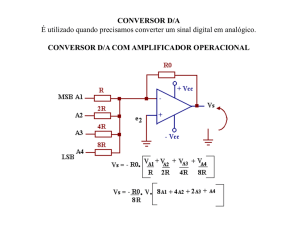

Conversor Digital-Analógico (D/A ou DAC)

Um DAC converte um sinal digital, expresso por um número

binário de n bits, em uma tensão analógica. Esta tensão analógica

“equivalente” pode assumir 2n valores distintos.

O DAC pode ser classificado, ainda, como unipolar ou sinalizado.

Os conversores unipolares apresentam uma tensão analógica de saída

sempre positiva. Para os sinalizados é pressuposto que o número

binário é sinalizado e, desta forma, a polaridade da tensão analógica

de saída depende do bit de sinal (geralmente o MSB).

Normalmente, o DAC é representado

como ilustrado na Figura ao lado.

Observar a necessidade de uma

tensão de referência (estável) que

servirá de base para produzir o sinal

analógico de saída.

b1

b2

b3

bn

Conversor D/A

(DAC)

.

.

.

Vo

n-bits

VREF

14

DAC – Função de Transferência

Uma das características mais importantes para se compreender a ação

de um conversor D/A e analisando a sua função de transferência (FT).

Como exemplo, está ilustrada a seguir uma FT para um DAC

unipolar de 3 bits.

Saída Analógica Vo / Vref

8/8

7/8

6/8

5/8

1 LSB = ⅛

4/8

3/8

2/8

1/8

0/8

000

001

010

011

100

101

110

111

(1000)

Código Digital de Entrada

A tensão de saída está normalizada em relação a VREF.

15

DAC – Função de Transferência

Matematicamente, podemos interpretar alguns pontos importantes da FT:

Vo Vref (b1 2 1 b 2 2 2 bn 2 n )

Os valores máximo e mínimo de VO serão:

1

VO (max) VREF 1 n

2

VO (min) 0

Observar que a menor mudança que pode ser provocada na tensão de saída

corresponde a variação de um bit menos significativo (LSB). Assim, temos:

LSB

1

2n

VLSB

VREF

2n

Exemplo: Um DAC unipolar de 4 bits vai apresentar em sua saída 16 níveis

diferentes de tensão (24 = 16). Se a tensão de referência for de 10V, a tensão

mínima será de 0V e a tensão máxima será de 9,375V (10.(1-24)) . A tensão VLSB

será de 0,625V (10/24).

16

DAC – Características Estáticas

Existe um conjunto de características (estáticas e dinâmicas)

associadas aos conversores que representam figuras de mérito

importantes. Principalmente quando for necessário fazer a escolha

de um conversor para uma dada aplicação. É essencial fazer a

escolha que maximize a solução custo-benefício.

Inicialmente, vamos abordar as características estáticas:

Resolução;

Fundo de Escala (Full-Scale output voltage);

Exatidão.

Depois de abordadas as suas definições vamos verificar que existem

erros (erro de offset, erro de ganho e erro de linearidade) que

podem afetá-las.

17

DAC – Características Estáticas – Fundo de Escala (FS) e Resolução

FS: É definida como sendo a diferença entre as tensões analógicas

produzidas pela maior e pela menor palavra digital de entrada. Deve-se

considerar, entretanto, que a resolução do conversor é infinita (n=∞):

1

VFS VO (max) VO (min) VREF 1 0 VREF

2

Resolução: 1) É o número de diferentes valores analógicos de saída, sendo

expressa em número de bits:

Resolução = n [bits]

2) É o “degrau” de tensão que existe quando se varia 1LSB na

palavra digital de entrada:

Resolução = VO(max)/(2n-1) [V/LSB]

Atenção: observe que pelo fato dos conversores reais não terem resolução

infinita, o máximo valor analógico de saída é inferior a FS. Um conversor

apresentar uma alta resolução não é um indicativo de boa exatidão.

18

DAC – Características Estáticas – Exatidão

Exatidão: É definida como sendo a diferença entre a resposta ideal

esperada e a resposta real do conversor incluindo os erros de

Offset, de Ganho e de Linearidade.

Esta figura de mérito é expressa através de uma porcentagem do

fundo de escala, em número de bits ou em função do LSB.

Atenção:

1. Os erros de Offset e Ganho podem ser minimizados (em alguns

casos até eliminados), na prática, por um processo de calibragem

chamado de “trimming”;

2. O projeto ou especificação de um bom conversor D/A necessita

que a exatidão seja menor que a sua resolução.

19

DAC – Erro de Offset

Saída Analógica Vo / Vref

8/8

7/8

6/8

5/8

4/8

3/8

2/8

1/8

0/8

001

010

011

100

101

110

111

(1000)

Código Digital de Entrada

Corresponde à diferença entre o valor real e o ideal da saída analógica do

conversor quando a palavra digital de entrada é zero. Resulta em um erro

constante da tensão de saída até FS, para todas as palavras digitais de

entrada. Tal erro é relacionado com o offset de entrada dos amplificadores

e comparadores utilizados nos circuitos internos do conversor.

A linha tracejada representa a resposta ideal de um DAC de 3 bits.

20

DAC – Erro de Ganho

Saída Analógica Vo / Vref

8/8

7/8

6/8

5/8

4/8

3/8

2/8

1/8

0/8

000

001

010

011

100

101

110

111

(1000)

Código Digital de Entrada

Corresponde a uma mudança na inclinação da função de transferência do

conversor, quando o erro de offset é reduzido a zero. Pode ser causado

por imprecisões no fator de escala ou mesmo na tensão de referência.

A linha tracejada representa a resposta ideal de um DAC de 3 bits.

21

DAC – Erro de Linearidade

Saída Analógica Vo / Vref

8/8

7/8

6/8

5/8

4/8

3/8

2/8

1/8

0/8

000

001

010

011

100

101

110

111

(1000)

Código Digital de Entrada

É o desvio da função de transferência real de uma linha reta (linear), quando

calibrado os erros de offset e de ganho; sendo classificado como erros de

INL e DNL. É um erro decorrente da não linearidade intrínseca dos

dispositivos semicondutores utilizados no conversor.

A linha tracejada representa a resposta ideal de um DAC de 3 bits.

22

DAC – INL e DNL

INL – Integral Nonlinearity

(Algumas vezes referenciada como Relative Accuracy ou Static Accuracy)

Corresponde ao maior desvio da saída analógica em relação a uma linha reta

desenhada entre a origem e o fundo de escala (conversor ideal).

Normalmente expressa em LSB ou em % de FS.

DNL – Differential Nonlinearity

Corresponde ao máximo desvio de quaisquer duas saídas analógicas

adjacentes com relação ao degrau de transferência ideal de 1LSB. Também

expressa em LSB ou em % FS.

Atenção:

O DAC é dito ser Monotônico se a tensão analógica de saída aumenta ou

permanece constante para um respectivo incremento do código digital de

entrada. Para tanto:

INL

1

LSB e DNL 1LSB

2

23

DAC – INL e DNL

Exemplo de avaliação dos erros DNL e INL. Observar que podem

assumir valores negativos.

Saída Analógica Vo / Vref

8/8

INL = 1LSB

7/8

6/8

5/8

transição

4/8

3/8

DNL = 2LSB-1LSB = 1LSB

2/8

1/8

0/8

000

001

010

011

100

101

110

111

(1000)

Código Digital de Entrada

24

DAC – Características Dinâmicas

Settling Time

Tempo necessário para que a saída analógica atinja o seu final dentro de uma

faixa de erro pré estabelecida (normalmente ± ½ LSB). Tipicamente situa-se

na faixa de centenas de nS a unidades de mS.

Taxa de Amostragem

Corresponde a velocidade com a qual o DAC pode realizar conversões

sucessivas. Esta grandeza é afetada pelas demoras de propagação, “slew rate”

e settling time dos circuitos internos do conversor. Normalmente expressa em

conversões por segundo (Samples/s).

Faixa Dinâmica

Representa a amplitude a qual o sinal de saída pode excursionar mantendo o

grau de linearidade estabelecida para o conversor. Os sinais devem ser

condicionados de forma a possibilitar a utilização otimizada desta faixa.

25

DAC – Topologias Básicas

Existem 3 topologias básicas para a construção dos conversores D/A:

Conversores com Rede Ponderada;

Conversores com Malha R-2R (ou Multiplicativos);

Conversores por Modulação de Largura de Pulso (PWM).

Os conversores em CI comerciais mais comuns (série DAC 08XX, por

exemplo) utilizam a conversação através da malha R-2R. O conversor

por PWM pode ser obtido, de forma simples, usando-se a saída PWM

que um microcontrolador usualmente oferece e um filtro RC.

26

DAC – Conversor (4 bits) com Rede Ponderada (Weighted Resistors)

Vref

I1

1R

I2

2R

b1

I3

4R

b2

I4

b3

8R

Conversor Corrente-Tensão

(Somador)

b4

R/2

Vo

Chaves Eletrônicas

Terra Virtual

I1 b1

VREF

V

20 b1 REF

R

R

V

V

I2 b2 REF 21 b2 REF

2R

R

VO

I3 b3

VREF

V

22 b3 REF

4R

R

I4 b 4

VREF

V

23 b 4 REF

8R

R

R

I1 I 2 I 3 I 4 R 20 b1 VREF 21 b2 VREF 22 b3 VREF 23 b4 VREF

2

2

R

R

R

R

VO VREF b1 21 b2 2 2 b3 23 b 4 2 4

27

DAC – Conversor (4 bits) com Malha R-2R (R-2R Ladder)

R

R

R

2R

Vref

2R

2R

2R

2R

b1

b2

b3

b4

R

Vo

Este conversor é muito semelhante ao anterior, contudo, apresenta a vantagem de

apresentar apenas dois valores distintos de resistores (R e 2R) o que pode aumentar a

exatidão do circuito. Outra vantagem é a diminuição da área de silício uma vez que no

conversor com rede ponderada os resistores aumentam de valor em uma proporção

geométrica.

28

DAC – Característica da Malha R-2R

R

R

R

2R

Vref

I1

2R

b1

I2

2R

b2

I3

2R

b3

I4

2R

b4

IO

IO=b1I1+b2I2+b3I3+b4I4

O lado inferior dos resistores

2R sempre “enxergam” o

potencial zero,

independentemente da

posição das chaves.

Terra Virtual

(AMPOP)

Para qualquer um dos nós, em relação à referência, observa-se, então, que o circuito

equivalente consiste de dois resistores iguais a 2R em paralelo. Desta forma, as

correntes são divididas por 2 sucessivamente. Com uma dedução semelhante a do

conversor com rede ponderada chega-se a:

VO VREF b1 2 1 b 2 2 2 b3 2 3 b 4 2 4

29

DAC – Interfaceamento

Barramento de Dados

Barramento de Endereços

mP

b0 ~ bn

a0 ~ am

R/W

Decodificador

de

Endereços

DAC

n bits

CE

Vo

WR

VREF

Basicamente, trata-se de um dispositivo de E/S para o qual deverá ser alocado uma

posição específica de endereçamento através do decodificador de endereços. O chip é

habilitado por linhas do tipo Chip Select (CS) ou Chip Enable (CE). Alguns DACs

apresentam latchs internos para receber a palavra digital a ser convertida e apresentam

linhas adicionais do tipo Write (WR).

30

Exemplo: DAC0800 (descrição geral)

31

Exemplo: DAC0800 (Estrutura Interna e Encapsulamento)

Observar que o DAC0800 oferece o sinal

analógico de saída sob a forma de corrente

(IOUT e IOUT). É necessário a presença de um

conversor corrente-tensão para se obter uma

saída analógica em tensão.

32

Exemplo: DAC0800 (Estrutura Interna Simplificada)

Recommended Full Scale Adjustment Circuit

33

Exemplo: DAC0800 (Valores Típicos)

A corrente de fundo de escala (IFS)

será dada por:

As correntes IO e IO são

complementares.

Para estes valores, IFS é de

aproximadamente 2mA

(1,992mA).

34

Exemplo: DAC0800 (Unipolar Negative Operation)

Observe que os resistores de 5K fazem a conversão corrente-tensão.

35

Exemplo: DAC0800 (Bipolar Negative Operation)

36

Exemplo: DAC0800 (Positive Low Impedance Output Operation)

Neste caso, o AMPOP faz a

conversão corrente-tensão.

Recordando os conceitos de Ciclo de Trabalho e Valor Médio

D

t ON

t

ON

t ON t OFF t W

VAVG Vhi Vlo .D VOFFSET

37

DAC por Modulação de Largura de Pulso (PWM)

A partir de um microcontrolador, por exemplo, que normalmente oferece uma saída

do tipo PWM, é possível recuperar o valor DC usando-se um simples filtro RC.

Observe que o conversor é, na realidade, implementado por software e a resolução

obtida é diretamente relacionada com o número de bits do contador interno do

microcontrolador associado ao PWM.

mC

PWM_OUT

Filtro

Analógico

(Passa-Baixa)

DC

w

|H(jw)|

wC

A freqüência de operação do

w PWM deve estar dentro da “stop

band” do filtro.

38

Exemplo: DAC (PWM) usando microcontrolador da família Z8

Filtro Passa Baixa

(2ª ordem)

Buffer

39

Exemplo: DAC0830

40

Exemplo: DAC0830

Observar a presença de dois

registros internos e a necessidade de

uma carta de tempo para ilustrar as

temporizações envolvidas.

A presença deste resistor, interno ao

CI (≈ 20K), facilita a interface com

um AMPOP para produzir a

conversão corrente-tensão.

41

Exemplo: DAC0830

42