Capítulo 5

Sub-rotinas e Estruturação da

Linguagem de Programação

“Assembly” aplicadas a família de

microcontroladores MCS-51 da

Intel

Prentice Hall

Microcontroladores 8051

1

Capítulo 5

Definição de sub-rotina

Programa Principal:

instrução 1

:

instrução N

rotina que calcula uma expressão matemática(tamanho de 60 bytes, por exemplo)

instrução N+1

:

instrução M

rotina que calcula uma expressão matemática(tamanho de 60 bytes, por exemplo)

instrução M+1

:

instrução O

rotina que calcula uma expressão matemática(tamanho de 60 bytes, por exemplo)

etc…

END

Prentice Hall

Microcontroladores 8051

2

Capítulo 5

Sub-rotina:

End1: sub-rotina que calcula uma expressão matemática (tamanho de 60 bytes, por exemplo)

RET

Programa Principal:

ProgP: instrução 1

:

instrução N

Chamada a sub-rotina que calcula uma expressão matemática

(ACALL end1/LCALL end1 – 2 ou 3 bytes)

instrução N+1

:

instrução M

Chamada a sub-rotina que calcula uma expressão matemática

(ACALL end1/LCALL end1 – 2 ou 3 bytes)

instrução M+1

:

instrução O

Chamada a sub-rotina que calcula uma expressão matemática

(ACALL end1/LCALL end1 – 2 ou 3 bytes)

etc…

END

Prentice Hall

Microcontroladores 8051

3

Capítulo 5

Área de memória de programa 1

; Área de Memória de Programa das "Sub-rotinas"

; Sub-rotina 1:

endereço inicial da sub-rotina 1: instrução 1

:

instrução N

RET

; Sub-rotina M:

endereço inicial da sub-rotina M: instrução 1

:

instrução N

RET

Área de memória de programa 2

; Área de Memória de Programa do “Programa Principal”

endereço inicial do programa principal: instrução 1

:

;chamada a "sub-rotina 1"

ACALL/LCALL endereço inicial da sub-rotina 1

;chamada a "sub-rotina 2"

ACALL/LCALL endereço inicial da sub-rotina 2

:

;chamada a "sub-rotina M"

ACALL/LCALL endereço inicial da sub-rotina M

;

instrução K

END

Prentice Hall

Microcontroladores 8051

4

Capítulo 5

Vantagens da utilização de sub-rotinas:

Princípio de funcionamento de uma sub-rotina:

Mas, como uma sub-rotina fisicamente é executada pelo

microprocessador ?

Pilha (LIFO – Last-In, First-Out)

RAM

Endereço Conteúdo

07h

((SP))

(SP) = 07h

08h

:

Cresce

Decresce

:

7Fh

Figura 4: Representação esquemática da pilha (LIFO) após um sinal de reset.

Prentice Hall

Microcontroladores 8051

5

Capítulo 5

Instrução

Bytes Ciclos

Codificação

Operação

PUSH direct

2

2

1100 0000 direct address

POP direct

2

2

1101 0000 direct address

(PC) (PC) + 2

(SP) (SP) + 1

((SP)) (direct)

(PC) (PC) + 2

(direct) ((SP))

(SP) (SP)-1

Tabela 1: Descrição das instruções PUSH direct e POP direct.

Prentice Hall

Microcontroladores 8051

6

Capítulo 5

Instrução

Bytes

Ciclos

Codificação

Operação

(PC)(PC)+2

(SP) (SP)+1

((SP)) (PC7-0)

(SP) - (SP)+1

((SP)) (PC15-8)

(PC10-0) addr11

LCALL addr16

3

2

0001 0010 a15....a8 a7 ..........a0 (PC) (PC)+3

(SP) (SP)+1

((SP)) - (PC7-0)

(SP) (SP)+1

((SP)) (PC15-8)

(PC15-0) addr16

Tabela 2: Descrição das instruções ACALL addr11 e LCALL addr16.

ACALL addr11

Prentice Hall

2

2

a10 a9 a8 1 0001 a7............a0

Microcontroladores 8051

7

Capítulo 5

Instrução

Bytes

Ciclos

Codificação

Operação

RET

1

2

0010 0010

RETI

1

2

0011 0010

(PC15-8) ((SP))

(SP) (SP)-1

(PC7-0) ((SP))

(SP) (SP)-1

(PC15-8) ((SP))

(SP) (SP)-1

(PC7-0) ((SP))

(SP) (SP)-1

Tabela 3: Descrição das instruções RET e RETI.

Prentice Hall

Microcontroladores 8051

8

Capítulo 5

Estruturação da

Linguagem Assembly

Descrição e Definição das Sub-rotinas

Início do programa: Inicialização das variáveis e programação do hardware

Loop do programa principal:

- processamento/instruções de chamadas a sub-rotinas;

- instrução de "jumper" incondicional para o início do Loop do

programa principal (gerenciamento e controle de 24 horas por dia).

Prentice Hall

Microcontroladores 8051

9

Capítulo 5

Estruturação da Linguagem “Assembly”:

;Sub-rotinas - Primeira Parte:

addr1: Subrotina 1

RET

:

addrN: Subrotina N

RET

; Inicialização das variáveis do programa e do “hardware” - Segunda Parte que pertence ao

; programa principal:

endereçodoIniciodoprogramaprincipal:

instruções 1

:

instrução N

; "Loop" do Programa Principal - Terceira Parte que pertence ao programa principal:

loop:

instrução 1

:

instrução N

call adr1

; chama a subrotina 1

:

:

call adrN

; chama a subrotina N

:

:

sjmp loop

; “Fim do looping do programa

END

; principal”

Prentice Hall

Microcontroladores 8051

10

Capítulo 5

Metodologia sistemática de implementação de projeto de programa;

Para um projeto completo constituído de muitas funções ou tarefas, a solução é

facilmente implementada através da divisão do projeto completo em pequenos módulos

(simples sub-rotinas) que são responsáveis por tarefas específicas e bem definidas;

Tempo de implementação é extremamente reduzido, pois somente é necessário definir

as diferentes tarefas (sub-rotinas) que o projeto deve executar e essas tarefas devem ser

chamadas no loop do programa principal de forma organizada e seqüencial;

Alta confiabilidade na implementação das sub-rotinas;

Tempo de desenvolvimento reduzido;

Tempo de simulação reduzido;

Tempo de emulação reduzido;

Tempo de manutenção reduzido;

Projeto modular;

Flexibilidade na implementação de novas características ao produto final através da

inserção e retiradas dos módulos que compõem o projeto do programa;

Inserção dos módulos já implementados em bibliotecas de sub-rotinas. Na

implementação de novos projetos as mesmas podem ser utilizadas imediatamente;

Fácil manutenção pois quando ocorrer um problema, o mesmo pode ser diretamente

analisado na sua respectiva sub-rotina.

Prentice Hall

Microcontroladores 8051

11

Capítulo 5

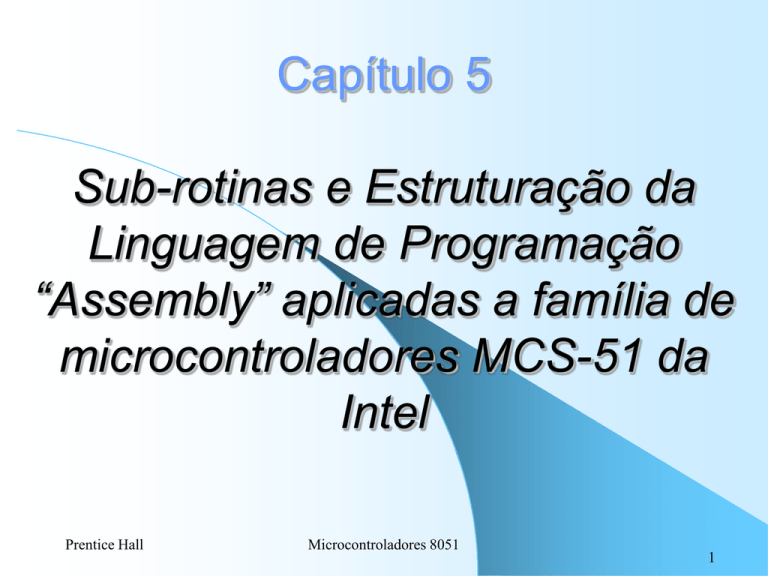

SUB1: Qte de Nums = FFh

Programa Principal

(R0)#60h

(R1)#05h

(65h)#00h

(PSW) #00h

(SP) #70h

Chama sub-rotina SUB1

(C)#0b

(A)((R0))

(A)(A)-(C)-#0FFh

Fim

S

(A)0 ?

[(A) #0FFh ?]

N

(65h)(65h)+1

(R0)(R0)+1

S

(R1)(R1)-1

(R1)0 ?

N

RET

Prentice Hall

Microcontroladores 8051

12

Capítulo 5

DEFSEG

EXEMPLO, ABSOLUTE

SEG

EXEMPLO

ORG

0100h

; Sub-rotina que calcula a qte de num=0FFh

SUB1: MOV R0,#60h

; Endereço inicial do buffer

MOV R1,#05h

; Quantidades de elementos do buffer

MOV 65h,#00

; Zera contador de num=0FFh

ADR2: CLR

C

; Zera o (C): não influenciar a op. de sub.

MOV A,@R0

; Carrega (A) com o cont. do buffer de mem.

SUBB A,#0FFh

; Subtrai o (A) da const. 0FFh

JNZ

ADR1

; Se (A)0 (A #0FFh) (PC)=ADR1 [não soma um no (65h)]

INC

65h

; Se (A)=0 (A = #0FFh), soma um no (65h)

ADR1: INC

R0

; Aponta p/ a próx. pos. mem. a ser analisada

DJNZ R1,ADR2

; Existem mais dados a serem analisados ? Se sim, salta para ADR2

RET

; Se não, finaliza a sub-rotina se (R1)=0 e retorna.

; Início do programa principal

PROGP:MOV PSW,#00h

; Faz (PSW) #00h.

MOV SP,#70h

; Define (SP)=70h (início da Pilha)

ACALL SUB1

; Chama a sub-rotina SUB1.

END

; Fim do programa principal

Prentice Hall

Microcontroladores 8051

13