SEEP

Sistemas Eletrônicos Embarcados

Baseados em Plataforma

UFRGS

Instituto de Informática

Departamento de Engenharia Elétrica

Grupo de Microeletrônica

LSE – Laboratório de Sistemas Embarcados

1 de 31

Introdução

• projeto aprovado pelo programa PD&I-TI (Pesquisa, Desenvolvimento

e Inovação em Tecnologias da Informação)

– financiado com recursos do CT-Info (fundo setorial de Informática)

• realização pelo Laboratório de Sistemas Embarcados da UFRGS

– Flávio, Susin, Luigi, Luba, Carlos Eduardo

• desenvolvimento no período de janeiro 2003 a dezembro 2006

– aprovação inicial por 2 anos, com renovação após avaliação

• orçamento geral de R$ 931 mil, para período de 4 anos

– R$ 450 mil em bolsas DTI

– R$ 307 mil em custeio

– R$ 174 mil em capital

2 de 31

Resultados gerais principais

• plataforma arquitetural configurável para SoCs embarcados

–

–

–

–

com componentes IP de HW (processadores, memórias, outros)

com componentes IP de SW (orientados para os domínios de aplicação)

com diversas estruturas de comunicação

fortemente direcionada à transformação da realidade nacional, mas

atingindo o estado-da-arte mesmo em mercados internacionais

• metodologia completa de projeto de SoCs embarcados, visando a

configuração da plataforma, principalmente através do software de

aplicação, incluindo ferramentas de:

–

–

–

–

exploração arquitetural

geração do software de aplicação

síntese de processadores dedicados

estimativas de desempenho e potência

–

–

–

–

co-simulação

geração do RTOS

integração de componentes IP

teste

3 de 31

Resultados gerais complementares

• desenvolvimento, prototipação e avaliação de duas aplicações de porte e

relevância industrial, utilizando a plataforma e a metodologia de

concepção resultantes do projeto

• biblioteca de IPs para plataformas direcionadas a aplicações industriais

relevantes para o país

• disponibilização de resultados (processos, técnicas, ferramentas,

componentes de hardware e software, aplicações) para a comunidade

de P&D nacional, inclusive através da internet

• acréscimo de 20% na produção científica atual do grupo, com

publicação no período de 18 artigos completos em periódicos

internacionais indexados e 40 artigos completos em eventos

internacionais, como resultado direto do projeto.

• formação de pelo menos 8 doutores e 20 mestres no período do projeto

• organização do material resultante do projeto em um livro “Projeto de

Sistemas Embarcados Baseado em Plataformas”

4 de 31

Atividades

• Atividades básicas

–

–

–

–

–

PLAT – plataforma de hardware

IP – integração de componentes IP hw/sw

CO-SIM – co-simulação distribuída

JAVA – síntese automática de microcontroladores JAVA

RTOS – sistema operacional de tempo real

• Atividades integradoras

–

–

–

–

ESTIM – estimativas de desempenho e potência

EXPLOR – ambiente de exploração arquitetural

TESTE – metodologia de teste

SOFT – geração automática de software

• Aplicações

– APLIC1 – aplicação de porte industrial, internacional (domótica?)

– APLIC2 – aplicação de porte industrial, nacional (terminal internet?)

– PROTO – prototipação, teste, avaliação e refinamento das aplicações

5 de 31

PLAT

• definição de duas plataformas de hardware para sistemas eletrônicos

embarcados complementares, orientadas para as aplicações previstas

• plataformas incrementam reuso de componentes de hw e sw

• configuráveis especialmente pelo software da aplicação e pela

parametrização de componentes

– parametrização em termos de desempenho, potência, área

• hardware

– processadores e blocos dedicados de hardware

– estrutura de comunicação dedicada à aplicação

– possível substrato: FPGAs

• software

– RTOS

6 de 31

PLAT

• 2003/1 a 2004/2

• bolsistas DTI: 1 recém-doutor, 1 recém-graduado

• indicadores de progresso ano 1

– definição inicial de duas plataformas, uma para cada aplicação-alvo,

atendendo requisitos distintos de custo, potência, desempenho

• indicadores de progresso ano 2

– definição final das plataformas, contendo processadores e blocos dedicados

de hardware, interconectados por uma estrutura de comunicação dedicada

à aplicação

7 de 31

IP

• mecanismo de integração de componentes IP homogêneos ou

heterogêneos de hardware e software

• componentes homogêneos: padrões

• padrões de hardware

– barramento: AMBA?

– interfaces de componentes: OCP? VCI?

• padrões de software: API com primitivas de comunicação de alto nível

• componentes heterogêneos

– construção automática ou semi-automática de adaptadores de interfaces

– uso de templates de hardware

– adaptação do código fonte de componentes de software

8 de 31

IP

• 2003/1 a 2004/2

• bolsistas DTI: 1 recém-doutor

• indicadores de progresso ano 1

– biblioteca de adaptadores de componentes IP para o padrão OCP

– adaptadores para processador femtoJava, memórias e interfaces de

periféricos

– componentes descritos nas linguagens C e Java

• indicadores de progresso ano 2

– ambiente completo de modelagem com suporte para a integração de

componentes IP

– biblioteca de adaptadores para padrões AMBA e VCI

– componentes descritos na linguagem SystemC

9 de 31

CO-SIM

• ambiente de co-simulação distribuída multi-nível

• uso do backbone DCB

• suporte para avaliação remota de componentes IP

– integração virtual ao modelo

– comunicação apenas através das interfaces

• suporte para construção de modelos contendo componentes homgêneos

ou heterogêneos

– heterogeneidade de interfaces, linguagens, níveis de abstração

• construção automática dos adaptadores de linguagens

• suporte para construção dos adaptadores de interfaces (atividade IP)

10 de 31

CO-SIM

• 2003/1 a 2004/2

• bolsistas DTI: 1 recém-mestre

• indicadores de progresso ano 1

– recursos para integração entre componentes C e Java

– geração de código de co-simulação para modelos distribuídos e

heterogêneos

• indicadores de progresso ano 2

– recursos para integração de componentes SystemC e VHDL

– geração de código de co-simulação para modelos não-distribuídos e

homogêneos

11 de 31

JAVA

• ambiente de síntese automática de microcontroladores dedicados e

otimizados

– plataforma combinando alto desempenho e baixa potência

• capazes de executar "byte-codes" Java

– portabilidade das aplicações, reuso de software

• síntese a partir de uma especificação Java da aplicação

• síntese de variantes do microcontrolador, suportando de forma mais

eficientes diferentes modelos de computação

– DSP

– multithread

12 de 31

JAVA

• 2003/1 a 2004/2

• bolsistas DTI: 1 recém-graduado

• indicadores de progresso ano 1

– definição de variantes arquiteturais do processador femtoJava, em especial

a versão DSP e a versão multi-thread, para uso na plataforma de baixa

potência

• indicadores de progresso ano 2

– ambiente de síntese automática de microcontroladores dedicados e

otimizados, capazes de executar "byte-codes" Java, a partir de uma

especificação Java da aplicação

13 de 31

RTOS

• geração automática de RTOS dedicado e otimizado para uma dada

aplicação embarcada

• configuração automática para a plataforma de hardware selecionada

• otimização de aspectos particulares de uma aplicação (desempenho,

potência)

• recursos

–

–

–

–

escalonamento de processos

atendimento de requisitos de tempo real

gerência de sistemas distribuídos

suporte à comunicação entre processos e processadores

14 de 31

RTOS

• 2003/2 a 2005/1

• bolsistas DTI: 1 recém-mestre

• indicadores de progresso ano 1

– definição dos módulos que deverão compor o RTOS, considerando o espaço

de automação de projeto

• indicadores de progresso ano 2

– desenvolvimento das rotinas para síntese do RTOS a partir da especificação

de alto nível do sistema embarcado

• indicadores de progresso ano 3

– conclusão da técnica de geração automática de RTOS

15 de 31

ESTIM

• metodologia de estimativas de desempenho, consumo de potência e

memória utilizada, a partir de especificações de alto nível da aplicação

• suporte à exploração do espaço de projeto

• estimativas para uma combinação aplicação – arquitetura-alvo

– plataforma de hardware (componentes IP, considerando diferentes tipos de

processadores)

– RTOS

– mecanismos de comunicação de hardware e software

16 de 31

ESTIM

• 2004/1 a 2005/2

• bolsistas DTI: 1 recém-mestre

• indicadores de progresso ano 2

– levantamento de características físicas de IPs, estruturas de comunicação e

software, para obter subsídios para estimação de desempenho, potência e

memória em alto nível de abstração

• indicadores de progresso ano 3

– ferramentas de estimativa de desempenho, potência e memória a partir de

especificação de alto nível da aplicação, orientadas para as plataformas

definidas no projeto

17 de 31

EXPLOR

• ambiente de exploração arquitetural de SoC

• estimativa de desempenho e potência de alternativas de distribuição das

funções computacionais entre processadores

– número e tipo de processadores

• estimativa de desempenho e potência de alternativas de estruturas de

comunicação

– barramentos simples

– NoC

• impacto do mapeamento de funções em diferentes posições da NoC

18 de 31

EXPLOR

• 2004/1 a 2005/2

• bolsistas DTI: 1 recém-mestre

• indicadores de progresso ano 2

– biblioteca de IPs com versões de componentes (minimizando área, potência,

espaço de memória, tempo de processamento) para exploração do espaço

de projeto

• indicadores de progresso ano 3

– ferramenta de catalogação e seleção de IPs baseada em requisitos da

aplicação

19 de 31

TESTE

• metodologia de teste de software e hardware, considerando arquiteturaalvo

– plataforma de hardware (componentes de processamento e estruturas de

comunicação)

– plataforma de software (RTOS)

• desenvolvimento de técnicas de teste

– com redução do tempo de teste

– com baixo custo (reuso das estruturas já existentes no sistema)

– com aumento da testabilidade

20 de 31

TESTE

• 2005/1 a 2006/2

• bolsistas DTI: 1 recém-doutor

• indicadores de progresso ano 3

– técnicas de teste de software aplicáveis a descrições VHDL: estudos de caso

– sequência de teste externo para o microcontrolador femtoJava

• indicadores de progresso ano 4

– ferramentas de auxílio ao planejamento de teste de SoCs baseados em

controladores integrados e em NoCs

21 de 31

SOFT

• geração automática de software a partir de uma especificação de alto

nível

• mapeamento automático para programas otimizados para o paradigma

computacional dos processadores considerados (microcontroladores,

DSP, ASIPs, VLIW, multithread, etc.)

• otimização segundo requisitos de desempenho, potência, memória

• exploração do espaço de projeto

• desenvolvimento de conjunto de classes para diferentes modelos de

computação

• definição de linguagem abstrata de modelagem para especificação de

alto nível (UML, Rosetta)

22 de 31

SOFT

• 2005/1 a 2006/2

• bolsistas DTI: 1 recém-doutor

• indicadores de progresso ano 3

– levantamento de características comuns de aplicações embarcadas, para

captura de diferentes modelos comportamentais de software, visando sua

automação

• indicadores de progresso ano 4

– geração automática de software de aplicação, sobre a plataforma de

hardware e software, a partir de especificações de alto nível em diferentes

modelos de computação

23 de 31

APLIC1

• especificação e desenvolvimento de uma aplicação de porte industrial e

relevância internacional, na área da domótica, para validação da

metodologia completa de projeto

– modelagem de alto nível, seleção da arquitetura, refinamento arquitetural,

simulação em diferentes níveis de abstração, desenvolvimento e integração

dos componentes (IPs) necessários e geração do software

• 2004/1 a 2005/2

• bolsistas DTI: 1 recém-mestre, 1 recém-graduado

• indicadores de progresso

– ano 2: modelagem de alto nível da aplicação, exploração de soluções

arquiteturais, desenvolvimento e busca de componentes IP necessários

– ano 3: conclusão da aplicação, com síntese final do software e hardware

24 de 31

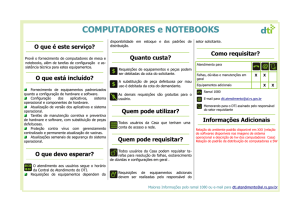

APLIC2

• especificação e desenvolvimento de uma segunda aplicação de porte

industrial, com impacto mais voltado à realidade social brasileira

– possível aplicação: terminal portátil de acesso à Internet de baixíssimo

custo, para aumentar a acessibilidade da população a tecnologias mais

complexas

• 2005/1 a 2006/2

• bolsistas DTI: 1 recém-doutor, 1 recém-graduado (15)

• indicadores de progresso

– ano 3: modelagem de alto nível da aplicação, exploração de soluções

arquiteturais, desenvolvimento e busca de componentes IP necessários

– ano 4: conclusão da aplicação, com síntese final do software e hardware

25 de 31

PROTO

• prototipação das aplicações em FPGAs

– teste dos protótipos segundo a metodologia de teste

– avaliação dos protótipos, em termos de desempenho e potência consumida,

através de benchmarks de domínio público

– refinamento das aplicações, segundo interesse de parceiros industriais, a

partir de parâmetros fornecidos pela própria indústria

• 2005/1 a 2006/2

• bolsistas DTI: 1 recém-graduado

• indicadores de progresso

– ano 3: montagem da primeira aplicação em placas de FPGAs, para

validação de metodologia e ferramentas de projeto e identificação de pontos

críticos da implementação do protótipo

– ano 4: montagem da segunda aplicação, comparação de resultados,

montagem de outra versão de uma das aplicações para exploração do

espaço de projeto e avaliações comparativas

26 de 31

Cronograma

ATIVIDADE

1. PLAT

2. IP

3. CO-SIM

4. JAVA

5. RTOS

6. TESTE

7. EST IM

8. SOFT

9. EXPLOR

10. APLIC1

11. APLIC2

12. PROTO

2003/1

//////////////

//////////////

//////////////

//////////////

2003/2

//////////////

//////////////

//////////////

//////////////

//////////////

2004/1

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

2004/2

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

2005/1

2005/2

2006/1

2006/2

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

//////////////

27 de 31

Outros indicadores de progresso

ano 1

ano 2

ano 3

ano 4

formação de 5 mestres e 1 doutor

submissão de artigos: 2 periódicos e 10 eventos internacionais

relatórios de pesquisa

1ª versão do site para disponibilização de resultados

formação de 5 mestres e 2 doutores

submissão de artigos: 2 periódicos e 10 eventos internacionais

relatórios de pesquisa

2ª versão do site

formação de 5 mestres e 2 doutores

submissão de artigos: 6 periódicos e 10 eventos internacionais

relatórios de pesquisa

versão final do site, com componentes IP de HW e SW

formação de 5 mestres e 3 doutores

submissão de artigos: 8 periódicos e 10 eventos internacionais

relatórios de pesquisa

28 de 31

Orçamento

2003

2004

2005

2006

Diárias no país

3.835,05

3.835,05

3.835,05

3.835,05

Diárias internacionais

3.835,05

3.835,05

3.835,05

3.835,05

Material de consumo

2.000,00

2.000,00

2.000,00

2.000,00

Passagens nacionais

5.000,00

5.000,00

5.000,00

5.000,00

Passagens internacionais

25.000,00

25.000,00

25.000,00

25.000,00

Terceiros pessoa física

5.000,00

5.000,00

5.000,00

5.000,00

Terceiros pessoa jurídica

33.820,00

33.820,00

33.820,00

33.820,00

Material perma nente

56.000,00

26.000,00

58.000,00

18.000,00

Material bibliográfico

4.000,00

4.000,00

4.000,00

4.000,00

138.490,10

108.490,10

140.490,10

100.490,10

29 de 31

Bolsistas DTI

DTI-7D (doutor)

DTI-7H (grad)

DTI-7D (doutor)

DTI-7G (m estre)

DTI-7H (grad)

DTI-7G (m estre)

DTI-7G (m estre)

DTI-7G (m estre)

DTI-7G (m estre)

DTI-7H (grad)

DTI-7D (doutor)

DTI-7D (doutor)

DTI-7D (doutor)

DTI-7H (grad)

DTI-7H (grad)

2003/1

PLAT

PLAT

IP

CO-SIM

JAVA

2003/2

PLAT

PLAT

IP

CO-SIM

JAVA

RTOS

2004/1

PLAT

PLAT

IP

CO-SIM

JAVA

RTOS

ESTIM

EXPLO

APLIC1

APLIC1

2004/2

PLAT

PLAT

IP

CO-SIM

JAVA

RTOS

ESTIM

EXPLO

APLIC1

APLIC1

2005/1

2005/2

2006/1

2006/2

RTOS

ESTIM

EXPLO

APLIC1

APLIC1

TESTE

SOFT

APLIC2

APLIC2

PROTO

ESTIM

EXPLO

APLIC1

APLIC1

TESTE

SOFT

APLIC2

APLIC2

PROTO

TESTE

SOFT

APLIC2

APLIC2

PROTO

TESTE

SOFT

APLIC2

APLIC2

PROTO

30 de 31

Coordenação científica

• reuniões técnicas semanais dentro de cada atividade

– presença de toda a sub-equipe

– discussão detalhada de problemas e soluções

• seminários quinzenais, envolvendo toda a equipe

– discussão dos trabalhos em andamento

– prévias de apresentações em conferências

– palestras convidadas, etc.

• reuniões de coordenação científica mensais

–

–

–

–

restritas aos pesquisadores líderes

avaliação de resultados

planejamento de atividades

integração das grandes linhas e estratégias científicas

• workshops de todo o grupo, abertos à comunidade nacional

– realizados em paralelo com eventos nacionais significativos (SBCCI, p.ex.)

– divulgação de resultados parciais do projeto

31 de 31