Revisão

Conceitos Fundamentais

Arquitetura da CPU

Unidade

de

Controle

Registradores

Unidade

lógica e

Aritmética

Registradores

Conjunto de unidades de armazenamento;

Funcionam num nível de hierarquia acima da

memória principal e da memória cache;

Também conhecida como memória de

rascunho;

Divide-se em dois tipos:

–

–

Visíveis ao usuário;

Controle e estado;

Registradores visíveis ao usuário

Podem ser acessados pelo usuário através

das linguagens de maquina ou de montagem;

Minimizam as referencias a memória principal;

São classificados em:

–

–

–

–

Registrador de Propósito geral

Registrador de dados;

Registrador de endereço;

Registrador de código de condição;

Registradores de código de

condição (flags)

Armazenam bits que definem o resultado de uma

operação;

Esses bits podem indicar se o resultado produzido é

positivo, negativo, zero ou overflow;

Em algumas arquiteturas é representado por um único

registrador (de controle);

As linguagens de máquina permitem ler esses bits

mas não alterar seu valor;

Registradores de controle e estado

São usados para controlar as ações da CPU;

É comum que eles não sejam visíveis ao

usuário;

Contudo alguns podem ser visíveis no nível de

linguagem de maquina e nível de SO

Existem várias classificações para esse tipo de

registrador, variando de máquina para

máquina

Registradores de controle e estado

Contador de Programas (PC)

–

–

–

Contem o endereço da instrução a ser buscada;

É atualizado pela CPU depois de cada busca;

Um salto ou desvio também alteram seu valor;

Registrador de instrução (IR);

–

Contem a ultima instrução buscada;

Registradores de controle e estado

Registrador de endereçamento (MAR);

–

Contém o endereço de uma posição de memória;

Registrador de armazenamento Temporário de dados

(MBR);

–

–

–

Contém uma palavra de dados a ser escrita na memória ou a

palavra lida recentemente;

Usado para trocar dados com os registradores visíveis ao

usuário;

Pode ser acessado diretamente pela ULA;

Registradores de controle e estado

Registradores de Armazenamento temporários

Projeto de Registradores Visíveis

ao usuário

Decidir entre propósito geral ou uso

especifico;

–

–

A especialização economiza bits, porem limita a

flexibilidade da programação

A tendência atual é especializar

Decidir o número de registradores

–

–

Um numero elevado requer mais bits para

especificar um operando

Um numero reduzido implica em mais acessos a

memória

Projeto de Registradores Visíveis

ao usuário

Decidir o tamanho dos registradores

–

–

Devem ter tamanho suficiente para conter o maior

endereço de memória;

Devem ser capazes de conter os dados da

maioria dos tipos disponíveis

Projeto de Registradores de

Controle e Estado

Decidir sobre o suporte ao SO

–

–

Certos tipos de informações de controle são úteis

ao SO

O projeto pode ser feito de acordo com as

necessidades do SO

Decidir sobre a alocação de dados de controle

entre os registradores e a memória

–

Levando em conta custo e taxa de acesso o que

deve ficar na em cada um?

Respostas

Trabalho 01

1.

Descreva a arquitetura básica da CPU,

mostrando seus componentes e a função de

cada um deles.

Tarefas da CPU

Buscar instruções

Interpretar Instruções

Buscar dados

Processar dados

Escrever Dados

O Ciclo de instruções

Ciclo simples

Inicio

Ciclo de

busca

Ciclo de

execução

Busca da

próxima

instrução

Execução

da

instrução

Fim

O Ciclo de instruções

Ciclo de busca

–

–

–

–

Lê a próxima instrução da memória

Essa instrução esta armazenada no Contador de

Programas (PC)

O processador incrementa o valor de PC

A instrução buscada é armazenada no registrador

de instruções (IR)

O Ciclo de instruções

Ciclo de Execução

–

–

Interpreta o código da operação e efetua a mesma;

As ações efetuadas podem ser:

Processador-memória

Processador-E/S

Processamento de dados

Controle

O Ciclo de instruções

Exemplo:

Formato da instrução

Código da

Endereço

operação

0

34

Formato dos números

Sinal

0

15

Magnitude

1

15

Lista de operações

0001 (1) – Carregar o valor em AC

– 0010 (2) – Armazenar o valor de AC na memória

– 0101 (5) – Somar o valor de AC com o valor de um endereço

–

O Ciclo de instruções

Exemplo:

–

–

Ciclo de instruções para o código A = A + B;

São necessárias 3 instruções:

–

Carregar o valor de A

Somar o valor de B com valor de A

Guardar o resultado em A e armazenar na memória

Será realizado é 3 ciclos de busca e execução

totalizando 6 passos;

O Ciclo de instruções

Exemplo:

Memória

300

301

302

1940

5941

2941

940 0003

941 0002

942

Registradores da CPU

300

PC

AC

1940

IR

Passo 1

O Ciclo de instruções

Exemplo:

Memória

300

301

302

1940

5941

2941

940 0003

941 0002

942

Registradores da CPU

301

0003

1940

PC

AC

IR

Passo 2

O Ciclo de instruções

Exemplo:

Memória

300

301

302

1940

5941

2941

940 0003

941 0002

942

Registradores da CPU

301

0003

5941

PC

AC

IR

Passo 3

O Ciclo de instruções

Exemplo:

Memória

300

301

302

1940

5941

2941

940 0003

941 0002

942

Registradores da CPU

302

0005

5941

PC

AC

IR

3+2=5

Passo 4

O Ciclo de instruções

Exemplo:

Memória

300

301

302

1940

5941

2941

940 0003

941 0002

942

Registradores da CPU

302

0005

2941

PC

AC

IR

Passo 5

O Ciclo de instruções

Exemplo:

Memória

300

301

302

1940

5941

2941

940 0003

941 0005

942

Registradores da CPU

303

0005

2941

PC

AC

IR

Passo 6

O Ciclo de instruções

Ciclo ampliado

Interpretação

da instrução

Cálculo

do

endereço

da

instrução

Armazenamento

do operando

Busca de

operando

Busca da

instrução

Calculo

de

endereço

do

operando

Execução da

instrução

Calculo

de

endereço

do

operando

Interrupções

Mecanismo pelo qual um componente de

arquitetural pode interromper a seqüência

normal de execução

Visa a melhoria no desempenho do

processador

São agrupadas em:

–

–

–

–

Interrupção de Software

Interrupção de relógio

Interrupção de E/S

Interrupção de falha de hardware

Interrupções

Exemplo:

–

–

–

Um dada impressora recebe um fluxo de dados

provenientes do final de um ciclo de execução;

Essa impressora demora muito para terminar

imprimir os dados no papel;

O que a CPU deve fazer enquanto espera esses

dados serem impressos?

Sem um sistema de interrupção ela fica parada

Com sistema de interrupção ela faz pequenas pausas.

Interrupção

Ciclo com interrupção

Busca de

operando

Busca da

instrução

Interpretação

da instrução

Cálculo do

endereço

da

instrução

Armazenamento

do operando

Calculo

de

endereço

do

operando

Execução

da

instrução

Calculo

de

endereço

do

operando

Verifica

ocorrência

de

interrupção

Interrupção

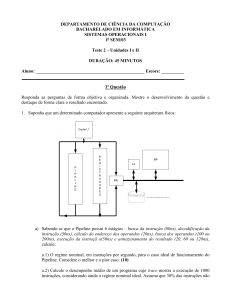

Pipeline

Técnica de implementação de processadores que

permite a sobreposição temporal das diversas fases

de execução das instruções

Constituído por seqüência de estágios operando em

paralelo

Funciona de modo semelhante a uma linha de

montagem

Seu uso visa a melhora no desempenho do

processador

Características do Pipeline

Aumenta o número de instruções executadas

simultaneamente

Aumenta taxa de instruções iniciadas e

terminadas por unidade de tempo

Melhora o desempenho do processo

(throughput)

Não reduz o tempo gasto para completar cada

instrução individualmente.

Pipeline do ciclo de instrução

Suponha que o ciclo pudesse ser resumido

dos seguintes estágios:

–

–

–

–

–

–

Busca de Instrução (BI)

Decodificação da Instrução (DI)

Cálculo de (endereço) Operandos (CO)

Busca de Operandos (BO)

Execução da Instrução (EI)

Armazenamento de Operandos (AO)

Pipeline do ciclo

Exemplo 3

Instrução

1

2

3

4

Instante de Tempo

1

2

3

4

5

6

7

8

BI

DI

CO

BO

EI

AO

BI

DI

CO

BO

EI

AO

BI

DI

CO

BO

EI

AO

BI

DI

CO

BO

EI

9

AO

Características do Pipeline

Deve-se procurar dividir a execução da

instrução em estágios com o mesmo Tempo

Contudo alguns estágios são mais lentos:

–

O estagio execução é geralmente mais lento que o

de busca

Quando os estágios não tem o mesmo tempo:

–

–

Algumas instruções podem ter o seu tempo

aumentado

Isso ocorre pois elas atravessam estágios em que

não realizam nenhuma operação útil

Pipeline do ciclo

Exemplo 4

Instrução

Instante de Tempo

1

1

2

3

4

2

B

DI

I

3

4

B

EI

O

CO

B

DI

I

5

8

9

AO

B

EI

O

CO

B

DI

I

7

AO

B

EI

O

CO

B

DI

I

6

CO

AO

B

EI

O

AO

Pipeline do ciclo

Exemplo 5

Instrução

Instante de Tempo

1

1

2

3

4

B

I

2

DI

3

5

B

EI

O

CO

B

DI

I

4

B

DI

I

B

DI

I

AO

B

EI

O

CO

CO

7

AO

B

EI

O

CO

6

B

EI

O

AO

AO

8

9

Conflitos

Situações que impedem a próxima instrução

dentro de uma fila de ser executada no ciclo

esperado

Os Conflitos reduzem o tempo de ganho obtido

pelo pipelining

Existem três classes de conflitos:

–

–

–

Estrutural

de Dados

de Controle

Conflitos Estruturais

Oriundos de um hardware que não suporta a

sobreposição simultânea de todas as etapas

de instruções

No exemplo da lavanderia seria o equivalente

a implementar um pipeline onde só existisse

uma tomada para a máquina de lavar e para a

máquina de secar.

Conflitos de Dados

Ocorrem quando uma instrução para ser

executada depende dos resultados gerados

por alguma instrução anterior que ainda não foi

completada

No exemplo da lavanderia seria um caso em

que a secadora demorou demais para secar

uma roupa e já tem a roupa lavada de outro

cliente na fila para secar.

Conflito de Controle

Ocorrem quando uma instrução de salto

condicional (desvio) entra no pipeline

provocando o cancelamento de instruções

subsequentes que também entraram no

pipeline.

Pipeline do ciclo c/ desvio

Exemplo 6

Instrução

Instante de Tempo

1

1

2 (salto

p/ 5)

3

4

5

2

B

DI

I

3

4

B

EI

O

CO

B

DI

I

5

7

9

AO

B

O

CO

B

DI

I

8

AO

B

EI

O

CO

B

DI

I

6

CO

B

DI

I

CO

Pipeline do ciclo c/ desvio

Exemplo 6 (continuação)

Instrução

Instante de Tempo

10

11

12

13

EI

AO

14

15

1

2 (salto

p/ 5)

3

4

5 (salto

p/3)

B

EI

O

B

EI

O

AO

AO

16

17

18

Memória Principal

Memória que armazena os dados e programas em

linguagem de máquina em execução corrente

Razoavelmente barata

Tempo de acesso da ordem de nano-segundos a

dezenas de nano-segundos

Freqüência de acesso alta. Se não existisse a

memória Cache, seria acessada a cada ciclo de

busca-decodificação-execução

Hierarquia de memória

Modelo hierárquico

Memória Principal

Cada posição da memória principal tem um

endereço único

Geralmente é combinada com uma memória

Cache menor e mais veloz

–

–

A Cache geralmente não é visível ao usuário

È usada para melhorar o desempenho

Endereçamento

A memória principal é organizada como um

conjunto de n células (ou posições) capazes de

armazenar, cada uma, m bits.

Cada célula é identificada por um endereço (código

binário associado) de k bits através do qual é

referenciada.

Os endereços são numerados de zero a n-1.

Endereçamento

Existem 2k possíveis endereços. Assim, o máximo

número de células endereçáveis é 2k.

A célula é a menor unidade de memória endereçável

Uma célula poderá armazenar qualquer uma das 2m

possíveis combinações diferentes dos seus m bits.

Onde m é independente de n.

Endereçamento

Os m de bits de uma célula são acessados

simultaneamente

m pode ser qualquer número inteiro mas, nos

últimos anos, os fabricantes padronizaram um

tamanho de 8 bits (1 byte).

Endereçamento

Bytes são agrupados em Palavras

A maioria das instruções opera sobre palavras

Registradores da CPU geralmente são do tamanho

de uma palavra.

Ordenação

Os bytes de uma palavra podem ser numerados da

esquerda para a direita ou da direita para a esquerda

Quando a numeração dos bytes começa da esquerda

para a direita da palavra, a ordenação dos bytes é

dita Big Endian

Quando a numeração dos bytes começa da direita

para a esquerda da palavra, a ordenação dos bytes é

dita Little Endian

Ordenação

Big Endian

Ordenação

Little Endian

Ordenação

Problema: ao transmitir informações de uma

máquina big endian para uma little endian, (ou viceversa), os bytes de uma palavra são invertidos (o

seu valor numérico muda completamente).

Evolução

O aperfeiçoamento das memórias centrou-se no

aumento da sua capacidade de armazenar

O aperfeiçoamento das CPU's centrou-se no seu

desempenho

A memória principal tem grande capacidade de

armazenamento porem seu acesso é lento

Ela pode se tornar um "gargalo" para a CPU, que deve

esperar muito para receber os dados dela

Soluções

É possível projetar uma memória com

velocidade compatível com a CPU?

Sim, mas é muito caro!

Seria possível embutir a memória no chip da

CPU e reduzir o uso do barramento?

Sim, mas existem restrições ao aumento do

tamanho do chip!

A melhor Solução

Memória Cache!

Memória rápida, porem cara e de menor capacidade

Contudo, associada à memória principal, (barata e de

grande capacidade), resulta num sistema:

–

–

–

razoavelmente barato

razoavelmente rápida

de grande capacidade

Memória Cache

Na Cache são mantidas as palavras mais

usadas pelo processador

Se a maior parte dos acessos for resolvida

pela Cache, o tempo médio de acesso será

próximo do tempo de acesso ao Cache, que é

pequeno.

Arquitetura com a Cache

Conexão Lógica entre CPU, Cache e Memória

Principal.

X=X+Y

Notas importantes

O acesso à RAM não é totalmente aleatório

Referências à memória num certo intervalo de

tempo pequeno tendem a acessar uma pequena parte

da memória total

Essa pequena parte é geralmente chamada de bloco

Nestes blocos os endereços estão ordenados numa

seqüência lógica para a execução da CPU

Principio da Localidade

Definição:

–

Existe grande probabilidade que palavras próximas

a uma palavra recentemente referenciada também

sejam referenciadas nos próximos acessos

Aplicação:

–

Quando uma palavra é referenciada pelo

processador, se ela não estiver no Cache, ela é

trazida para o mesmo junto com palavras de

endereços vizinhos na memória principal

Organização

Memória principal é divididas em blocos de

endereços de tamanho fixo

A Cache é dividida em linhas

Sempre que uma endereço procurada não

estiver no Cache o bloco correspondente é

trazido da memória principal

É mais eficiente trazer k endereços de uma

vez do que uma endereço k vezes

Mapeamento

Como associar um dado na memória principal

a uma posição na Cache?

Mapeamento:

–

–

–

Direto

Associativo

Associativo por conjuntos

Mapeamento Direto

Cada bloco da memória principal é mapeado numa

linha na Cache, e cada linha da Cache possui um

rótulo

Como a Cache é muito menor do que a memória

principal, muitos endereços compartilham a mesma

linha

Um endereço é dividido em:

–

–

–

Rótulo

Linha

Palavra

Mapeamento Direto

O campo linha do endereço é usado para

endereçar a Cache e o campo Rótulo do

endereço é comparado com o campo Rótulo

da linha na Cache

É verificado se, dentre as palavras mapeadas

naquele linha existe a palavra que esta sendo

buscada

Mapeamento Direto

Endereços diferentes são mapeados na mesmo linha

Isso pode comprometer o desempenho, pois

palavras irrelevantes podem estar armazenadas na

mesma linha, enquanto palavras importantes podem

estar armazenadas em linhas diferentes da Cache

Se elas estão em diferentes linhas levará mais tempo

para encontra-las

Mapeamento Associativo

Permite que cada bloco da memória seja

carregado em qualquer linha da Cache

Nesse sistema a Cache é formada apenas por

um Rótulo e uma Palavra

Um rótulo identifica um bloco da memória

principal

Mapeamento Associativo

A busca de uma palavra na cache envolve duas

fases:

Determinação do número do bloco a partir do

endereço

–

Obtido dividindo o endereço pelo tamanho b do bloco.

Busca da linha que contém este número de bloco

–

Comparar simultaneamente os campos de número de

bloco de todos os linhas com o número de bloco

procurado

Mapeamento Associativo

Na cache associativa, a ordem das entradas é

aleatória

O microprograma busca a palavra na cache e, se não

estiver lá, vai a memória principal armazenando-a

Caso a cache esteja cheia alguma palavra deverá ser

descartada, de acordo com uma política de

substituição adequada

Comparação

Direto vs Associativo

Memória Secundaria

Memória de grande capacidade (dezenas de

Gigabytes).

Armazenamento massivo

Implementada em meio magnético (hard disk, fitas

magnéticas) ou ótico (CD-ROM, DVD-ROM).

Armazena programas e dados não processados

correntemente, mas que poderão eventualmente ser

utilizados (freqüência de acesso pequena).

Memória Secundária

Memória lenta e barata

Tempo de acesso da ordem de milissegundos

Pode também ser utilizada para emular memória

principal

Isso aumenta o espaço de endereçamento disponível

através de técnicas de memória virtual

Disco Magnético

Constituído de um prato circular de metal ou

de plástico, coberto com um material que pode

ser magnetizado

Os dados são gravados e posteriormente lidos

por meio de uma bobina chamada cabeçote

Durante a leitura o cabeçote permanece

estático, enquanto o disco gira embaixo dele

Durante a escrita ele emite pulsos magneticos

que gravam os dados no disco

Disco Magnético

Os dados são organizados no disco em forma

de círculos concêntricos chamados de trilha

Cada trilha tem a mesma largura do cabeçote

Disco Magnético

Trilhas adjacentes são separadas por espaços

Isso evita a ocorrência de erros devido a falta

de alinhamento do cabeçote ou a interferência

de campos magnéticos

Os dados são transferidos de e para o disco

em blocos

Os dados são armazenados em regiões do

tamanho de um bloco, chamadas setores

Características físicas

Movimento do cabeçote

–

–

Fixo – Existe um cabeçote para cada trilha

Móvel – Um por disco, que se move para alcançar

as trilhas

Transportabilidade do disco

–

–

Não-Removível – Montado permanentemente na

unidade de disco

Removível – Pode ser substituído por outro disco

na unidade

Características físicas

Lados

–

–

Único – Só um lado do disco é magnetizável

Duplo – Os dois lados são magnetizáveis

Pratos

–

–

Único

Múltiplos

Características físicas

Mecanismo do Cabeçote

–

Contato – O cabeçote toca o disco

–

Espaço Fixo – O cabeçote é posicionado a uma

certa de distancia do disco

–

Esta sujeito a erros mais barato

Os dados trafegam mais devagar que o anterior

Espaço Aerodinâmico – Evolução do mecanismo de

espaço físico, com cabeçote mais estreito e mais

próximo do disco

Características físicas

Cabeçote com Espaço Aerodinâmico

–

–

–

–

Aumenta a densidade de dados que trafegam

Disco fica envolvido numa região quase sem ar,

livre de varias impurezas

O cabeçote tem formato aerodinâmico

Foi desenvolvido para o modelo de disco

Winchester

Memória Óptica

Desenvolvida a partir de 1983

Surgiu com o CD

Era destinado apenas para o armazenamento

de áudio digital

Com CD-ROM passou a armazenar dados

Evoluiu para DVD, inicialmente proposto para

armazenar vídeo de alta qualidade

Memória Óptica

O disco é constituído de uma resina de

policarbonato

È depois revestida com uma superfície com

alto índice de reflexão

–

Geralmente alumínio

A informação digital é registrada na superfície

reflexiva como uma serie de sulcos

microscópicos

Memória Óptica

A gravação é feita primeiro com um laser de alta

intensidade muito bem focado para criar a um disco

matriz

Essa matriz é um molde para as cópias

A superfície sulcada é protegida contra pó e

arranhões

Memória Óptica

A leitura é feita com um laser de baixa

potencia

O feixe passa através da cobertura protetora

enquanto o motor gira o disco

Ao encontrar um sulco a intensidade da luz

muda

Essa mudança é detectada por um foto-sensor

e convertida num sinal digital