DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO

BACHARELADO EM INFORMÁTICA

SISTEMAS OPERACIONAIS I

10 SEM/03

Teste 2 – Unidades I e II

DURAÇÃO: 45 MINUTOS

Aluno: ________________________________________________ Escore: __________

1a Questão

Responda as perguntas de forma objetiva e organizada. Mostre o desenvolvimento da questão e

destaque de forma clara o resultado encontrado.

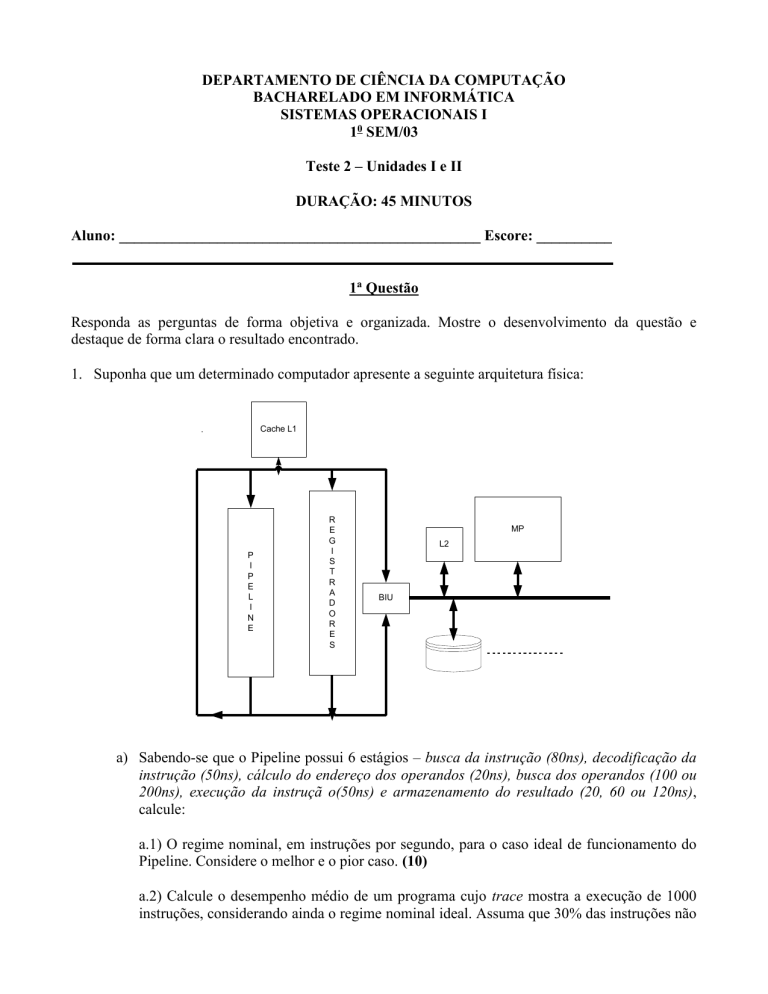

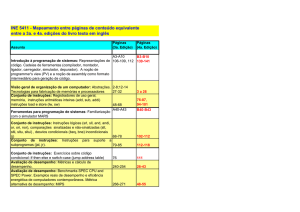

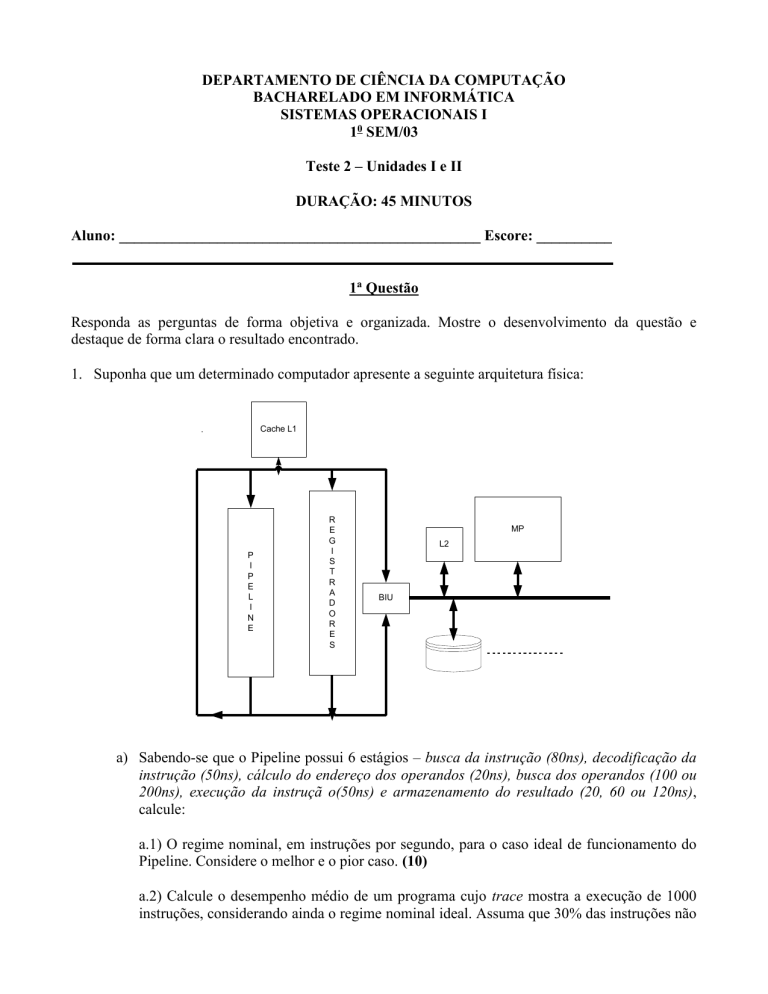

1. Suponha que um determinado computador apresente a seguinte arquitetura física:

Cache L1

P

I

P

E

L

I

N

E

R

E

G

I

S

T

R

A

D

O

R

E

S

MP

L2

BIU

a) Sabendo-se que o Pipeline possui 6 estágios – busca da instrução (80ns), decodificação da

instrução (50ns), cálculo do endereço dos operandos (20ns), busca dos operandos (100 ou

200ns), execução da instruçã o(50ns) e armazenamento do resultado (20, 60 ou 120ns),

calcule:

a.1) O regime nominal, em instruções por segundo, para o caso ideal de funcionamento do

Pipeline. Considere o melhor e o pior caso. (10)

a.2) Calcule o desempenho médio de um programa cujo trace mostra a execução de 1000

instruções, considerando ainda o regime nominal ideal. Assuma que 30% das instruções não

possuem operandos; 20% possuem um operando do tipo imediato e outro em memória, o

resultado é armazenado em registrador; 10% possuem os 2 operandos em memória e o

resultado é armazenado em registrador e, finalmente, 40% possuem 3 operandos em

memória. (20)

a.3) Seja Pj a probabilidade de que uma determinada instrução seja um desvio condicional,

Pt a probabilidade de que o desvio pelo else seja efetuado (o projetista optou por assumir

como default a saída pelo then) e b a penalidade decorrente da realização do desvio; PD a

probabilidade de que a instrução dependa do resultado da instrução imediatamente anterior e

c a penalidade correspondente. Formule uma expressão que mostre o tempo médio de

resposta para o pipeline (ciclos/instrução). (Dica – lembre que o desempenho de um pipeline

ideal é de 1 ciclo / instrução) (20)

b) Sabendo-se que a hierarquia de memória adotada pelo sistema inclui uma Cache interna L1,

cujo tempo de resposta é de 10ns, uma Cache externa L2, com resposta de 30ns, uma

memória principal com resposta de 120ns e uma memória virtual com tempo médio de

resposta da ordem de 1s.

b.1) Apresente uma fórmula que permita calcular o tempo efetivo médio (esperado) com

base nesta hierarquia apresentada. (10)

b.2) Se a memória principal tem 256Mbytes e a cache L2 é do tipo de acesso direto com

tamanho de bloco de 32 bytes e TAG de 14 bits, calcule o número de entradas da cache e o

tamanho da mesma em bits. (20)

2a Questão

Assinale a(s) resposta(s) que considerar correta(s) – pode haver mais de uma resposta correta em cada

questão. Se não estiver convicto marque apenas uma resposta, pois cada resposta errada além da

primeira, anula uma correta. (5 pontos para cada resposta correta)

1. No funcionamento real de uma estrutura Pipeline, cujo custo pela ocorrência de desvios

condicionais seja b unidades de tempo, o de desvios incondicionais seja c unidades de tempo e o

pela ocorrência de instruções com dependência de dados seja d unidades de tempo, pode-se esperar

que:

A) b > c > d

B) d > c > b

C) d > b > c

D) d > b e b = c

2. A estratégia adotada na implementação de um esquema para tratamento de interrupções inclui:

A) Operações realizadas em nível de hardware e operações em nível de software

B) Pré-salvamento dos registradores conhecidos por PC, PSW e IR

C) Salvamento e restauração de registradores sob a responsabilidade de quem escreve a RTI

D) A parada do processo corrente e o desvio da execução para a RTI

3. A Tabela de Interrupções:

A) Contém o endereço do dispositivo que solicitou a interrupção

B) É uma área de memória com o endereço da rotina de tratamento da interrupção

C) É uma área no início da memória onde o sistema salva os dados do processo corrente

D) Contém as rotinas de serviço do sistema operacional para o tratamento de interrupção

4. Dentre as estratégias de implementação de um sistema de E/S, pode-se afirmar que:

A) A CPU é sempre a responsável pela transferência dos dados de / para a memória principal

B) As interrupções de hardware são assíncronas e verificadas ao final do ciclo de instrução

C) Na E/S programada a CPU fica ociosa (idle) enquanto aguarda a resposta do periférico

D) O DMA por roubo de ciclo é mais transparente para a CPU do que o por transferência de blocos

5. A introdução do endereço relativo das instruções foi um grande avanço na concepção de um

computador. Com o endereçamento relativo surgiu a possibilidade de:

A) Carregar o programa em posições não necessariamente contíguas de memória.

B) Carregar o programa a partir de qualquer posição livre de memória

C) Mapear o ER para o EA tanto em tempo de carga como de execução

D) Ampliar a capacidade de memória dos computadores

6. Com o surgimento das redes de computadores, o conceito de multiprocessamento precisou ser

adaptado para:

A) Incluir as opções de fortemente acoplado para as LANs e fracamente acoplado para as WANs

B) Atender os casos em que um mesmo computador possui múltiplas CPUs e pertence a uma LAN

C) Distinguir as arquiteturas baseadas em múltiplos processadores das de múltiplos computadores

D) Permitir a execução simultânea de instruções e programas em diferentes computadores da rede

7. Sistema Multiprogramável é aquele que:

A) Possibilita o processamento concorrente de dois ou mais processos

B) Permite ao usuário um ganho efetivo de desempenho na execução do seu programa

C) Atende vários usuários em regime de Time-Sharing e outros em Batch interativo

D) Roda programas em foreground, em background, em real time e em pipeline

8. Dentre as formas de implementação de um sistema operacional, pode-se afirmar que:

A) A que implica no menor requisito de espaço em memória é a cliente-servidor

B) Em termos de eficácia (desempenho do código) ganha o SO monolítico

C) Em termos de flexibilidade de configuração ganha o SO modular

D) Quanto ao tempo de resposta, o mais eficiente é o SO multiprogramado

9. Num sistema multiprogramado onde supostamente um programa consuma 20% do tempo da CPU,

a execução concorrente:

A) De 5 programas garante um idle time de 0% para a CPU

B) De 5 ou mesmo mais programas não garante o uso completo do tempo da CPU

C) De mais programas aumenta o throughput do sistema

D) De 2 programas reduz o tempo ocioso da CPU em 50%

10. O surgimento dos minicomputadores no final da década de 60 possibilitou às empresas adotarem

uma nova filosofia de processamento que:

A) Foi chamada de teleprocessamento

B) Permitiu a redução de custos e a descentralização de operações como a entrada de dados

C) Acabou com o reinado dos computadores conhecidos como mainframes

D) Resultou no surgimento das redes locais e remotas de computadores e também na Internet