UNIVERSIDADE FEDERAL DO PARÁ

CENTRO TECNOLÓGICO

DEPARTAMENTO DE ENGENHARIA ELÉTRICA

CURSO:

MICROPROCESSADORES

Prof.: Marcelo Barretto

Mestre em Engenharia Elétrica - PUC/RJ

Professor Adjunto IV

Especialista em Redes Locais de Computadores

Ano: 2000

Microprocessadores

_________________________________________________________________________________________________

____

Sumário

Capítulo 1: Conceitos Básicos

1.1

1.2

1.3

1.4

1.5

1.6

1.7

1.8

- Histórico

- CPU, Memórias e Dispositivos de Entrada/Saída

- Sistema de Barramentos

- Arquitetura Padrão de um Microprocessador

- Execução de Instruções em Microprocessadores

- Algumas Instruções Importantes

- Capacidade de Interrupção

- Técnicas de Entrada/Saída

Capítulo 2: Os Microprocessadores da INTEL

2.1. O 8086/8088

2.1.1. Arquitetura

2.1.2.

Características Gerais

2.1.3.

Capacidade de Interrupção

2.2. O 80286

2.2.1.

Arquitetura e Características

2.2.2.

Diferenças no Conjunto de Instruções

2.2.3.

Implicações no Desempenho de um Microcomputador

2.3. Os 80386

2.3.1 - Diferenças de Arquitetura e Características

2.3.2 - Diferenças no Conjunto de Instruções

2.3.3 - Versões 80386, 80386SX e 80386SL

2.3.4 - Implicações no Desempenho de um Microcomputador

2.4 - Os i486

2.4.1 - Diferenças de Arquitetura e Características

2.4.2 - Diferenças na Capacidade de Processamento

2.5 - Os Pentium, Pentium MMX e PRO

2.5.1 - Diferenças de Arquitetura e Características

2.5.2 - Benchmarks

2.6 - Os Pentium II

2.6.1 - Arquitetura e Características

2.6.2 - Benchmarks

2.6.3 - Implicações no Desempenho de Desktops e Servidores de Rede

2.7 – Últimos Microprocessadores da INTEL

Capítulo 3: Características Gerais dos Sistemas de Barramentos

3.1

3.2

3.3

3.4

- Os Barramentos Principais ISA, EISA e MCA

- Os Barramentos Locais Secundários VESA e PCI

- Os Barramentos Secundários IDE e Enhanced IDE

- Os Barramentos Secundários SCSI

Capítulo 4: Suporte ao Desenvolvimento de Software Básico

4.1 - Estrutura de um Programa na Memória

4.2 - Montadores, Carregadores e Depuradores

4.3 - Uso de um Depurador de Linguagem Assembly

Página 2

Microprocessadores

_________________________________________________________________________________________________

____

Capítulo 5: Características Gerais dos Microprocessadores da MOTOROLA

5.1 - O 68.000

5.1.1 - Arquitetura

5.1.2 - Diferenças no Conjunto de Instruções

5.1.3 - Capacidade de Interrupção

5.2 - O 68.010

5.3 - O 68.020

5.4 - O 68.030

5.5 - O 68.040

5.6 – O 68.060

5.7 – Os PowerPC (IBM/Apple/Motorola)

Capítulo 6: Introdução aos Microcontroladores

6.1 - Arquitetura Interna

6.2 - O microcontrolador 8052 da INTEL

6.3 – O MPC860 da Motorola

Capítulo 7: Introdução às Arquiteturas RISC

7.1 - Noções da Arquitetura RISC

7.2 - Implicações no Desempenho de um Computador

Capítulo 8: Arquiteturas Não Convencionais

8.1 - Arquiteturas Paralelas

8.2 - Arquiteturas MIMD

8.3 - Arquiteturas à Passagem de Mensagens

Página 3

Microprocessadores

_________________________________________________________________________________________________

____

CAPÍTULO 1: CONCEITOS BÁSICOS

1.1 - HISTÓRICO

A história dos microprocessadores é brevemente resumida a seguir com o destaque de algumas

datas importantes:

Década de 40: è Válvula e Transistor (1948)

Década de 50: è Comercialização do transistor

Década de 60: è Circuitos Integrados SSI ("Small Scale Integrated")

Década de 70: è Circuitos Integrados MSI ("Medium Scale Integrated")

1971:

=> Circuitos Integrados LSI ("Large Scale Integrated")

=> INTEL 4004 (CPU do primeiro microcomputador de 4 bits)

1972:

=> INTEL 8008 (CPU do primeiro microcomputador de 8 bits)

1974:

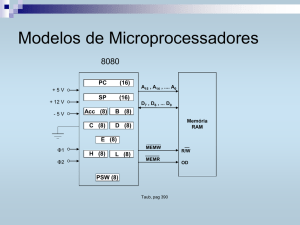

è INTEL 8080 (10 vezes mais rápido que o 8008)

=> MOTOROLA 6800

1976:

=> TEXAS 9800 (CPU do primeiro microcomputador de 16 bits)

1977:

è MOSTEK 6502 ==> Apple I, II e II plus

è ZILOG Z80 ==> TRS-80

1978:

=> Circuitos Integrados VLSI ("Very Large Scale Integrated")

=> MOTOROLA 6809 (Melhor CPU de 8 bits do mercado)

è INTEL 8088/8086 (29.000 transistores integrados)

=> Microprocessadores BIT-SLICE (de 2 a 64 bits)

Década de 80:

1980:

1981:

1982:

1984:

1985:

1986:

1988:

1989:

=> MOTOROLA 68.000 (68.000 transistores integrados)

=> MOTOROLA 68.010

=> INTEL 80186/80188

=> INTEL 80286 (130.000 transistores integrados)

=> MOTOROLA 68.020

=> INTEL 80386 (ou 80386DX, ou i386)

=> MOTOROLA 68.030

=> INTEL 80386SX

=> INTEL i486 (1.200.000 transistores)

Década de 90:

1991:

1992:

1993:

1995:

=> INTEL i386SL, i486SX

ð Microprocessadores com tecnologia RISC

=> INTEL i486DX2/50 e i486DX2/66

=> INTEL Pentium

=> INTEL Pentium Pro

Página 4

Microprocessadores

_________________________________________________________________________________________________

____

1997:

è INTEL Pentium II

Tendências:

ð

ð

ð

ð

ð

ð

Máquinas CISC ou Máquinas RISC

Pentium 166 Mhz è Pentium II a 300 Mhz

Máquina de Controle Seqüencial è Máquina de Controle Paralelo

Máquina de Arquitetura SIMD è Máquina de Arquitetura MIMD ("Data-Flow")

Arquiteturas orientadas p/ o HW è Arquiteturas orientadas p/ o SW

Máquinas processando texto è Máquinas processando dados multimídia

1.2 - CPU, MEMÓRIAS E DISPOSITIVOS DE ENTRADA/SAÍDA

Os próximos parágrafos procuram dar uma idéia da nomenclatura utilizada no restante deste

documento e introduzir os componentes principais da arquitetura de microcomputadores ou de

circuitos controlados a microprocessador.

HARDWARE: consiste de circuitos eletrônicos responsáveis pela execução direta de instruções em

linguagem de máquina: CIs, placa impressa, cabos, fontes de alimentação, etc.

SOFTWARE: consiste de algoritmos e suas representações no computador (programas).

FIRMWARE: consiste de um software embutido em circuitos eletrônicos.

É comum dizer que qualquer operação feita por software pode também ser construída por hardware e

qualquer instrução executada pelo hardware pode também ser simulada por software.

Um sistema de microcomputador típico é mostrado na figura 1. Basicamente, são três os

componentes de qualquer sistema controlado por microprocessador ou mesmo de um sistema de

computação: Unidade Central de Processamento (CPU), Memória e Dispositivos de Entrada/Saída

(E/S).

A CPU tem finalidade óbvia, a de controlar o sistema como um todo. A memória serve para

armazenar os dados que serão manipulados e os dispositivos de E/S para a comunicação da

máquina com o mundo exterior (usuário).

Os vários tipos de Memória são definidos a seguir:

RAM - "Random Access Memory": memória de leitura/escrita, volátil, para armazenamento

temporário de programas e dados;

RAM Estática - RAM com menor densidade e mais rápida que a RAM dinâmica. Não necessita de

circuitos adicionais em um microcomputador.

RAM Dinâmica - RAM com maior densidade e mais lenta que a RAM estática. Necessita de

circuitos adicionais de controle em um microcomputador.

ROM - "Read Only Memory": memória programada quando a pastilha é fabricada, não podendo ser

modificada. É usada para armazenamento permanente de programas e dados;

PROM - "Programmable ROM": memória programada por um dispositivo programador de PROM.

Programável uma única vez;

Página 5

Microprocessadores

_________________________________________________________________________________________________

____

EPROM - "Erasable PROM": memória que pode ser apagada e reprogramada várias vezes. Apagável

pela incidência de raios ultra-violeta e programável por um dispositivo programador de EPROM;

EEPROM - "Erasable Electrically PROM": memória EPROM eletricamente modificável, sem

necessidade de dispositivos externos apagadores ou programadores.

Os Dispositivos de Entrada/Saída são os componentes que viabilizam a interface com o usuário,

tais como: portas seriais, portas paralelas, conversores análogo-digitais, etc

Estes componentes são ligados através de um sistema de barramentos, o qual será explicado na

próxima seção.

Microprocessador

(CPU)

Memória

RAM

Memória

EPROM

Barramento de Endereços

Barramento de Dados

Barramento de Controle

Interfaces

para

Memória

Secundária

Interfaces de

Interação c/

o Usuário

HD

Imp. Matricial

Monitor

Interfaces de

Controle e

Sensoreamento

CD-ROM R/W

Sensor

Válvula

Modem

Scanner

Figura 1 – Sistema de Microcomputador Típico e suas Interfaces

Página 6

Microprocessadores

_________________________________________________________________________________________________

____

1.3 - SISTEMA DE BARRAMENTOS

Um sistema de barramentos é definido como um conjunto físico de linhas de sinal que possuem

funções específicas dentro do sistema.

O sistema de barramentos de um microcomputador é composto de 3 barramentos (ver figura 1)

independentes em suas funções elétricas: o barramento de endereços, o barramento de dados e o

barramento de controle.

O Barramento de Endereços é apenas de saída (em relação CPU) e define o caminho de

comunicação dentro do sistema.

O Barramento de Dados é bidirecional, sendo o meio de comunicação entre os componentes do

sistema. Na saída de dados da CPU, estes são gerados pelo microprocessador (CPU) e enviados à

uma unidade que é selecionada pelo barramento de endereços. Na entrada de dados, estes são

gerados por uma unidade particular e enviados ao microprocessador.

O Barramento de Controle, como o próprio nome indica, envia e recebe os sinais de controle

necessários à transferência de dados no sistema. Este barramento é composto, basicamente, de 4

tipos de sinais: leitura de memória ativa, escrita de memória ativa, entrada através de dispositivo

externo ativo e saída através de dispositivo externo ativo.

1.4 - ARQUITETURA PADRÃO DE UM MICROPROCESSADOR

Depois de se examinar um sistema de microcomputador de forma global, nesta seção será

apresentada a arquitetura padrão de um microprocessador, exibida na figura 2. Destacam-se os

seguintes blocos:

Registrador de Instrução (RI) - registrador que armazena a instrução sendo executada;

Contador de programa ("Program Counter - PC") - registrador que armazena o endereço de

memória da próxima instrução a ser executada;

Acumulador - registrador que contém o dado a ser processado;

Apontador de pilha ("Stack Pointer - SP") - registrador que aponta para o endereço de retorno de

subrotina, sendo este último armazenado em uma pilha na memória;

Unidade Lógica e Aritmética (ULA) - circuito combinacional utilizado para operações lógicas e

aritméticas envolvendo dois operandos;

Decodificador de instruções - circuito combinacional utilizado para determinar qual a próxima

instrução a ser executada. Isto é feito a partir do código de operação armazenado previamente no

Registrador de Instrução;

Unidade de controle - circuito seqüencial interno ao microprocessador utilizado para gerar os

sinais de controle necessários à execução da instrução previamente decodificada;

Registradores auxiliares - conjunto de registradores de rascunho que podem ser usados em

conjunto ou separadamente para operações intermediárias, sem que seja necessário o acesso

sistemático à memória;

Página 7

Microprocessadores

_________________________________________________________________________________________________

____

Flags – conjunto de Flip-Flops destinados a guardar as condições resultantes da execução de

instruções. Tais flags são fundamentais no sentido em que se constituem no único mecanismo que o

programador Assembly dispõe para desvios de processamento e implementação de algoritmos.

Barramento de

Dados

Buffer de

Dados

Acumulador

RI

Código de

Instrução

Informação

Complementar

Decodificador

X

R1

SP

Apontador

de Pilha

..

.

PC

Contador de

Programa

Rn

Unidade Lógica e

Aritmética (ALU)

Registradores de

Rascunho

Unidade de

Controle

S

Z

CY

AC

Buffer de Endereço

Sinais de

Controle

P

Flags

Barramento de

Endereços

Figura 2 – Arquitetura Padrão de um Microprocessador

1.5 - EXECUÇÃO DE INSTRUÇÕES EM MICROPROCESSADORES

Nesta seção serão dadas as explicações básicas para o entendimento dos microprocessadores

mais comuns do mercado.

Antes de mostrar o procedimento de execução de instruções é necessário detalhar alguns aspectos:

os flags de condição, o formato das instruções e as operações básicas (de leitura e escrita) de um

microprocessador.

Flags de Condição:

Um "flag" é "SETADO", forçando-se o bit de flag para "1" e é "RESETADO", forçando-se o bit de flag

para "0". Quando uma instrução afeta um flag este é alterado da seguinte maneira:

ZERO: Se o resultado da instrução tem valor 0,

Página 8

Microprocessadores

_________________________________________________________________________________________________

____

então Z è 1

senão Z è 0;

SINAL: Se o bit mais significativo do resultado da operação tem valor 1,

então S è 1

senão S è 0;

PARIDADE: Se a soma dos bits do resultado da operação é 0,

então P è 1 (paridade PAR)

senão P è 0 (paridade ÍMPAR);

CARRY: Se o resultado da instrução provoca um "carry" (na adição) ou um "borrow" (na subtração ou

comparação),

então C è 1

senão C è 0;

CARRY AUXILIAR: Se a instrução causou um carry do bit 3 para o bit 4,

então AC è 1

senão AC è 0.

Cada microprocessador tem seus próprios bits de flag. Os flags anteriormente mencionados são os

mais comuns de serem encontrados na maioria dos microprocessadores.

Mostra-se a seguir o formato de instrução, por exemplo, de um microprocessador de 8 bits. A

partir deste entendimento, pode-se por analogia, entender o formato de instruções de outros

microprocessadores. Assim, o formato de instrução do INTEL 8085 é utilizado como exemplo básico.

Formato de Instrução e dado no 8085

1. Instruções de um byte

D7 D6 D5 D4 D3 D2 D1 D0

Código de Operação

Ex.:

MOV R1,R2 ; R1 <- R2

Obs.: O endereço do primeiro byte das instruções é sempre usado como o endereço de instrução.

2. Instruções de dois bytes

D7 D6 D5 D4 D3 D2 D1 D0

Código de Operação

D7 D6 D5 D4 D3 D2 D1 D0

Info. Complementar

Ex.:

MVI R,dado ; R <- dado

3. Instruções de três bytes

Página 9

Microprocessadores

_________________________________________________________________________________________________

____

D7 D6 D5 D4 D3 D2 D1 D0

Código de Operação

D7 D6 D5 D4 D3 D2 D1 D0

Info. Complementar

D7 D6 D5 D4 D3 D2 D1 D0

Info. Complementar

Ex.: LXI Rp, dado 16 ; Rh <- (byte3)

; Rl <- (byte 2)

Nas seções anteriores foram mostrados os componentes básicos de um circuito controlado a

microprocessador, a arquitetura padrão dos microprocessadores e a CPU do sistema. Isto era

indispensável para a compreensão do capítulo e do curso como um todo.

Ainda com o intuito de mostrar como instruções são executadas em microprocessadores, também

se faz necessário explicar as operações básicas de um computador ou circuito controlado a

microprocessador. Estas, são as operações de leitura de memória e escrita na memória.

Operações Básicas de um Computador:

Operação de Leitura:

1. A memória recebe o endereço e a solicitação de leitura;

2. A memória localiza a célula decodificando o endereço;

3. Operação de leitura propriamente dita;

4. Intervalo em que a memória não é acessível por razões técnicas ("Descanso").

Ciclo de Acesso à Memória: fases 1, 2 e 3

Ciclo da Memória: fases 1, 2, 3 e 4

Operação de Escrita:

1. A memória recebe o endereço, o dado e uma solicitação de escrita;

2. A memória localiza a célula decodificando o endereço;

3. Operação de escrita propriamente dita;

Página 10

Microprocessadores

_________________________________________________________________________________________________

____

4. ("Descanso").

Obs.: A operação de leitura é muito mais freqüente que a operação de escrita.

Ciclo de Instrução

Uma instrução é executada por um microprocessador durante um intervalo de tempo particular à

instrução, chamado, CICLO DE INSTRUÇÃO. Um ciclo de instrução é composto de vários ciclos de

máquina que variam de acordo com a instrução. Cada ciclo de máquina, por sua vez tem a duração

de vários períodos de relógio. Em seguida, o ciclo de instrução é detalhado.

O formato da instrução em linguagem de máquina é mostrado a seguir. Com base neste formato

pode-se descrever textualmente o ciclo de instrução.

Linguagem de Máquina ==>

Código de Operação

Informação Complementar

CICLO DE INSTRUÇÃO:

1. BUSCA

a) Envio de um endereço para a memória e execução de uma leitura;

b) Incremento do registrador de endereço de instrução;

2. EXECUÇÃO

a) Decodificação do código de operação;

b) Execução da instrução;

3. VOLTA PARA FASE 1

--> Pode haver desvio:

- Incondicional: o valor do registro de endereço de instrução é alterado;

- Condicional: se a condição é satisfeita, a seqüência linear é interrompida.

É importante ressaltar que cada ciclo de instrução é composto por vários ciclos de máquina..

A figura 3 procura ilustrar o procedimento de execução de um pequeno programa, passo-a-passo, já

armazenado na memória e a figura 4 mostra, sob a forma de diagrama de tempo, a execução da

instrução LDA 0420, com todos os seus ciclos de máquina e períodos de relógio.

Página 11

Microprocessadores

_________________________________________________________________________________________________

____

5

Caracter "A" do teclado

Porta de

Entrada 01

5

5

Acumulador

16

Registrador de

Instrução

Microprocessador

1

3

6

8

12

14

Endereço

0100

0101

0102

0103

0104

0105

0106

0107

Conteúdo

IN

01

STA

00

20

OUT

10

...

2

4

7

9

13

15

Memória de Programa

10

Endereço

2000

2001

2002

2003

Conteúdo

A

11

Memória de Dados

16

Porta de

Saída 10

16

Caracter "A" para o

monitor de Vídeo

Figura 3 – Execução de Instruções por um Microprocessador Passo-a-Passo

Página 12

Microprocessadores

_________________________________________________________________________________________________

____

T1 T2 T3 T4 T5

T1 T2 T3 T4 T5 T 1 T2 T3 T4

T5 T1 T2 T 3 T 4 T 5

Fase

Busca

Exec.

Busca

Exec.

Busca

Exec.

Busca

Exec.

Ciclo

Ciclo

M1

Ciclo

M2

Ciclo

M3

Ciclo

M4

Oper.

RI <- LDA

Não

Usado

Não

Usado

RI <- 20

Não

Usado

PC

1001

->1002

1003

1004

Busca do

Código de

Operação da

Instrução e

Transferência

deste código

para o

Registrador de

Instrução (RI)

RI <- 04

1002

->1003

Busca do

primeirobyte do

endereço e

transferência

para dentro da

parte de

endereço do RI,

byte demenor

ordem

Busca do

segundobyte

do endereço e

transferência

para dentro da

parte de

endereço do RI,

byte demaior

ordem

Bar.

A <Dados (0420)

<-(0420)

1004

A parte de

endereço do RI é

depositada no

barramento de

endereços

Acumulador

recebe o conteúdo

da posição de

memória, cujo

endereço é 0420

RI

Figura 4 – Execução da Instrução LDA 0420

1.6 - ALGUMAS INSTRUÇÕES IMPORTANTES

Normalmente, pode-se separar as instruções de linguagem Assembly de um microprocessador em

grupos. Tais grupos podem ser generalizados para a maioria dos microprocessadores com algumas

pequenas diferenças. A título de exemplo, os grupos de instruções no 8085 são mostrados abaixo.

Página 13

Microprocessadores

_________________________________________________________________________________________________

____

Grupo de Transferência de Dados

Move dados entre registradores ou entre locações de memória e registradores;

Ex.: "MOVEs", "LOADs", "STOREs" e EXCHANGE;

Grupo Aritmético

"ADDs", "SUBTRACTs", "INCREMENTs" ou DECREMENTs" dados nos registradores ou na

memória;

Grupo Lógico

"ANDs", "ORs", "XO Rs", "COMPAREs", "ROTATEs" ou

registradores ou entre locações de memória e registradores;

"COMPLEMENTs"

dados

entre

Grupo de Salto

"JUMPs", "CALLs" e "RETs" condicionais ou incondicionais;

Grupo de Instruções de Pilha, E/S e Controle de Máquina

Inclui instruções de manutenção de pilha, leitura escrita na/da memória, "seta" ou lê máscaras de

interrupção, seta ou limpa "FLAGs"

1.7 – CAPACIDADE DE INTERRUPÇÃO

Uma das técnicas de Entrada/Saída de dados mais utilizadas na atualidade é a Interrupção. Seu uso

aplica-se tanto em computadores de um modo geral, como também no ambiente de automação

industrial.

INTERRUPÇÃO (IRQ) é um sinal de hardware enviado por um dispositivo periférico necessitando de

imediata atenção da CPU. A utilização desta técnica, forçosamente, envolve sinais de hardware.

É comum em softwares de apoio tradicionais, como o Norton Utilities, observar a distinção entre

Interrupções por Hardware e por Software. Segundo nomenclatura da INTEL, a diferença básica é que

na Interrupção por Hardware , o endereço de salto, para o qual o microprocessador irá desviar o

processamento é predefinido pelo hardware do microprocessador, enquanto que na Interrupção por

Software, este endereço de salto pode ser alterado pelo usuário programador Assembly.

Um outro conceito relacionado as interrupções também merece ser comentado. É o mascaramento

de Interrupções. Existem as Interrupções Mascaráveis e as Interrupções Não Mascaráveis.

Quando as Interrupções são Mascaráveis o processador tem a capacidade de não aceitar o pedido

de interrupção do periférico, deixando-o pendente, de tal forma que possa atendê-lo um tempo

depois. Já nas Interrupções Não Mascaráveis, o processador não pode fazer isso, sendo obrigado a

atender imediatamente a solicitação de interrupção do periférico.

A fim de exemplificar estes conceitos e subsidiar as explicações sobre o mecanismo de Interrupção,

é fornecida a seguir a sintaxe e a semântica de uma instrução básica para o entendimento deste

mecanismo, a instrução RESTART.

Página 14

Microprocessadores

_________________________________________________________________________________________________

____

Instrução RST n (Restart)

RST é uma instrução CALL de propósito especial. RST "push" ou "empurra" bytes do Program

Counter (PC) sobre a pilha e então faz a CPU saltar para um dentre vários endereços

predeterminados.

((SP) - 1) <-- (PCH)

((SP) - 2) <-- (PCL)

(SP) <-- (SP) - 2

(PC) <-- 8 * (NNN)

NNN - Número binário entre 000 e 111 (entre 0 e 7 em decimal)

SP - Stack Pointer

PCH - Byte mais significativo do Program Counter

PCL - Byte menos significativo do Program Counter

Ex.: Endereços de salto possíveis no INTEL 8085:

HEXADECIMAL

0000

0008

0010

0018

0020

0024

0028

002C

0030

0034

0038

003C

DECIMAL

0

8

16

24

32

36

40

44

48

52

56

60

RST

0

1

2

3

4

TRAP

5

5.5

6

6.5

7

7.5

Interrupções por Hardware:

Ex.: O 8085 inclui 4 sinais de entrada (hardware) que geram internamente instruções RST:

RST 5.5, RST 6.5 e RST 7.5 (Mascaráveis)

TRAP (não Mascarável)

Interrupções por Software:

Quando um dispositivo de E/S pede o serviço de interrupção e a IRQ está habilitada pelo sistema de

interrupção do processador, este reconhece o pedido e prepara suas linhas de dados para aceitar

qualquer instrução de um byte do dispositivo. RST é geralmente a instrução escolhida, pois é uma

instrução CALL de propósito especial que estabelece o retorno ao programa principal.

Ex.: O 8085 possui 1 entrada e 1 saída que implementa este tipo de interrupção

INTR – pino de entrada

INTA – pino de saída

Página 15

Microprocessadores

_________________________________________________________________________________________________

____

Para o processador não se confundir, ao receber dois pedidos de interrupção simultâneos, é provido

um mecanismo de prioridade que estabelece uma ordem no atendimento destes pedidos.

Prioridade das Interrupções no 8085

NOME

PRIORIDADE

ENDEREÇO DE SALTO (1)

TRAP

1

0024H

RST 7.5

RST 6.5

RST 5.5

INTR

2

3

4

5

003CH

0034H

002CH

(2)

TIPO DE "TRIGGER"³

Pulso Positivo amostrado

até Alto Nível

Pulso Positivo "Latched"

Sensível a Nível (Alto)

Sensível a Nível (Alto)

Sensível a Nível (Alto)

(1) – O processador coloca o conteúdo do Program Counter sobre a pilha, antes de saltar para o

endereço indicado

(2) - Depende da Instrução fornecida a CPU quando a Interrupção é reconhecida

A figura 5 ilustra o mecanismo de Interrupção no 8085. A figura 6 mostra o mesmo para o ZILOG Z80

e a figura 7 exibe os circuitos integrados típicos dos ambientes INTEL e ZILOG. É importante

ressaltar a diferença entre os mecanismos de prioridade de interrupção das duas empresas.

Página 16

Microprocessadores

_________________________________________________________________________________________________

____

INTEL

8085

1

INTR

2

INTA

3

RST nn

Dispositivo

Periférico

Ex.: RST 7

3

4

Endereço

0038

0039

003A

2

Dado

C3 (JMP)

00

80

Programa sendo executado

6001

6002

6003

1

INTR

6

Pilha

(SP)

02

60

Subrotina de Serviço de

Interrupção

8000

5

...

...

RET

Figura 5 – Mecanismo de Interrupção no INTEL 8085

Página 17

Microprocessadores

_________________________________________________________________________________________________

____

___

INT

____

INTA

1

ZILOG

Z80

2

Dispositivo

Periférico

I

Registrador da CPU

80

80

Programa sendo executado

4002

4003

4004

2

Pilha

(SP)

60XX

4

1 ___

INT

6

3

04

40

Subrotina de Serviço de

Interrupção

6050

04

5

...

...

RETI

Tabela de Endereços de

Interrupção

8003

8004

50

8005

60

8006

Figura 6 – Mecanismo de Interrupção (Modo 2) no ZILOG Z80

Página 18

Microprocessadores

_________________________________________________________________________________________________

____

PIO

DMA

Barramentos

Z80

CPU

Mecanismo

"Daisy Chain"

CTC

SIO

Prioridade Fixa

8274

8253

Barramentos

8085

CPU

8259

(PIC)

8257

8272

Prioridade

Controlada

Figura 7 – Mecanismos de Prioridade de Interrupção ZILOG e INTEL

8259 – Controlador de Prioridade de Interrupção (PIC)

8257 – Controlador de DMA Programável (PDC)

8272 – Controlador de Disco Flexível

8274 – Controlador Serial Multiprotocolo

8273 – Temporizador Programável

1.8 – TÉCNICAS DE ENTRADA E SAÍDA

Página 19

Microprocessadores

_________________________________________________________________________________________________

____

Além da técnica de Interrupção detalhada na seção anterior, existem duas outras técnicas, também

muito utilizadas em sistemas de computação de um modo geral. São estas: "Polling" e Acesso

Direto à Memória (ou DMA – “Direct Access Memory”).

"POLLING": É uma técnica de Entrada/Saída de dados onde a CPU, explicitamente, consulta o

periférico com o objetivo de saber se o mesmo possui dados para transmitir ou se está livre para os

receber. Esta técnica não envolve sinais de hardware e pode ser implementada por software;

ACESSO DIRETO À MEMÓRIA: É uma técnica de Entrada/Saída de dados onde a CPU não

participa do processo de transferência de dados, exceto no seu início e após o seu término. Um

outro dispositivo periférico é necessário, o chamado "Controlador de DMA", para assumir o controle

dos barramentos do sistema e controlar as transferências de dados.

Na maior parte dos casos, o uso desta técnica obriga o uso combinado das anteriores para que o

processo de transferência de dados seja iniciado e terminado corretamente. A figura 8 ilustra passoa-passo o procedimento de transferência de dados para a ou da memória, sem interferência da CPU.

Memória

Disp. 0

Disp. 1

Barramentos

s

do

Da

CPU

2

HOLD

CDMA

3 HOLDA

DRQ

1

Disp. 3

Disp. 2

DACK

4

Driver Óptico

Figura 8 – Entrada/Saída por Acesso Direto à Memória

1 – DRQ – “Data Request”: Solicitação de Acesso Direto à Memória feito pelo dispositivo periférico ao

Controlador de DMA (CDMA);

2 – HOLD – “Hold Request: Solicitação de controle de barramentos feito pelo CDMA ao processador;

3 – HLDA – “Hold Acknowledgement” – Resposta do processador ao CDMA, avisando que à partir

daquele momento, este poderá assumir o controle temporário dos barramentos para a

transferência de dados;

4 – DACK – “Data Acknowledgement” – Resposta do CDMA ao dispositivo periférico, avisando que

assumiu o controle dos barramentos e a transferência de dados poderá se iniciar.

A programação do CDMA consiste basicamente de informar o mesmo sobre o endereço inicial do

bloco de bytes a ser transferido, o sentido da transferência e o tamanho de bloco ou o endereço final.

Depois que os comandos são fornecidos ao dispositivo periférico o processo continua, sem

Página 20

Microprocessadores

_________________________________________________________________________________________________

____

interferência da CPU. Após a transferência, o sinal DRQ é retirado, consequentemente, todos os

outros sinais são retirados e a CPU reassume o controle dos barramentos.

Página 21

Microprocessadores

_________________________________________________________________________________________________

____

CAPÍTULO 2: OS MICROPROCESSADORES DA INT EL

2.1 – O 8086/8088

A figura 9 exibe o Diagrama em Blocos da Arquitetura do 8086.

2.1.1 – Arquitetura

Unidade de Execução

AH

BH

CH

DH

AL

BL

CL

DL

SP

BP

SI

DI

Unidade de Interface de

Barramento

0000

IP

CS

DS

SS

ES

0000

0000

0000

0000

Unidade de Controle de

Barramento

ALU (Unidade Lógica e

Aritmética)

Unidade de Controle

1

2

3

4

5

6

Status

Fila de Código Objeto

de Instrução

Registrador de Instrução

Figura 9 – Arquitetura do 8086

Fonte: "The 8086 Book", Rector R. e Alexy G. - OSBORNE/McGraw-Hill

Página 22

Microprocessadores

_________________________________________________________________________________________________

____

Registradores do 8086/8088

Registrador

AX = AH + AL

BX = BH + BL

CX = CH + CL

DX = DH + DL

SP

BP

SI

DI

IP

Flags H + Flags L

CS

DS

SS

ES

Finalidade

Acumulador

Base (2º acumulador)

Contador (usado em instruções de múltiplas interações)

Dado (algumas instruções movem dados de uma porta de E/S para a posição

de memória endereçada por DX)

Apontador de Pilha

Apontador de Base

Índice Fonte

Índice Destino

Apontador de Instrução

Flags

Segmento de Código

Segmento de Dados

Segmento de Pilha

Segmento Extra

Observações:

1.

2.

3.

4.

O registrador SP está estreitamente ligado ao ES, em função das operações relacionadas à

manutenção da pilha;

O registrador IP está estreitamente ligado ao CS, em função das operações relacionadas à

execução de instruções;

O endereço fonte de um String de dados é obtido à partir de SI + DS;

O endereço destino de um String de dados é obtido à partir de DI + ES.

2.1.2 – Características Gerais

Capacidade de Endereçamento:

20 bits de endereçamento => 1.0 Megabytes ou 512 Kwords

Operações com: Bit, Byte, Word e Bloco

Organização da Memória:

a) Física: => 2 x 512 Kbytes. End. Ímpar (D7 – D0)

End. Par (D15-D8)

b) Endereçamento relativo à base de endereços de Registradores de Segmento: Code (CS),

Data (DS), Stack (SS) e Extra (ES).

Endereço

Registrador

Conteúdo

End. da Memória de Programa

IP

CS

(IP+CS) Endereço Final è

0MMMM

NNNN0

PPPPM

Página 23

Microprocessadores

_________________________________________________________________________________________________

____

End. da Memória de Dados

XX

DS

(XX+DS) Endereço Final è

0MMMM

NNNN0

DDDDM

End. da Memória de Pilha

XX

SS

(XX+SS) Endereço Final è

0MMMM

NNNN0

SSSSM

End. da Memória Extra

XX

ES

(XX+ES) Endereço Final è

0MMMM

NNNN0

DDDDM

Observações:

1.

2.

Cada registrador de segmento (16 bits) identifica o início de um segmento 64 Kbytes. Como são

4 (quatro) os registradores de segmento, pode-se selecionar apenas um de 4 segmentos de 64

Kbytes de cada vez. Isto significa que de 1 MBytes, têm-se apenas 1 de 16 possíveis

segmentos endereçáveis diretamente (1 MBytes / 64 Kbytes = 16);

XX pode ser um registrador qualquer da CPU, como por exemplo: IP, quantidade de 16 bits, DI ou

SI, BX, BP, etc.

c) Posições de FFFF0-FFFFF (32 Bytes) reservadas para “Reset” => Após o “Reset”, a CPU

executa sempre a instrução contida no endereço FFFFF0, onde normalmente existe um JUMP.

d) Posições de 00000-003FF (1024 Bytes) reservadas para operações com Interrupção => 256

possíveis vetores de interrupção;

Endereçamento de Entrada/Saída

- 256 dispositivos diretamente;

- 64 Kbytes indiretamente

Tamanho dos Registradores Internos : 16 bits

Tamanho do Barramento de Dados: 16 bits

Coprocessador matemático: 8087

2.1.3 – Capacidade de Interrupção

1. Interrupções Predefinidas (requisitadas por hardware ou software)

De 0 a 31:

IRQ 0

IRQ 1

IRQ 2

...

è

è

è

Divisão por Zero

Passo-a-Passo

NMI (“Not Maskable Interrupt”)

2. Interrupções de Hardware (definidas pelo usuário)

De 32 a 255:

Solicitadas via pino INTR da CPU

Página 24

Microprocessadores

_________________________________________________________________________________________________

____

Observação: O dispositivo solicitante deve colocar em D0-D7 (8 bits menos significativos do

barramento de dados) o Número de Interrupção para a CPU. A CPU multiplica este número por 4 e

com o resultado, endereça a posição de memória contendo o vetor correspondente na TABELA DE

VETORES DE INTERRUPÇÃO. A figura 10 ilustra estes conceitos.

1a. Instrução

Rotina de Serviço

de Interrupção

IRET

Número de

Interrupção

003FF

x 4

IP

CS

Tabela de

Vetores de

Interrupção

00000

Figura 10 – Busca da Rotina de Serviço de Interrupção no 8086

Dos 4 bytes do VETOR DE INTERRUPÇÃO, os 2 primeiros formam o conteúdo do IP (“Instruction

Pointer”) e 2 bytes restantes formam o conteúdo do CS - Registrador de Segmento de Código (“Code

Segment”). Desta maneira é formado o Endereço de Início da Rotina de Serviço de Interrupção.

3. Interrupções de Software (definidas pelo usuário)

De 32 a 255: Solicitadas via instrução "INT nn"

nn = Número da Interrupção a ser executada

Para finalizar este item deve-se comentar a posição do microprocessador 8088 em relação ao 8086.

Sobre o 8088

Página 25

Microprocessadores

_________________________________________________________________________________________________

____

Uma das únicas diferenças entre os dois processadores é a de que o barramento de dados no 8088

possui um comprimento de 8 bits (o barramento do 8086 é de 16 bits). Este fato possibilitou aos

fabricantes de microcomputadores o aproveitamento quase total dos circuitos periféricos do 8080

(mais conhecidos e mais baratos), reduzindo sobremaneira o custo final da máquina. Como o 8086,

efetivamente, não era utilizado como um microprocessador de 16 bits, propagandeou-se em larga

escala que microcomputadores com CPU 8088 possuíam o mesmo desempenho e mais baixo custo

do que máquinas com CPU 8086. A verdade é que o momento era de transição para uma CPU mais

poderosa e os fabricantes de placas ainda não haviam tomado uma posição definitiva à respeito.

Assim, o 8088 é arquiteturalmente (rodava os mesmos programas) igual ao 8086, com a diferença

principal apenas no comprimento do barramento de dados.

Sobre o par 80186/80188

Após os microprocessadores 8086 e 8088, a INTEL lançou o processador 80186, com desempenho

cerca de 30% superior ao 8086. O 80186 era um 8086 com novos blocos de hardware internos. Tal

microprocessador encontrou sua utilização na área de controle de processos, gerenciamento de

terminais e automação industrial. Entretanto, não fez sucesso comercial na área de

microinformática, pois suas melhorias em relação a software eram muito poucas.

A exemplo do par 8086/8088, uma CPU 80188 também foi produzida pela INTEL, com as mesmas

características do 80186, à exceção do barramento de dados, dimensionado para 8 bits

2.2 – O 80286

2.2.1 – Arquitetura e Características

O microprocessador 80286 surgiu com duas grandes novidades para a área de microinformática. A

primeira foi que o barramento de endereços da pastilha cresceu para 24 bits (não mais os 20 bits do

8086 e 80186), o que implica em uma capacidade de endereçamento de 16 MBytes. A segunda foi a

introdução de dois modos de funcionamento da CPU: o MODO REAL (compatível com o 8086) e o

MODO PROTEGIDO (específico para o 286). Uma terceira inovação, o suporte a memória virtual (na

época, não totalmente explorada), permitia o endereçamento de até 1 Gigabytes. Os itens que se

seguem procuram fornecer mais detalhes sobre esta CPU.

Modo Real: Neste modo, o 80286 é compatível em software (a nível de código objeto) com o

8086/8088. O fato de emular o 8086/8088 significa dizer que a memória a ser utilizada pelo programa

não pode ultrapassar 1.0 MBytes, consequentemente, não utilizando toda a capacidade de

endereçamento disponível. Sendo a CPU mais evoluída em hardware e permitindo a utilização de

osciladores a cristal de freqüências mais altas, sem dúvida máquinas com esta CPU, mesmo

operando neste modo, possuíam maior desempenho que os famosos XTs.

Modo Protegido: Neste modo, o 80286, também pode rodar programas 8086/8088 e além disso,

rodar programas escritos especificamente com o código fonte 80286. Neste modo, o 80286

automaticamente mapea 1.0 Gigabytes de endereços virtuais por tarefa dentro de um espaço de

endereço real de 16.0 Megabytes. No modo protegido, o 80286 provê proteção de memória para

isolar o sistema operacional e assegurar a privacidade de cada tarefa sendo executada. Assim, o

80286, foi especialmente otimizado para suportar sistemas multitarefa e multiusuário.

Página 26

Microprocessadores

_________________________________________________________________________________________________

____

Registradores do 80286

Registrador

AX = AH + AL

BX = BH + BL

CX = CH + CL

DX = DH + DL

SP

BP

SI

DI

IP

Flags H + Flags L

CS

DS

SS

ES

Finalidade

Acumulador

Base (2º acumulador)

Contador (usado em instruções de múltiplas interações)

Dado (algumas instruções movem dados de uma porta de E/S e a posição de

memória endereçada por DX)

Apontador de Pilha

Apontador de Base

Índice Fonte

Índice Destino

Apontador de Instrução

Flags

Segmento de Código

Segmento de Dados

Segmento de Pilha

Segmento Extra

Observação: Exatamente os mesmos registradores do 8086

Capacidade de Endereçamento:

24 bits de endereço è 16.0 MBytes

Operações com: byte, word, double word, quad word, BCD, ASCII, apontador e ponto flutuante;

Relógio:

80286-4

80286-6

80286

80286x

==> 4.0 Mhz

==> 6.0 Mhz

==> 8.0 Mhz

==> 12.0 Mhz e 16 Mhz

Organização de Memória:

è 2 x 8.0 MBytes;

a) física

b) Endereçamento:

31

16 15

Seletor de Segmento

0

Offset

O seletor de segmento (16 bits) especifica um índice dentro de uma tabela em memória residente

cujo conteúdo é um endereço base de 24 bits. O endereço real de memória é obtido com a soma

deste endereço base (24 bits) mais o offset (16 bits), totalizando 24 bits de endereço.

c)

Posições de 00000-003FF (1024 bytes è 256 possíveis vetores de interrupção) reservadas,

como no 8086, para operações com interrupção, no modo real;

d) Posições de FFFF0-FFFFF reservadas para "reset", no modo real;

Página 27

Microprocessadores

_________________________________________________________________________________________________

____

Endereçamento de Entrada/Saída:

- 256 dispositivos diretamente;

- 64 Kbytes indiretamente

Tamanho dos Registradores Internos: 16 bits

Tamanho do Barramento de Dados: 16 bits

Coprocessador matemático: 80287

Capacidade de Processamento de Instruções: aprox. 1.5 MIPS

(80286 a 8 Mhz)

2.2.2 - Diferenças no Conjunto de Instruções

O conjunto de instruções do 80286 é dividido em sete categorias: transferência de dados,

aritméticas, deslocamento/lógicas, manipulação de strings, controle de transferência, de alto nível e

de controle de processador.

Entre as instruções adicionais podem ser citadas as seguintes:

PUSHA è salva o conteúdo da totalidade dos registradores;

POPA è restaura o conteúdo da totalidade dos registradores;

INS è entra string de caracteres;

OUTS è sai string de caracteres;

ENTER è chama procedure;

LEAVE è libera procedure;

e mais 15 instruções que somente podem ser executadas no modo protegido;

2.2.3 – Implicações no Desempenho de um Microcomputador

Sistemas de microcomputador baseados no 80286 foram os primeiros sistemas com capacidade

para rodar sistemas operacionais de rede multiusuário e/ou multitarefa, na época, por exemplo, o

Netware 2.x da Novell, o qual era escrito em C e Assembly 80286. Tais sistemas, paulatinamente,

passaram à função de computador pessoal (“desktop”) e não mais a de servidor.

2.3 - OS 80386

2.3.1 - Diferenças de Arquitetura e Características

O microprocessador 80386 é compatível em software com o 8086. A INTEL optou por manter esta

compatibilidade para aproveitar toda a enorme base de software escrita para os 8086 e 80286. Sendo

Página 28

Microprocessadores

_________________________________________________________________________________________________

____

assim, o 386 executa a maioria dos programas escritos para o 8086 e 80286, simplesmente por que

este emula estas CPUs, não fazendo uso de todas as suas capacidades.

Primeiro microprocessador de 32 bits da INTEL, o 80386 trouxe um novo modo de operação, em

adição aos dois modos do 80286 (Real e Protegido), o modo Virtual. O microprocessador abordado

nos próximos parágrafos é o 80386 mais potente da família, que na literatura é chamado de

80386DX, ou 80386 "Full" ou ainda, como a INTEL o denominou, simplesmente, 80386.

A figura 11 mostra os registradores do 80386.

Registradores Gerais de

Endereço e Dados

31

15

7 0

AH

AL

BH

BL

CH

CL

DH

DL

SI

DI

BP

SP

Registradores Seletores

de Segmento

15

EAX

EBX

ECX

EDX

ESI

EDI

EBP

ESP

0

CS

SS

DS

ES

FS

GS

Código

Pilha

Dados

Apontador de Instrução

e Registrador de Flags

IP

FLAGS

EIP

EFlags

Figura 11 – Registradores do 80386

No MODO REAL, o 80386 é compatível em software (a nível de código objeto) com o 8086/8088,

inclusive com a mesma limitação de memória (1.0 MBytes). Sendo a CPU mais evoluída em

hardware (p.e. registradores de 32 bits) e permitindo a utilização de osciladores a cristal de

freqüências ainda mais altas que os 80286, sem dúvida, máquinas com esta CPU possuem

desempenho bem maior que os 286. Assim, neste modo, o mecanismo de endereçamento, o

tamanho de memória e a manipulação de interrupções são todos idênticos ao modo real do 80286.

As instruções 80386 também podem ser utilizadas neste modo.

No MODO PROTEGIDO, o 80386, se comporta exatamente como no modo de mesmo nome do

80286, sendo que endereçará 4.0 Gigabytes de memória real (ao invés dos 16.0 MBytes do 80286)

e 64 Terabytes de memória virtual. Neste modo, o mecanismo de endereçamento também é diferente

daquele utilizado no 80286. Enquanto no 80286 o endereço base é de 24 bits (aos quais são

adicionados 16 bits de offset), no 80386 este endereço é de 32 bits (aos quais são adicionados 16

ou 32 bits de offset).

Quando operando no modo protegido, o 80386 pode fazer uso de uma técnica chamada de

SEGMENTAÇÃO. Esta técnica organiza a memória em módulos lógicos chamados segmentos. Este

modo de gerenciamento de memória provém a base para a proteção de segmentos de memória. Por

Página 29

Microprocessadores

_________________________________________________________________________________________________

____

exemplo, uma tabela do sistema operacional pode residir em um segmento e, como tal, deve ser

protegido da interferência de usuários não privilegiados, os quais poderiam "derrubar" o sistema.

Uma outra técnica útil de gerenciamento de memória para sistemas operacionais multitarefa em

memória virtual é a técnica chamada de PAGINAÇÃO. Independentemente da segmentação, a qual

modulariza programas e dados em segmentos de comprimento variável, a paginação divide

programas em páginas uniformes múltiplas. Dessa forma, somente um pequeno número de páginas

de cada tarefa precisa estar na memória em um dado instante. A paginação é útil para o

gerenciamento da memória física do sistema.

O 80386 possui 4 níveis de proteção otimizados para suportar as necessidades de sistemas

operacionais multitarefa, os quais devem proteger e isolar programas de usuários, uns dos outros, e

programas do próprio sistema operacional, dos usuários. Tais níveis de proteção se constituem, em

outras palavras, em um sistema de privilégio hierárquico de 4 níveis:

PL=0 (mais privilegiado) - Núcleo do sistema operacional;

PL=1 - Serviços do Sistema Operacional;

PL=2 - Extensões do Sistema Operacional e

PL=3 - Aplicações.

Quando operando no MODO VIRTUAL, o 80386 permite a execução simultânea de aplicações 8086,

sistemas operacionais 8086 e suas aplicações, aplicações 80286 e, ainda, aplicações 80386.

Assim, em um computador 386 multiusuário, uma pessoa pode estar rodando uma planilha DOS,

enquanto outra usa o DOS e uma terceira roda múltiplos utilitários e aplicativos UNIX.

A MEMÓRIA CACHE é um bloco de memória RAM (do tipo estática) que, tendo tempo de acesso

menor que a memória principal (do tipo dinâmica), pode ser lido muito mais rapidamente. Assim,

antes de se executar um programa que está na memória principal, a região contendo o programa é

transferida para a memória cache e só então o programa é executado. Isto reduz drasticamente o

tempo de acesso à RAM e aumenta a velocidade de execução dos programas. No 80386, o uso de

memória cache era opcional, isto é, apenas algumas máquinas (dependendo do fabricante) incluíam

uma pastilha controladora de memória cache, o 82385 (gerenciavam até 256 Kbytes), e sua inclusão

implicava em um aumento da placa mãe. Esta pastilha só era encontrada nas últimas versões

micros 386.

Características Principais:

Capacidade de Endereçamento:

32 bits de endereço è 4.0 Gigabytes

Operações com: bit, campos de bit, string de bits, byte, word, double word, quad word, BCD, ASCII,

apontador e ponto flutuante;

Relógio:

80386-12

80386-16

80386x

80386x

Am386-40

è

è

è

è

è

12.5 Mhz

16.0 Mhz

20.0 Mhz

33.0 Mhz

40.0 Mhz

Organização de Memória:

a) Física:

è 2 x 2.0 Gigabytes;

è 4 x 1.0 Gigawords;

è 8 x 0.5 Gigalongwords

b) Endereçamento:

Página 30

Microprocessadores

_________________________________________________________________________________________________

____

3 espaços de endereço ==> lógico, linear e físico

Endereçamento Lógico (ou Virtual): Consiste de um segmento seletor (14 bits) e de um

offset (soma de componentes de endereçamento: BASE, INDEX, DISPLACEMENT => 32 bits),

totalizando 46 bits de endereçamento, consequentemente, um espaço de 64 Terabytes;

Endereçamento Linear: A unidade de segmentação translaciona o endereço lógico para

um endereço linear de 32 bits, implicando em 4.0 Gigabytes;

Endereçamento Físico: Se a unidade de paginação não está habilitada, o endereço linear

de 32 bits corresponde a um endereço físico, também de 4.0 Gigabytes.

c)

Posições de 00000000-000003FF (1024 bytes è 256 possíveis vetores de interrupção)

reservadas, como no 8086 e 80286, para operações com interrupção, no modo real;

d) Posições de FFFFFFF0-FFFFFFFF reservadas para "reset", no modo real;

Endereçamento de Entrada/Saída:

- 256 dispositivos diretamente, como nos 8086 e 80286;

- 64 Kbytes indiretamente

Tamanho dos Registradores Internos: 32 bits

Tamanho do Barramento de Dados: 32 bits

Coprocessador matemático: 80387

Capacidade de Processamento de Instruções: aprox. 4.0 a 10.0 MIPS

(80386 32 bits em 16, 20 e 25 Mhz)

2.3.2 - Diferenças no Conjunto de Instruções

O conjunto de instruções do 80386 é dividido em nove categorias: transferência de dados,

aritméticas, deslocamento/lógicas, manipulação de strings, controle de transferência, suporte de

linguagem de alto nível, suporte de sistema operacional e de controle de processador. As diferenças

no conjunto de instruções estão intimamente ligadas às instruções de suporte de linguagem de alto

nível e de sistema operacional.

Uma das fraquezas do projeto 286 foi a sua incapacidade de emular o 8086, mantendo a proteção e

a memória virtual. Com o 286, só se poderia emular o 8086 se este estivesse no modo real, quando a

proteção está completamente desabilitada. O projeto do 386 corrigiu este problema e permitiu então

que várias tarefas 8086 sejam emuladas ao mesmo tempo no seu modo VIRTUAL.

A fim de fornecer compatibilidade em software com os 80286, o 80386 podia executar instruções de

16 bits no modo real e no modo protegido. Prevendo a expansão para o 386, a INTEL, especificou

para o 286 que os bits não usados por um descritor de segmento deveriam ser posicionados em "0".

O 386 interpreta isso como um identificador de segmento 286. Assim, o processador examina o

conteúdo de um bit D do descritor de segmento. Se é "0", então todos os comprimentos de operando

e endereços efetivos são assumidos como de 16 bits (código 286). Se é 1, então o comprimento

default é de 32 bits (código 386). Independentemente da precisão default, o 80386 pode executar

instruções de 16 ou 32 bits, através de um prefixo automaticamente adicionado pelos montadores

Assembly da INTEL.

Página 31

Microprocessadores

_________________________________________________________________________________________________

____

Fonte: "80386 High Performance Microprocessor with Integrated Memory Management", INTEL

Corporation - Advance Information, october 1985;

Além das diferenças anteriormente mencionadas, pode-se ainda citar algumas outras:

1.

O tempo de execução das instruções é diferente em vários casos. Na maior parte, o 386 é mais

rápido que o 286;

2.

Existem vários códigos indefinidos no 286 que, se executados, provocariam uma falha de código

(INT 6). No 386 a instrução será executada;

3.

O prefixo LOCK (impede que outros dispositivos acessem a memória do processador) para o

8086 é irrestrito, mas para o 386 é proibido em várias instruções. O problema era que o uso

indiscriminado do LOCK resultava em que dispositivos eram inibidos por períodos

inaceitavelmente longos. No ambiente não protegido do 8086, cabia às aplicações não deixar que

isto ocorresse. No ambiente protegido do 386, apenas algumas instruções podem ser precedidas

deste prefixo, àquelas que não interferem com a velocidade de execução de tarefas.

2.3.3 – Versões 80386, 80386SX e 80386SL

O 80386SX podia ser interfaceado a circuitos periféricos de 16 bits, mas roda os softwares de 32 bits

escritos para o 386, pois sua arquitetura interna é de 32 bits. O seu barramento de dados é de 16

bits (a metade dos 32 bits do 80386). Endereça até 16 MBytes de memória real (bem menos que os

4 Gigabytes do 80386). Era comercializado pela INTEL com relógio máximo de 20 Mhz (o 80386 era

encontrado com relógio de 33 Mhz). Sua capacidade de execução de instruções varia entre 3 e 4

MIPS (menos da metade dos 11,4 MIPS do 80386 a 33 Mhz). O coprocessador utilizado com o

386SX era o 80387SX.

O 80386SL era um microprocessador também derivado do 80386 e foi projetado especialmente para

uso em computadores portáteis ("Lap Tops"). Esta pastilha foi o resultado da integração de três

circuitos: a CPU 386SL, um controlador de barramento e um controlador de vídeo gráfico, diminuindo

assim, o tamanho e o peso do equipamento, além de proporcionar uma característica particular de

economia de energia. A memória real endereçável do 386SL era de 32 MBytes (16 MBytes a mais

que o 386SX), sua freqüência de operação era de 20 Mhz e o barramento de dados de 16 bits (como

no 386SX). A unidade gerenciadora de energia era capaz de baixar a zero a atividade na CPU,

enquanto se lê a tela do micro ou no intervalo da digitação. A aplicabilidade do 386SL em "lap Tops"

foi indiscutível.

2.3.4 - Implicações no Desempenho de um Microcomputador

Com base nas explicações fornecidas nos itens anteriores pode-se dizer o seguinte:

A exemplo do que ocorreu com o 80286 em relação ao 8086, sistemas de microcomputador

baseados no 80386, paulatinamente, passaram de servidores a desktops. Uma versão do Netware da

Novell, a versão 3.12, até os dias atuais muito utilizada, usa toda a capacidade deste

microprocessador, uma vez que foi escrita em C e assembly 386.

Página 32

Microprocessadores

_________________________________________________________________________________________________

____

O 80386 dispunha de um modo de execução muito melhor adaptado ao funcionamento multitarefa do

que o 80286. Na época, sistemas baseados neste microprocessador eram os únicos capazes de

suportar de uma só vez os sistemas operacionais DOS, OS/2 e UNIX.

2.4 - OS I486

A INTEL, segundo decisão da justiça dos EUA, não pode registrar números, 386 e 486 p.e., como

suas marcas. Optou então, por acrescentar um "i" (i minúsculo) na frente dos números. Assim, 486,

80486 ou i486 eram nomes encontrados na literatura para designar o mesmo processador.

Inicialmente será abordado o i486 e em seguida o i486SX.

2.4.1 - Diferenças de Arquitetura e Características

A arquitetura interna do i486 foi otimizada em relação ao 80386 ou i386. Isto possibilitou a introdução

na pastilha de algo acima de um milhão de transistores (quatro vezes mais que o i386 possui). Os

fabricantes de computadores foram diretamente beneficiados por esta densidade de integração, uma

vez que a placa mãe sofreu uma redução significativa de tamanho e o processo de projeto e

montagem foi simplificado. Também o microcódigo de instruções foi otimizado, de forma a manter o

máximo possível as operações no interior da pastilha e, consequentemente, eram necessários

menos ciclos de relógio para executar as mesmas instruções que o i386 já executava. O 486 usa

ambas as bordas do sinal de Relógio para a CPU, enquanto os 286 e 386 usavam apenas uma

borda.

Pode-se dizer que, a grosso modo, o ganho de desempenho veio, essencialmente, da memória

cache e do coprocessador (essencial em ambientes de CAD/CAM). Entretanto, em ambientes de

microinformática, considerados mais simples, que usam planilhas e bancos de dados, o ganho de

desempenho com o uso do coprocessador foi praticamente nulo.

O i486 incorpora o i386 com as suas instruções, memória cache de 8 Kbytes de RAM estática (mais

rápida que a dinâmica) e gerenciador próprio (80385) e coprocessador aritmético (80387). Foram

adicionadas ao conjunto de instruções do i386 cinco instruções: três para gerenciamento da

memória cache e duas, incluídas a pedido da Microsoft, para tratamento de tarefas concorrentes

pelo OS/2. Como no i386, a pastilha endereça diretamente até 4.0 Gigabytes e indiretamente até 64

Terabytes.

2.4.2 - Diferenças na Capacidade de Processamento

O i486 a 25 Mhz possui uma capacidade de processamento de instruções de aproximadamente 20.0

MIPs (duas vezes mais rápido que um i386 nos mesmos 25 Mhz) e é totalmente compatível com

este último.

Como mencionado, a capacidade de processamento do 486 foi amplamente influenciada pela

memória cache. Isto é detalhado a seguir.

Há muitas discussões sobre o melhor tamanho da memória cache, mesmo entre os fabricantes de

microcomputadores, por isso mesmo são oferecidas ao usuário as mais diferentes opções. Uma vez

que esta é a responsável direta pelo aumento de desempenho da máquina, uma escolha acertada

Página 33

Microprocessadores

_________________________________________________________________________________________________

____

poderia beneficiar grandemente o usuário. O que se constata na literatura especializada é que o

melhor tamanho para a memória cache é o tamanho do maior programa que vai ser executado

naquela máquina. Entretanto pode-se tornar excessivamente caro colocar o máximo possível de

memória cache, não compensando os benefícios correspondentes.

O i486 permitiu memória cache externa, além dos 8 Kbytes internos. Assim, algumas máquinas

eram oferecidas com 256 Kbytes externos. Considerando-se o desempenho relativo a um XT 4.77

Mhz, pode-se fornecer alguns dados de desempenho, como discriminados abaixo:

i486, 33 Mhz, cache externo de 64 Kbytes

Cache interno e externo desabilitado

è 6,5 vezes mais rápido;

è 26 vezes mais rápido;

Somente cache externo habilitado

Somente cache interno habilitado

è 38 vezes mais rápido;

Caches interno e externo habilitados

è 72 vezes mais rápido;

Conclui-se destes dados que o cache interno é extremamente importante, mesmo sendo muito

menor que o externo. Isto se deve a sua lógica de construção e, obviamente, ao fato de estar dentro

da própria pastilha de CPU.

Quando se carrega um programa na memória cache e este é executado, considera-se que isto é um

"acerto" e cada vez que se deve movimentar um bloco da memória principal para a RAM de cache,

considera-se que isto é um "erro". Existe, portanto, uma taxa de acertos ("Hit Rate") relacionada

com o tamanho da memória cache. Um cache externo maior, evidentemente, possibilitará uma

melhor taxa de acertos, uma vez que poderá conter mais programas. Assim, a velocidade do cache

interno aliada a uma melhor taxa de acertos provida pelo cache externo, possibilitará um melhor

desempenho da máquina como um todo.

Sobre o i486SX

O i486Sx foi lançado pela INTEL para fazer frente a concorrência acirrada do microprocessador

Am386-40 de 40 Mhz da Advanced Micro Devices (AMD), mais veloz que o seu microprocessador

mais rápido, o i386 33 Mhz. Deve-se entender o "SX" com uma versão desprovida de algo que sua

versão completa, ou "full", ou ainda "DX", continha.

O i486SX possui um barramento de dados de 32 bits, exatamente como o i486. Isto não aconteceu

com o i386SX, o qual possui 16 bits para dados, 16 a menos que i386. Basicamente, o i486SX opera

a uma taxa de relógio de 20 Mhz e possui uma unidade de ponto flutuante interna (como o i486),

mas esta encontra-se desativada. Estes dois fatores levaram a uma diminuição no custo da pastilha

de 60% em relação ao i486. O i486SX, mesmo a 20 Mhz segundo a INTEL, era 45% mais rápido que

o i386 (33 Mhz), com um custo apenas 17 % superior. Já o i486 25 Mhz era 20% mais rápido que o

i486SX (20 Mhz) e custava 270% mais caro (custo em março de 1992). Um quadro exibido pela

revista Micro Sistemas em março de 1992 mostrava o seguinte:

CPU (clock)

i386 (33)

i486SX(20)

Custo (US$)

MIPs

Custo do MIP (US$)

214

250

11,4

16,5

18,77

15,15

Página 34

Microprocessadores

_________________________________________________________________________________________________

____

i486 (25)

671

20,0

33,55

Sobre o i486 50 Mhz (i486/50 e i486DX2/50)

Em junho de 1991 a INTEL lançou o i486 50 Mhz e somente em junho de 1992 a revista PC

Magazine americana publicou testes de desempenho sobre as primeiras máquinas fabricadas com

esta CPU. Antes desta CPU, a líder em desempenho da INTEL era o i486 33 Mhz. Segundo a citada

revista, o i486/50 é 30% mais rápido que i486/33 a um custo (naquele ano) 10 a 20% maior. Uma

observação importante é que máquinas equipadas com esta CPU definitivamente não eram baratas,

mas a relação custo beneficio em relação ao i486/33 era atraente. Isto significou, em outras palavras,

que se alguém estivesse disposto a pagar o preço de uma máquina 486/33, era melhor que o fizesse

por uma i486/50, em função da melhor relação custo/benefício.

Em março de 1992 a INTEL anunciou as chamadas pastilhas "Speed-Doubler". Tais pastilhas

introduziram opções de preço e desempenho nos i486. Uma dessas opções, é o i486DX2/50 que

opera internamente a 50 Mhz, mas comunica-se com os barramentos a 25 Mhz. Isto permite o

projeto de sistemas baseados, externamente, no i486 25 Mhz, facilitando mais uma vez o dia-a-dia

dos fabricantes de micro e minicomputadores. A segunda opção é a pastilha "full" i486DX/50. Esta

pastilha é 30% mais rápida que a anterior.

Em linhas gerais, pode-se dizer que para máquinas necessitando de uma atividade de Entrada/Saída

intensa, como servidores de arquivos p.e., o i486DX2/50 não seria a primeira escolha. Já para

máquinas "stand-alone" em ambientes de CAD/CAM esta seria uma boa escolha.

O i486DX/50 contém basicamente a mesma lógica de processador que o i486DX/33, com

coprocessador, 8 Kbytes de cache e 1,2 milhão de transistores, mas houve alguns refinamentos

técnicos na parte de 50 Mhz, a qual usa um projeto de pastilha de três camadas e não de duas

camadas como o i486DX/33.

Sobre os i486DX2/66 e i486DX4/100

Em novembro de 1992, foram disponibilizadas comercialmente máquinas sob controle da pastilha

i486DX2/66, ou seja, operando internamente a 66 Mhz e externamente a 33 Mhz. Testes preliminares

revelaram que esta pastilha é 30% mais rápida que o i486DX/50.

O i486DX4/100, possui um clock interno de 99 MHz, operando externamente a 33 MHz. Esta

pastilha entrou e saiu rapidamente do mercado, dando lugar aos microprocessadores da classe

Pentium.

Algumas Observações:

Os problemas relacionados a estes microprocessadores são a quantidade de calor desprendida, que

precisa ser dissipada, e a emissão de sinais de alta frequência, podendo também sofrer

interferências do meio ambiente, como é o caso das televisões que emitem sinais na faixa de 54 a

890 Mhz. A partir dos i486, os fabricantes iniciaram a utilização de ventiladores acoplados aos

dissipadores, para reduzir os efeitos da alta temperatura. Também alguns gabinetes são

comercializados com algum tipo de blindagem interna de modo a minimizar a influência das

frequências externas.

Com a crescente demanda do mercado por redes de computadores e, consequentemente, por

equipamentos de gerenciamento e interconexão de tais redes, observou-se que as CPUs de pontes

Página 35

Microprocessadores

_________________________________________________________________________________________________

____

(“Bridges”), roteadores (Routers”), ponte-roteadores (“Brouters”) e passarelas

(“Gateways”)

frequentemente, são CPUs INTEL do tipo 286 e 386. Neste mercado, modelos mais sofisticados

desses equipamentos frequentemente fazem uso de CPUs MOTOROLA e alguns até mesmo de

processadores RISC.

2.5 - OS PENTIUM, PENTIUM MMX E PRO

2.5.1 - Diferenças de Arquitetura e Características

Antes de iniciar as explicações sobre os Pentium MMX e PRO, é necessário mencionar os primeiros

microprocessadores da classe Pentium, os simplesmente Pentium (núcleo P54C).

Os Pentium

Essencialmente, o Pentium consiste de dois processadores i486 em paralelo. Logo, mais instruções

são processadas ao mesmo tempo, tipicamente, o dobro. Pode-se destacar algumas características

importantes.

Pipelines

O microprocessador Pentium é construído em torno de 2 pipelines (ou Pipes) inteiros (U e V),

paralelos, de propósito geral e 1 unidade com pipeline, de ponto flutuante. O pipe U é chamado

de Principal e o pipe V é chamado de Secundário. O Pipe U possue algumas limitações sobre

instruções que executa. Os dois Pipes tem cinco estágios cada um, como mostrado na figura 12.

O Pentium pode buscar até 2 instruções por ciclo. Durante a execução de uma instrução, as

próximas duas instruções são testadas. Se possível, a primeira é executada no Pipe U e a Segunda

no Pipe V. Se não é possível, uma instrução é passada ao Pipe U e nenhuma instrução é passada

ao Pipe V. O comportamento funcional das instruções nos dois Pipes é exatamente o mesmo de

instruções executadas sequencialmente.

Caches

O Pentium possui um subsistema de cache interno com 2 conjuntos (um para instrução e outro para

dados) de caches associativos de 8 Kbytes. Como o cache de dados é disposto em 8 bancos, este

pode ser acessado simultaneamente por ambos os Pipes, desde que as referências sejam para

bancos diferentes.

Prebuscador de Instruções (“Instruction Prefetcher”)

O, aqui chamado, Prebuscador de Instruções possui 4 buffers de 32 Bytes. No estágio PF, dois

buffers de prebusca operam em conjunto com o buffer chamado BTB (“Branch Target Buffer “).

Somente 1 dos buffers de prebusca requisita prebuscas em um dado tempo. Se uma instrução de

salto é buscada, o BTB prevê se o salto ocorrerá ou não. Se o salto não vai ser executado tudo

continua linearmente. Se é para ser executado, o outro buffer de prebusca é habilitado e inicia a

prebusca como se o salto fosse executado. Se finalmente o salto não for realizado, os pipelines de

instrução são limpos e a atividade de prebusca recomeça. Como o cache de instruções e dados são

separados, prebuscas de instruções não conflitam com referências a dados para acesso ao cache.

Página 36

Microprocessadores

_________________________________________________________________________________________________

____

O Pentium emprega um esquema de previsão dinâmica de saltos (“Dynamic Branch Prediction”).

Se a previsão é correta, não há penalidade na execução de uma instrução de salto. Se não é correta,

as penalidades são as seguintes:

1.

2.

3.

3 ciclos, se o JUMP condicional foi no Pipe U;

4 ciclos, se o JUMP condicional foi no Pipe V e

3 ciclos em qualquer dos Pipes para CALLs e instruções de JUMP incondicional.

Prefetch

(PF)

Estágio de

Decodificação 1

(DS1)

Pipe U

Pipe V

Estágio de

Decodificação 2

(DS2)

Estágio de

Decodificação 2

(DS2)

Execução

Execução

Writeback

Writeback

Figura 12 – Pipelines de Inteiros do Pentium

Write Buffers

O Pentium possui 2 buffers de escrita, um para cada Pipe (U ou V). A finalidade desses buffers é

aumentar o desempenho de escritas consecutivas na memória. Esses buffers de 64 bits são

carregados simultaneamente em um período de relógio. Escritas nesses buffers são enviadas para o

barramento externo do processador. Tais operações de escrita acontecem sempre na ordem em que

ocorrem. Não são possíveis leituras intermediárias.

Página 37

Microprocessadores

_________________________________________________________________________________________________

____

Unidade de Ponto Flutuante

A Unidade de Ponto Flutuante do Pentium acrescenta um Pipeline de 3 estágios aos Pipes já

mencionados (U e V). As instruções de ponto flutuante seguem normalmente pelo pipeline até o

estágio E (Execução). Após este estágio, as instruções dispendem pelo menos um clock para cada

um dos 3 estágios: X1, X2 e WF. A maioria das instruções de ponto flutuante tem um período de

latência superior a um período de relógio. Entretanto, tal latência é escondida pela existência dos 3

estágios. Além disso, instruções com inteiros (e não de ponto flutuante) são tratadas durante este

período de latência. A figura 13 exibe a integração dos Pipelines de Inteiros e Ponto Flutuante. Os 3

primeiros estágios do Pipe de Inteiros são desacoplados do Pipe de Ponto Flutuante. Os dois

últimos são integrados.

X1

Prefetch

(PF)

Estágio de

Decodificação 1

(DS1)

Estágio de

Decodificação 2

(DS2)

X2

WF

Execução Writeback

Estágios do Pipe de Ponto Flutuante desacoplados

Estágios Integrados dos Pipes

Pipeline de Inteiros somente

Figura 13 – Integração dos Pipelines de Inteiros e de Ponto Flutuante do Pentium

Os Pentium MMX

Os microprocessadores Pentium com tecnologia chamada pela INTEL de MMX (algo como

“Multimedia Extensions”) trouxeram quatro enriquecimentos básicos de projeto arquitetônico:

1.

2.

3.

4.

Arquitetura SIMD;

4 novos tipos de dados.

8 registradores MMX de 64 bits e

57 novas instruções;

Como a própria INTEL propagandeia, esta mudança na arquitetura do processador foi a mais

importante desde o 80386, o qual extendeu a arquitetura de 16 para 32 bits e introduziu três modos

de funcionamento (real, protegido e virtual). Como de fato se verificou, tais mudanças foram

incorporadas a todas as gerações de processadores subsequentes da empresa.

Segundo a INTEL, a definição desta tecnologia foi resultado de trabalho conjunto entre arquitetos de

microprocessadores e desenvolvedores de software. Dentre os softwares analisados, incluiram-se

Gráficos, Vídeo MPEG, Síntese de música, compressão de voz, reconhecimento de voz,

Página 38

Microprocessadores

_________________________________________________________________________________________________

____

processamento de imagens, jogos e vídeo-conferência. O núcleo deste processador foi chamado de

P55C.

Esta análise mostrou muitas características comuns entre as diversas categorias de software. Os

atributos chave para estas aplicações foram:

•

•

•

•

•

Tipos de dados pequenos e inteiros (por exemplo: pixel gráfico de 8 bits, amostras de

áudio de 16 bits);

Loops pequenos altamente repetitivos;

Multiplicações e acumulações frequentes;

Algoritmos de computação intensiva;

Operações altamente paralelas.

Assim, foi projetado um grupo de instruções novo, com instruções inteiras de propósito geral, visando

a otimização do processamento de tais aplicações.

Arquitetura SIMD (“Single Instruction Multiple Data”)

Técnicas SIMD foram utilizadas de forma a permitir que múltiplas peças de informação pudessem ser

processadas com uma única instrução, provendo um certo paralelismo, reduzindo loops de

computação intensiva e, consequentemente, aumentando o desempenho de aplicações multimídia e

de comunicações.

Novos Tipos de Dados

O tipo de dado principal da arquitetura MMX é um pacote inteiro de ponto fixo, onde múltiplas

palavras inteiras são agrupadas em uma única quantidade de 64 bits. Estes pacotes são

manipulados por registradores MMX de 64 bits.

Como exemplo de benefício pode-se citar o pixel, geralmente representado em inteiros de 8 bits, ou

bytes. 8 desses pixels podem ser “empacotados” em uma única quantidade de 64 bits e movidos

para um registrador MMX. Uma instrução MMX ao ser executada, busca 8 pixels de uma só vez, faz

as operações lógicas e aritméticas sobre os oito elementos e escreve o resultado em um outro

registrador MMX.

A figura 14 exibe os novos tipos de dados do Pentium MMX.

Página 39

Microprocessadores

_________________________________________________________________________________________________

____

Packet Byte (8 elementos de 8 bits)

63

31

7

0

Packet Word (4 elementos de 16 bits)

63

31

0

Packet Doubleword (2 elementos de 32 bits)

63

31

0

Quadword (1 elemento de 64 bits)

63

0

Figura 14 – Novos Tipos de Dados do Pentium MMX

Registradores MMX

A figura 15 exibe o layout dos oito novos registradores MMX

Campo

TAG

63

0

MM7

MM0

Página 40

Microprocessadores