AULA 5 – Complemento

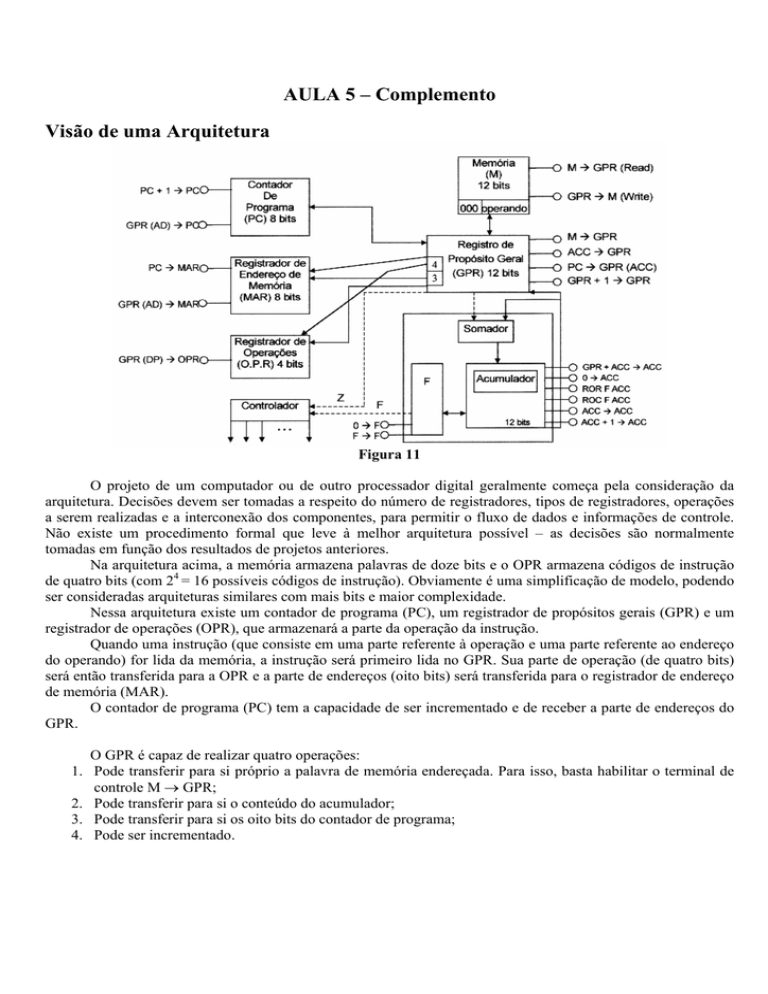

Visão de uma Arquitetura

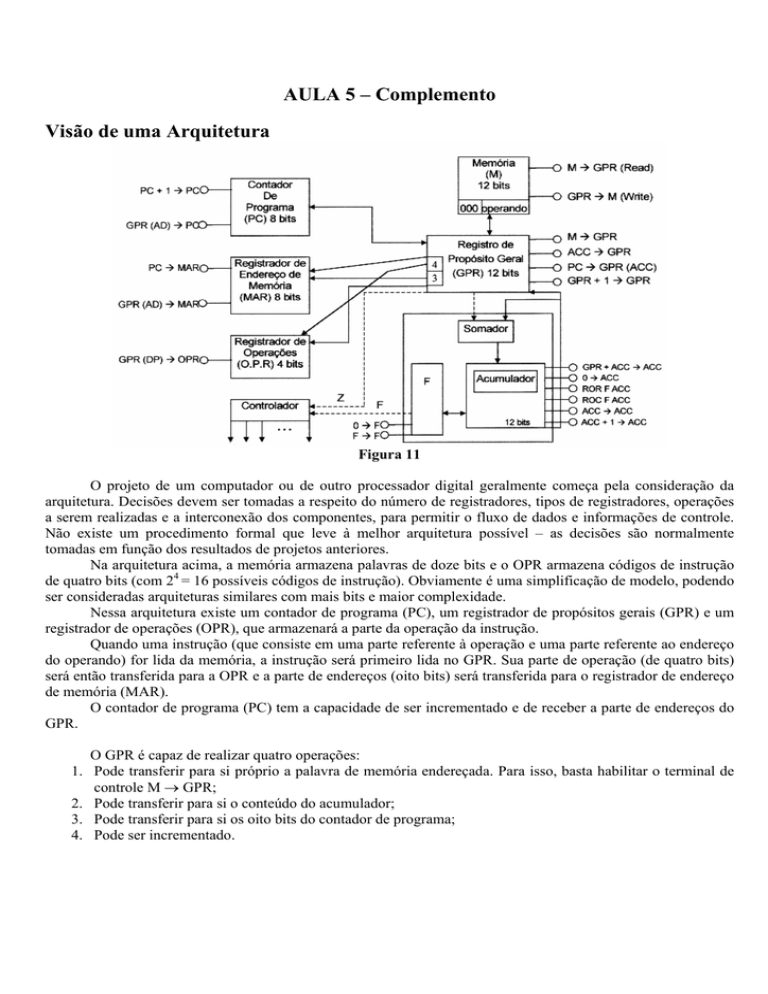

Figura 11

O projeto de um computador ou de outro processador digital geralmente começa pela consideração da

arquitetura. Decisões devem ser tomadas a respeito do número de registradores, tipos de registradores, operações

a serem realizadas e a interconexão dos componentes, para permitir o fluxo de dados e informações de controle.

Não existe um procedimento formal que leve à melhor arquitetura possível – as decisões são normalmente

tomadas em função dos resultados de projetos anteriores.

Na arquitetura acima, a memória armazena palavras de doze bits e o OPR armazena códigos de instrução

de quatro bits (com 24 = 16 possíveis códigos de instrução). Obviamente é uma simplificação de modelo, podendo

ser consideradas arquiteturas similares com mais bits e maior complexidade.

Nessa arquitetura existe um contador de programa (PC), um registrador de propósitos gerais (GPR) e um

registrador de operações (OPR), que armazenará a parte da operação da instrução.

Quando uma instrução (que consiste em uma parte referente à operação e uma parte referente ao endereço

do operando) for lida da memória, a instrução será primeiro lida no GPR. Sua parte de operação (de quatro bits)

será então transferida para a OPR e a parte de endereços (oito bits) será transferida para o registrador de endereço

de memória (MAR).

O contador de programa (PC) tem a capacidade de ser incrementado e de receber a parte de endereços do

GPR.

1.

2.

3.

4.

O GPR é capaz de realizar quatro operações:

Pode transferir para si próprio a palavra de memória endereçada. Para isso, basta habilitar o terminal de

controle M → GPR;

Pode transferir para si o conteúdo do acumulador;

Pode transferir para si os oito bits do contador de programa;

Pode ser incrementado.

Para realizar cada microoperação, o controlador deve formar sinais de comando dos terminais de controle

de diversos registradores e da memória em ciclos de relógio apropriados.

Lista de micro-operações

Memória : GPR → M

escreve o conteúdo de GPR na localização de memória

PC: PC + 1 → PC

incrementa o PC

GPR (AD) → PC transfere a parte do endereço do GPR para o PC

MAR

: GPR (AD) → MAR transfere a parte de endereços do GPR para o MAR

OPR

: GPR (OP) → OPR transfere a parte de operação do GPR para o MAR

GPR

: M → GPR

transfere a palavra endereço para o GPR

Acc → GPR

transfere o conteúdo do acumulador para o GPR

PC → GPR (AD) transfere o conteúdo do PC para a parte de endereços

do GPR

GPR + 1 → GPR incrementa GPR

GPR+Acc→ Acc adiciona conteúdo do GPR com o do Acc e deixa

resultado no Acc

GPR + Acc → Acc adiciona conteúdo do GPR com o de Acc e deixa

resultado no Acc

ULA:

Ø → Acc

ACC → Acc

Acc + 1 → Acc

Ø→F

F→F

zera o acumulador

complementa o acumulador

incrementa o acumulador

zera o flip-flop F

complementa F

ROR F Acc

gira o acumulador à direita através de F.

ROL F Acc

Figura 12

gira o acumulador à esquerda através de F.

Figura 13

Instruções:

Após iniciar a operação, o controlador funcionará buscando uma instrução, acrescentando-a, buscando

outra instrução, executando-a e assim por diante.

A seqüência de microinstruções necessárias para realizar a busca (“fetch”) da instrução é a seguinte:

1.

PC

→ MAR

transfere endereço de instrução para o MAR

2.

M

→ GPR

transfere a palavra endereçada (instrução) para o GPR

PC + 1 → PC

e incrementa o PC

3.

GPR (OP) → OPR transfere a parte da operação para o OPR

As instruções da máquina podem ser implementadas diretamente a partir das microinstruções, ou através

de combinações ou seqüências delas.

Instruções elementares: (implementadas diretamente das microinstruções)

Ø

Acc

Acc + 1

Ø

F

ROR

ROL

PC + 1

→

→

→

→

→

F

F

→

Acc

Acc

Acc

F

F

Acc

Acc

PC

zerar o acumulador

complementar o acumulador

incrementar o acumulador

zerar F

complementar F

girar à direita por F

girar à esquerda por F

saltar para a próxima instrução

se F = Ø

terminar

CRA

CTA

ITA

CRF

CTF

ROR

ROL

SFZ

HLT

Outras instruções:

1) ADD <endereço>

Adiciona ao conteúdo do acumulador o operando localizado no endereço específico.

1. GDR (AD) → MAR

2. M → GDR

3. GDR + Acc → Acc

2) ADD I <endereço>

Adiciona ao conteúdo do acumulador o operando apontado pelo endereço especificado

1. GDR (AD) → MAR

2. M → GRR

3. GPR (AD) → MAR

4. M → GPR

5. GPR + Acc → Acc

3) STA <endereço>

Armazena o conteúdo do acumulador no endereço de memória especificado.

1. GPR (AD) → MAR

2. Acc → GPR

3. GPR → M

4) JMP <endereço>

salta para a instrução presente no endereço especificado

1. GPR (AD) → PC

5) JMPI <endereço>

salta para a instrução apontada pelo endereço especificado

1. GPR (AD) → MAR

2. M → GPR

3. GPR (AD) → PC

6) CSR <endereço>

chama a subrotina armazenada a partir do endereço especificado

1. GPR (AD) → MAR

2. GPR (AD) →→ PC

3. PC → M

4.GPR (AD) → PC

5. PC + 1 → PC

7) ISZ <endereço>

incrementa o valor armazenado no endereço especificado e salta para a próxima instrução, se zero.

1.

2.

3.

4.

5.

Outras instruções

CRA

CTA

ITA

CRF

CTF

ROR

ROL

HTL

GRR (AD)

M

GPR + 1

GPR

PC +1

→

→

→

→

→

MAR

GRR

GPR

M

PC (se GPR = 0)

Figura 14

Exemplos de Programação na Arquitetura

Figura 15

Microprogramação

Microprogramação é uma técnica de realizar controle em computadores, e baseia-se na utilização de

microinstruções. Um computador controlado por microprograma pode ser visto como um computador dentro de

outro computador.

As microinstruções (ou micro-operações) são executadas em resposta à sinais aplicados à terminais de

controle dos registradores, ULA e memória. Esses sinais são chamados de sinais de comando. Em qualquer

intervalo de relógio uma ou mais entradas de controle devem ser habilitadas para a execução dos procedimentos

computacionais. Através disso é possível executar seqüências de microinstruções (tais como: (1) GPR

(AD)→MAR, (2) M→GPR, (3) GPR + Acc→Acc), executando, ao final de cada seqüência, uma instrução da

linguagem de máquina (como ADD).

Exemplo de Controlador de Interrupção:

Figura 16

Após iniciar sua operação, um controlador típico repete seqüências de busca-execução de instruções até

encontrar uma instrução de parada (ex.: “Halt”).

No entanto, eventualmente é necessário interromper essa seqüência para fazer com que o controlador

execute uma ou outra seqüência especial de instruções. Isso pode ocorrer porque uma fonte solicita uma

interrupção. Em resposta, o controlador deve atender à interrupção. Obviamente, se existem vários níveis de

interrupção em um sistema computacional, o controlador só irá interromper seu procedimento para atender a

solicitação de maior prioridade.

Formatos de Instrução

Uma instrução em linguagem de máquina possui dois componentes fundamentais: o código da operação e

campos de endereços opcionais. As instruções em linguagem de máquina podem ainda conter modificadores,

específicos de cada arquitetura e fabricante.

O código da operação é tipicamente um valor binário sem sinal que indica a operação que deve ser

executada. O conjunto das operações que podem ser manipuladas diretamente pelo processador é chamado de

conjunto de instruções ou linguagem de máquina. Se as instruções alocam i bits para o código, é possível haver

até 2i instruções para aquela arquitetura em particular.

Os campos de endereço, também chamados operandos, são os endereços da informação sobre o qual o

processador irá executar a operação específica. Os conjuntos de instrução são caracterizados pelo número de

operandos permitidos em cada operação.

Figura 17

Formato de 4 endereços:

O formato de instruções com quatro endereços permite até quatro endereços em cada instrução. O uso

desses endereços é definido pelo fabricante para cada instrução, como por exemplo, especificado:

1. o operador esquerdo de uma operação binária;

2. o operador direito de uma operação binária;

3. o resultado

4. o endereço da próxima instrução.

Ex.: A: = B + C – D

endereço op. code

op. esq.

op. direito

Res.

100

101

B

T

C

D

T

A

ADD

SUB

Prox.

inst.

101

102

O comando acima poderia ser realizado em apenas dois passos.

Apesar de seu poder de representação, o formato de quatro endereços não é utilizado por tornar as

instruções muito grandes. Para suportar 2i instruções diferentes e 2n endereços de memória, o tamanho total de

cada instrução seria de i + 4n.

Formato de 3 endereços

Para reduzir o tamanho das instruções com endereços pode-se eliminar, por exemplo, o endereço da

próxima instrução.

Os endereços descreveriam:

- o operando esquerdo de uma operação binária;

- o operando direito de uma operação binária;

- o resultado

Como o endereço da próxima instrução não é especificado, é necessário convencionar sua localização. A

convenção utilizada para todos os computadores convencionais é executar a instrução presente no endereço

seguinte a menos que seja especificada uma outra instrução.

Essa convenção faz com que os programas sejam armazenados em bloco seqüenciais de memória. Além

disso, já que o endereço da próxima instrução a ser executada não é mais explícito, é necessário incluir um

registrador especial para armazenar essa informação: o contador de programa (PC). É necessário ainda haver

instruções que não restrinjam a execução dos programas sempre as instruções seguintes, implementando as

chamadas “branching instructions”.

Apesar de menores, esse formato de instrução ainda apresenta instruções grandes, de vários bytes, que

devem ser armazenados e buscados na memória.

Formato de dois endereços:

Exemplo de registrador de instruções (IR):

Figura 18

Para reduzir o tamanho das instruções, é possível eliminar mais endereços, como o do resultado. Assim, é

necessário convencionar seu armazenamento em algum local fixo e conhecido, como por exemplo, no mesmo

endereço do primeiro ou segundo operando. Assim, uma instrução do tipo “ADD x,y” pode representar “x:=

x+y”. como é fácil notar, no uso desse formato, é necessário estar atento a esta convenção para não perder

informações.

Formato de um endereço:

Figura 19

Neste formato, só existe um endereço por instrução. É necessário convencionar quais são os endereços de

um possível segundo operando e do resultado, como por exemplo em um registrador de propósitos gerais (ex.:

Acc).

Assim, uma instrução do tipo “ADD x” significa “Acc : = Acc + x”

A vantagem desse formato de instruções é seu tamanho. Com 2i instruções diferentes e espaço endereçável

n

2 , cada instrução ocuparia somente ( i + n) bits.

Exercícios

1. Implemente o comando A: = B + C – D usando instruções hipotéticas (ex.: ADD e SUB) e formatos de 3,

2 e 1 endereços.

2. É possível implementar um computador com formato de Ø endereços? Se sim: como isso poderia ser

implementado?

3. Se um computador utiliza formato de instruções com 2 endereços, tiver 16 Mb de espaço endereçável e

100 instruções diferentes, qual deveria ser o tamanho do seu registrador de instruções?

4. É verdadeira ou falsa a afirmação abaixo? Por quê? Ao final da fase de “fetch”, o PC conterá o endereço

da próxima instrução a ser executada.

5. Reescreva a instrução abaixo em notação prefixa: A : = (( B + C * (C/(D*E))) – 1

6. Uma variação da estrutura de Von Neumann consiste na execução simultânea de uma única instrução em

ULAs distintas. Descreva possíveis explicações para uma arquitetura desse tipo.