TUTORIAL PARA SÍNTESE STANDARD-CELLS

Atualizado em 04/novembro/2007

Fernando Gehm Moraes

ATENÇÃO: PASSOS 1 a 4 NO WINDOWS

Verifique se a variável de ambiente MGLS_LICENSE_FILE é igual a

[email protected] (my_computer properties advanced environment

variables). Se não for este valor, insira esta variável.

1 – Arquivos do multiplicador e de simulação (test bench)

Baixar do endereço abaixo os códigos VHDL contendo o multiplicador e o respectivo test_bench.

http://www.inf.pucrs.br/~moraes/microel/multiplicador/multiplica.vhd

e

http://www.inf.pucrs.br/~moraes/microel/multiplicador/tb.vhd

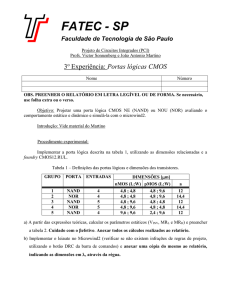

2 – Simulação funcional no modelsim:

Abrir o simulador ModelSim (

seguintes comandos:

). Na janela transcript (onde tem o prompt) digitar os

cd E:/multiplicador

vlib work

vmap work work

vcom multiplica.vhd tb.vhd

vsim work.testa_mult

view wave

# ir para o diretório onde estão os fontes

# nomes dos fontes VHDL

# não mudar, pois é o nome da entity do test_bench

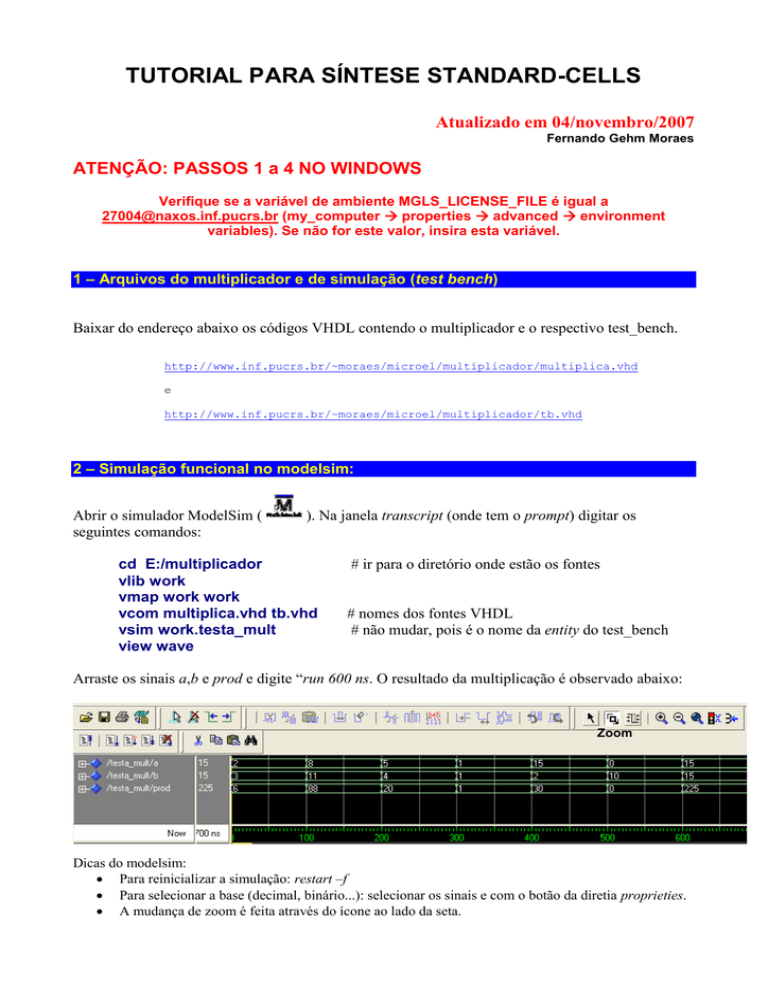

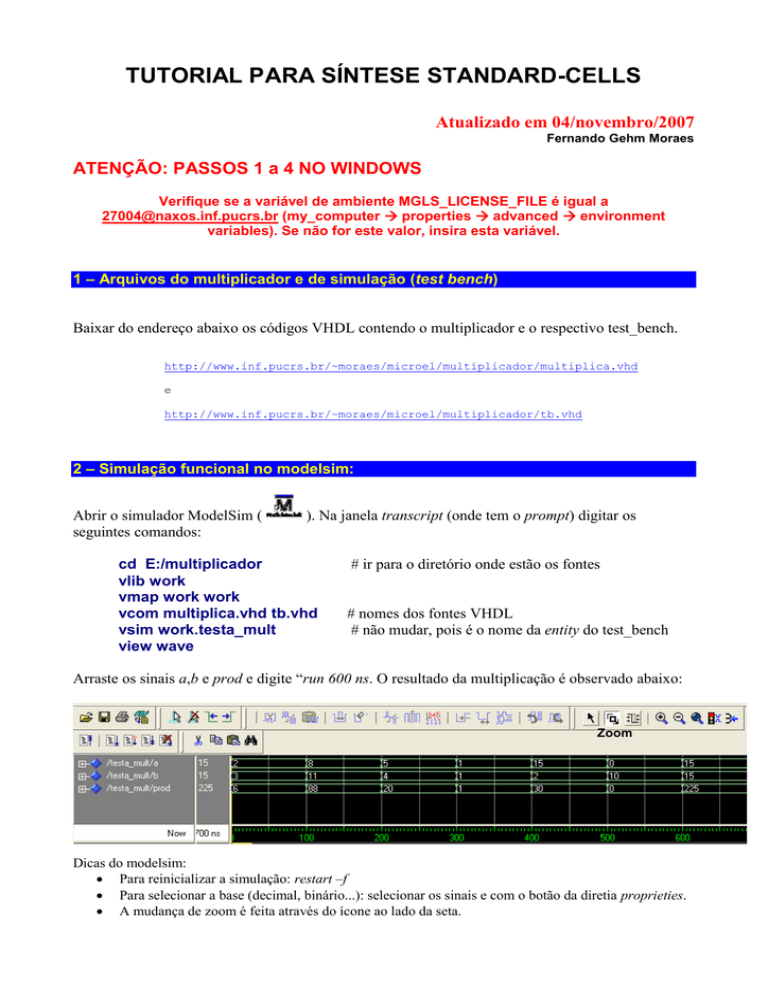

Arraste os sinais a,b e prod e digite “run 600 ns. O resultado da multiplicação é observado abaixo:

Zoom

Dicas do modelsim:

Para reinicializar a simulação: restart –f

Para selecionar a base (decimal, binário...): selecionar os sinais e com o botão da diretia proprieties.

A mudança de zoom é feita através do ícone ao lado da seta.

3 – Síntese Lógica

Após verificarmos o correto funcionamento lógico do circuito, devemos proceder à etapa de

síntese lógica. Nesta etapa é feita a tradução do VHDL para o nível de portas lógicas.

Para isto iremos utilizar a ferramenta Leonardo Spectrum

.

Para sintetizarmos o circuito, devemos indicar qual a tecnologia que iremos utilizar. No

presente tutorial iremos utilizar a tecnologia tsmc035 (0.35 microns).

É possível utilizar a ferramenta Leonardo em modo gráfico, mas o usual é utilizarmos

scripts. Salve os comando abaixo em um arquivo denominado synt.do

## ADKsynthesis script

set vhdl_write_component_package FALSE

set vhdl_write_use_packages {library ieee,adk; use ieee.std_logic_1164.all; use adk.all;}

set edifout_power_ground_style_is_net TRUE

load_library tsmc035_typ

analyze multiplica.vhd -format vhdl -work work

elaborate Mult_CSAdder -architecture Mult_CSAdder -work work

ungroup -all -hierarchy

optimize -ta tsmc035_typ -effort standard -macro -area

report_area -cell

write

write

write

mul_l.edf

mul_l.v

mul_l.sdf

-format edif

-format verilog

-format sdf

Abra a ferramenta Leonardo e: (1) usando comandos pwd / cd / dir ir para o diretório onde

está o script e o arquivo vhdl fonte; (2) digite no Leonardo sc synt.do para executar o script. O

script executa os passos acima para realizar a síntese lógica.

Este exemplo deve resultar em:

Cell

and02

aoi22

inv01

mux21

nand02

nand04

nor02

oai21

xnor2

Number

Number

Number

Number

Library References

tsmc035_typ

1 x

tsmc035_typ

3 x

tsmc035_typ

9 x

tsmc035_typ

7 x

tsmc035_typ

10 x

tsmc035_typ

3 x

tsmc035_typ

3 x

tsmc035_typ

1 x

tsmc035_typ

17 x

of

of

of

of

Total Area

1

1 gates

1

4 gates

1

7 gates

2

13 gates

1

10 gates

1

4 gates

1

3 gates

1

1 gates

2

32 gates

ports :

nets :

instances :

references to this view :

16

62

54

0

Total accumulated area :

Number of gates :

77

Number of accumulated instances :

54

-- Writing file mul_l.edf

-- Writing file mul_l.v

-- Writing file mul_l.sdf

Info, Command 'write' finished successfully

Notar que este multiplicador consumiu o equivalente a 77 portas lógicas nand2 equivalentes

(number of gates). Esta síntese gera três arquivos, dos quais 2 serão utilizados.:

1. mul_l.v descrição Verilog do arquivo multiplicador. Abrir e analisar este arquivo.

2. mul_l.sdf descrição dos atrasos das portas lógicas.

A escolha de saída Verilog deve-se à ferramenta de síntese física utilizada.

4 – Simulação SDF (com atraso de portas lógicas)

O terceiro passo no fluxo de projeto corresponde à simulação com atrasos. Para isto iremos

utilizar os arquivos verilog e sdf obtidos na etapa anterior.

Baixar da página a descrição da biblioteca:

http://www.inf.pucrs.br/~moraes/microel/multiplicador/adk.v

Recomendas-se criar um novo diretório, por exemplo atraso, e copiar neste diretório os

arquivos necessários (adk.v, mul_l.v, tb.vhd). Isto evita confusão entre as simulações com e sem

atraso.

Uma vez copiados os três arquivos necessários, digitar:

vlib

vmap

vlog

vlog

vcom

vsim

work

work work

adk.v

mul_l.v

tb.vhd

-sdfmax /multiplicador=mul_l.sdf -t 10ps work.testa_mult

Recomenda-se gravar estes 6 comandos em um arquivo, por exemplo atraso.do, e depois no

ModelSim apenas digitar do atraso.do.

Observações:

O comando vlog adk.v compila a biblioteca em formato verilog, pode demorar um pouco.

O parâmetro -sdfmax /multiplicador=mul_l.sdf liga o nome da instância definida no test

bench ao arquivo de atraso.

O parâmetro -t 10ps é utilizado para que seja possível a visualização dos atrasos.

Ao final do comando vsim deve aparecer o seguinte relatório:

#

#

#

#

#

Loading work.inv01

Loading work.mux2

Loading mul_l.sdf

** Note: (vsim-3587) SDF Backannotation Successfully Completed.

Time: 0 ps Iteration: 0 Region: /testa_mult File: tb.vhd

Simular 700 ns (run 700 ns) e observar os resultados. O resultado é aparentemente similar à

primeira simulação, com o circuito multiplicando corretamento.

O destaque na simulação corresponde à simulação de pior caso, que é multiplicar 1111 (15)

por 1111(15), que resulta em 1110000 (225). O atraso observado neste caso é de 1,62 ns.

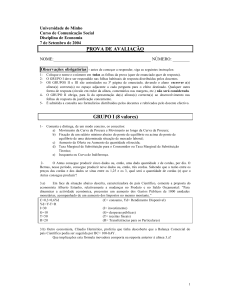

5 – Abrir o adk_ic e criar um projeto

digitar o comando adk_ic para abrir a janela principal do programa IC Station da mentor.

** IMPORTANTE: LANÇAR O ADK_IC NO DIRETÓRIO QUE ESTÁ O VERILOG **

no menu translate escolher a opção read verilog (descrição gerada pelo Leonardo, e já

simulada com atraso de portas). Preencha os campos conforme a figura abaixo:

a) Pressione OK. Depois de várias mensagens (inclusive de erros...) deverá aparecer uma janela

vazia.

b) Localize no menu à direita (IC Palletes) a opção “Place and Place”. Clique em menu “Plan and

Place”. No novo menu, em “flooplanner” clicar em “autofp”. Clicar em OK. Irá ser gerado um

desenho com área reservada para quatro linhas de células.

c) Clicar em “TOP” para voltar ao menu anterior (ou no menu superior ADK SHOW ADK

PALETTE). Clicar no menu “ADK_Edit” e depois “P&R”. Neste menu clicar no AutoPlace

“StdCell”. As células serão posicionadas conforme abaixo.

d) E depois AutoRoute All para que todas as conexões sejam realizadas.

e) Na janela acima enxergamos apenas o retângulo de cada célula, mas não o seu layout. Para ver o

layout: “Context hierarchy peek area”. Clique em “polygon” e selecione a área.

Para vizualizar os pinos de entrada e saída digite “”setup IC” e ative “port display”.

Medir com as réguas o tamanho do circuito. A unidade é (lambda). O circuito tem

aproximadamente 950 x 740 . Sabendo-se que um é igual a 0,12 m, o tamanho do

circuito é aproximadamente 114 m x 88,8 m, ou 10123,2 m2, ou 0,010123 mm2.

f) DRC (verificação de regras de projeto): usar o menu Calibre, nos menus superiores. Em rules

selecionar o arquivo de regras .

$ADK/technology/ic/process/tsmc035.rules

RUN DRC. Apesar de automatizado o fluxo, erros ocorrem. Nesta execução ocorreram

12 erros! .Abra o erro (clicando no símbolo ‘+’) até chegar na coordenada do erro. Neste

ponto, será possível visualizar onde ocorreu o erro.

Na janela abaixo mostram-se 4 erros de espaçamento de Metal 2:

Erro de DRC

.

g) Extração do SPICE para simulação no nível de transistores. No menu ICTrace(M) (menus da

direita!)

ICTrace(M) netlist hspice GEROU O NETLIST SPICE

(opção HSPICE / Substitue Slashes)

Neste menu indicar o nome do arquivo, e depois de gerado visualizá-lo.

Obtém-se o seguinte arquivo:

* File: ./net_mul.

Creation time: Sun Nov

4 18:32:06 2007

.subckt multiplicador A[0] A[1] A[2] A[3] B[0] B[1] B[2] B[3] GND P[0] P[1]

P[2]

+ P[3] P[4] P[5] P[6] P[7] VDD

* devices:

m0 170 nx82 VDD VDD p l=0.24u w=3.12u ad=1.1232p as=2.0232p

m1 171 nx210 VDD VDD p l=0.24u w=3.12u ad=1.1232p as=2.0232p

m2 172 nx70 VDD VDD p l=0.24u w=3.12u ad=1.1232p as=2.0232p

m3 173 nx250 P[1] VDD p l=0.24u w=1.56u ad=0.5616p as=0.9216p

m4 P[2] nx204 170 VDD p l=0.24u w=3.12u ad=2.0232p as=1.1232p

m5 nx208 nx212 171 VDD p l=0.24u w=3.12u ad=2.0232p as=1.1232p

m6 P[3] nx208 172 VDD p l=0.24u w=3.12u ad=2.0232p as=1.1232p

…………………………………………

m364 111 nx128 P[5] GND n l=0.24u w=1.2u ad=0.792p as=0.864p

m365 GND nx241 167 GND n l=0.24u w=1.2u ad=0.864p as=0.432p

m366 168 nx222 GND GND n l=0.24u w=1.2u ad=0.432p as=0.864p

m367 P[7] 109 168 GND n l=0.24u w=1.2u ad=0.792p as=0.432p

m368 169 nx128 GND GND n l=0.24u w=1.2u ad=0.432p as=0.792p

m369 110 nx255 169 GND n l=0.24u w=1.2u ad=0.792p as=0.432p

.ends multiplicador

O multiplicador de 4 bits consumiu 370 transistores. Fazendo a relação entre o número

de transistores e a área do circuito (0,01 mm2), obtém-se uma densidade de implementação

igual a 36550 transistores/ mm2.

salve este arquivo como mult.sp

h) Em um diretório para simulação coloque os arquivos mult.sp, tsmc035.mod e o arquivo de

simulação abaixo:

* circuito multiplicador obtido a partir do spice

*** modelo para tecnologia 0.35 microns

.include tsmc035.mod

*** arquivo obtido da extração

.include mult.sp

X1

C1

C2

C3

C4

C5

C6

C7

C8

a0 a1 a2 a3 b0 b1 b2 b3 0 p0 p1 p2 p3 p4 p5 p6 p7 vcc multiplicador

p0

p1

p2

p3

p4

p5

p6

p7

0

0

0

0

0

0

0

0

50fF

50fF

50fF

50fF

50fF

50fF

50fF

50fF

vcc vcc 0 dc 3.3

Vaa0

Vaa1

Vaa2

Vaa3

a0

a1

a2

a3

0

0

0

0

pwl(

pwl(

pwl(

pwl(

0n

0n

0n

0n

0

0

0

0

9.8n

9.8n

9.8n

9.8n

0

0

0

0

10n

10n

10n

10n

3.3

3.3

3.3

3.3

19.8n

19.8n

19.8n

19.8n

3.3

3.3

3.3

3.3

20n

20n

20n

20n

3.3

3.3

3.3

0

29.8n

29.8n

29.8n

29.8n

3.3

3.3

3.3

0

30n

30n

30n

30n

3.3

3.3

3.3

3.3

39.8n

39.8n

39.8n

39.8n

3.3

3.3

3.3

3.3

40n

40n

40n

40n

3.3

3.3

3.3

3.3

49.8n

49.8n

49.8n

49.8n

3.3)

3.3)

3.3)

3.3)

Vbb0

Vbb1

Vbb2

Vbb3

b0

b1

b2

b3

0

0

0

0

pwl(

pwl(

pwl(

pwl(

0n

0n

0n

0n

0

0

0

0

9.8n

9.8n

9.8n

9.8n

0

0

0

0

10n

10n

10n

10n

3.3

3.3

3.3

3.3

19.8n

19.8n

19.8n

19.8n

3.3

3.3

3.3

3.3

20n

20n

20n

20n

3.3

3.3

3.3

3.3

29.8n

29.8n

29.8n

29.8n

3.3

3.3

3.3

3.3

30n

30n

30n

30n

0

0

0

0

39.8n

39.8n

39.8n

39.8n

0

0

0

0

40n

40n

40n

40n

3.3

3.3

3.3

3.3

49.8n

49.8n

49.8n

49.8n

3.3)

3.3)

3.3)

3.3)

.options

**

* mede o tempo do atraso de subida

**

.measure tran trise trig v(a3) val=1.65

+

targ v(p7) val=1.65

td=2n rise = 1

rise = 1

**

* mede o tempo do atraso de descida

**

.measure tran tfall trig v(a3) val=1.65

+

targ v(p7) val=1.65

td=2n fall = 1

fall = 1

.TRAN .5N 55N

.END

No arquivo do modelo (tsmc035.mod) renomear os modelos para coincidir com o arquivo

extraído (houveram casos de ser nch/pch também – verificar o arquivo extraído).

.MODEL N NMOS (

.MODEL P PMOS (

LEVEL

LEVEL

= 53

= 53

Se houverem erros do tipo “nodo sem” verificar no layout se não tem porta de entrada ou

saída aberta. Um turn around possível para estes casos é colocar os pinos abertos na lista do

subcircuito (por exemplo, hipoteticamente o 51), e depois conectá-lo a vcc (no exemplo) ou

0.

.subckt multiplicador A[0] A[1] A[2] A[3] B[0] B[1] B[2] B[3] GND P[0] P[1] P[2]

+ P[3] P[4] P[5] P[6] P[7] VDD 51

X1

a0 a1 a2 a3 b0 b1 b2 b3 0 p0 p1 p2 p3 p4 p5 p6 p7 vcc vcc multiplicador

Estamos simulando:

A

B

produto

0

0

0

F

F

E1

7

F

69

F

0

0

F

F

E1

A simulação vai gerar o resultado apresentado na figura abaixo. Verifique o resultado

obtido na simulação com a tabela acima.

Observar o resultado nas medidas geradas com measure:

trise

1.181e-09

tfall

1.724e-09

temper

25.0000

alter#

1.0000

Ou seja, a simulação indicou como tempo crítico o tempo de descida, igual a 1,74 ns, um pouco

superior ao 1,62 ns obtido com a simulação com atraso lógico (SDF). Isto mostra que a simulação

com atraso SDF é confiável.

i) [não atualizado ainda] Última etapa. Comparação Layout versus Schematic (LVS), no menu top

(IC Palletes): VerifyDP(LVS) LVS. Indicar a referência para comparação contra o layout:

Nome do spice

extraído

Nome da instância

do somador no

arquivo spice

IMPORTANTE: no Setup LVS colocar “ignore ports”

O relatório gerado (lvs.rep) será:

##################################################

##

##

##

C A L I B R E

S Y S T E M

##

##

##

##

L V S

R E P O R T

##

##

##

##################################################

REPORT FILE NAME:

./lvs.rep

LAYOUT NAME:

$MGC_WD/multiplicador

SOURCE NAME:

./mult_net ('multiplicador')

RULE FILE:

/soft/design_kits/2006/adk_mentor_2.5/technology/ic/process/tsmc035.rules

LVS MODE:

Mask

RULE FILE NAME:

/soft/design_kits/2006/adk_mentor_2.5/technology/ic/process/tsmc035.rules

CREATION TIME:

Sun Nov 4 20:08:50 2007

CURRENT DIRECTORY:

/home/prof/moraes/multiplicador

USER NAME:

moraes

**********************************************************************************************

OVERALL COMPARISON RESULTS

******************************************************************************************

#

#

#

#

# #

#

###################

#

#

#

CORRECT

#

#

#

###################

_

*

_

*

|

\___/

-----------------------------------------------------------------------------------------------

INITIAL NUMBERS OF OBJECTS

--------------------------

Nets:

Instances:

Total Inst:

Layout

-----569

Source

-----202

185

185

-----370

185

185

-----370

Component Type

-------------*

MN (4 pins)

MP (4 pins)

j) Após o LVS posso explorar dentro do layout onde estão as redes. Por exemplo: show net by

name. Digite “p[3]” e veja dentro de layout onde está esta saída. Ou:

ICTrace(M) ==> Show Net by name (**)

k) Para salvar: File Cell Save Cell All Cells. Depois da edição deve-se reservar a célula

para edição: FILE->CELL->RESERVE