Prova P4/PS

Disciplina: Organização de Computadores-EC

Professor: Ney Laert Vilar Calazans

Aluno:

27/junho/2014

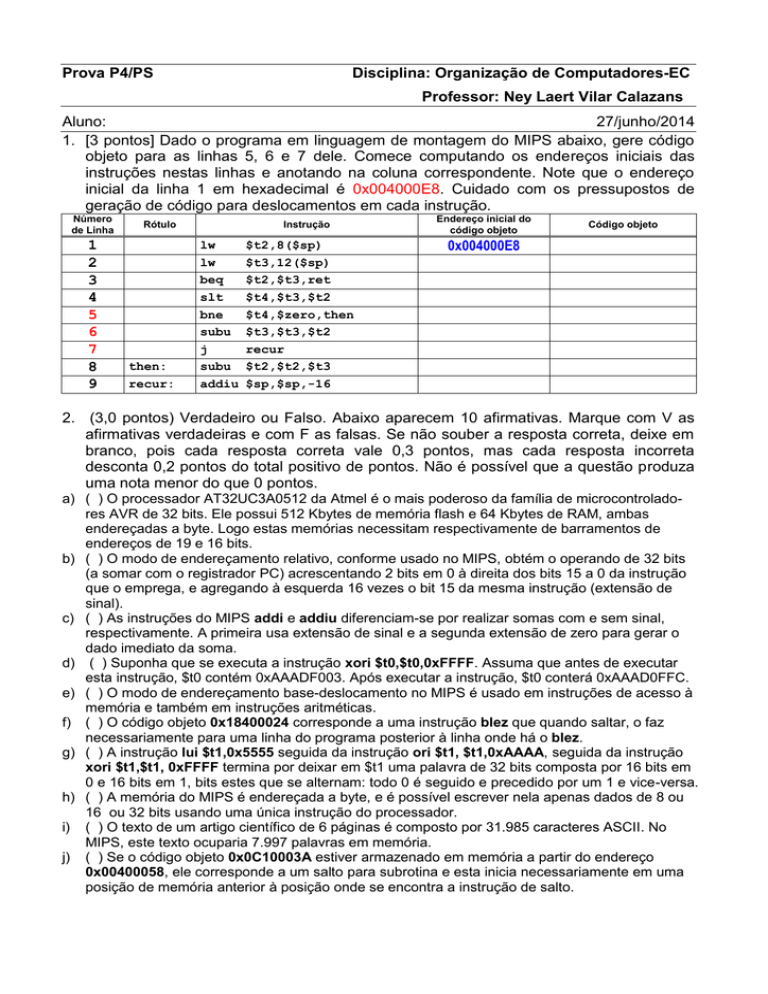

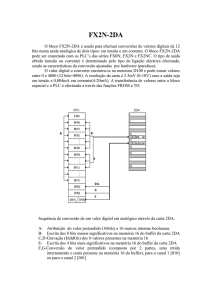

1. [3 pontos] Dado o programa em linguagem de montagem do MIPS abaixo, gere código

objeto para as linhas 5, 6 e 7 dele. Comece computando os endereços iniciais das

instruções nestas linhas e anotando na coluna correspondente. Note que o endereço

inicial da linha 1 em hexadecimal é 0x004000E8. Cuidado com os pressupostos de

geração de código para deslocamentos em cada instrução.

Número

de Linha

1

2

3

4

5

6

7

8

9

Rótulo

then:

recur:

Instrução

lw

lw

beq

slt

bne

subu

j

subu

addiu

$t2,8($sp)

$t3,12($sp)

$t2,$t3,ret

$t4,$t3,$t2

$t4,$zero,then

$t3,$t3,$t2

recur

$t2,$t2,$t3

$sp,$sp,-16

Endereço inicial do

código objeto

Código objeto

0x004000E8

2. (3,0 pontos) Verdadeiro ou Falso. Abaixo aparecem 10 afirmativas. Marque com V as

afirmativas verdadeiras e com F as falsas. Se não souber a resposta correta, deixe em

branco, pois cada resposta correta vale 0,3 pontos, mas cada resposta incorreta

desconta 0,2 pontos do total positivo de pontos. Não é possível que a questão produza

uma nota menor do que 0 pontos.

a) ( ) O processador AT32UC3A0512 da Atmel é o mais poderoso da família de microcontroladores AVR de 32 bits. Ele possui 512 Kbytes de memória flash e 64 Kbytes de RAM, ambas

endereçadas a byte. Logo estas memórias necessitam respectivamente de barramentos de

endereços de 19 e 16 bits.

b) ( ) O modo de endereçamento relativo, conforme usado no MIPS, obtém o operando de 32 bits

(a somar com o registrador PC) acrescentando 2 bits em 0 à direita dos bits 15 a 0 da instrução

que o emprega, e agregando à esquerda 16 vezes o bit 15 da mesma instrução (extensão de

sinal).

c) ( ) As instruções do MIPS addi e addiu diferenciam-se por realizar somas com e sem sinal,

respectivamente. A primeira usa extensão de sinal e a segunda extensão de zero para gerar o

dado imediato da soma.

d) ( ) Suponha que se executa a instrução xori $t0,$t0,0xFFFF. Assuma que antes de executar

esta instrução, $t0 contém 0xAAADF003. Após executar a instrução, $t0 conterá 0xAAAD0FFC.

e) ( ) O modo de endereçamento base-deslocamento no MIPS é usado em instruções de acesso à

memória e também em instruções aritméticas.

f) ( ) O código objeto 0x18400024 corresponde a uma instrução blez que quando saltar, o faz

necessariamente para uma linha do programa posterior à linha onde há o blez.

g) ( ) A instrução lui $t1,0x5555 seguida da instrução ori $t1, $t1,0xAAAA, seguida da instrução

xori $t1,$t1, 0xFFFF termina por deixar em $t1 uma palavra de 32 bits composta por 16 bits em

0 e 16 bits em 1, bits estes que se alternam: todo 0 é seguido e precedido por um 1 e vice-versa.

h) ( ) A memória do MIPS é endereçada a byte, e é possível escrever nela apenas dados de 8 ou

16 ou 32 bits usando uma única instrução do processador.

i) ( ) O texto de um artigo científico de 6 páginas é composto por 31.985 caracteres ASCII. No

MIPS, este texto ocuparia 7.997 palavras em memória.

j) ( ) Se o código objeto 0x0C10003A estiver armazenado em memória a partir do endereço

0x00400058, ele corresponde a um salto para subrotina e esta inicia necessariamente em uma

posição de memória anterior à posição onde se encontra a instrução de salto.

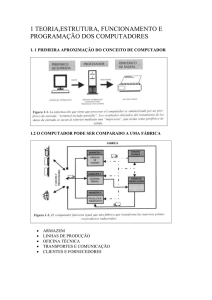

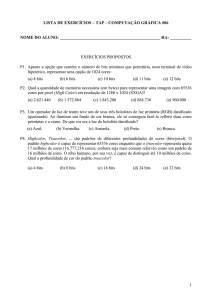

3. (4,0 pontos) Considere a organização do bloco de dados multiciclo abaixo, que

acomoda a execução de um subconjunto da arquitetura do conjunto de instruções do

processador MIPS. Em seguida, responda às questões que seguem a figura.

M1

result

npc

rst

D

Q

M2

uins.i

RNPC

ck

ce

npc

uins.CY1

dtpc

D

Q

rpc

ck

ce

uins.wpc

address data

Memória

de

Instruções

D

Q

RIR

ck

M3

20..16

M4

AdRs

R1

20..16

15..11

RD

AdRt

REGS

R2

uins.i

rst ck

uins.CY1

D

RS

ck

R2

D

s-extend*4

25..0

“0000” &

IR[25:0] & “00”

M6

op1

M5

M7

M7

uins.CY2

uins.i

rst

D

Q

RALU

ck

ce

uins.walu

result

RB

uins.ce

uins.rw

address

data

Memória

de Dados

data M8

uins.i

x“000000” &

data[7:0]

RB

rst

Q

RMDR

ck

ce

M9

uins.i

uins.i

uins.ce uins.bw

uins.rw

C

o

m

p

D

uins.wmdr

uins.i

IMED

D

A

L

U

Q

RA

cte_im

s-extend

15..0

RA

ce

0-extend

15..0

Q

uins.i

ce

uins.CY2

op2

rst

RB

RT

ck

wreg

uins.wreg

15..0

rst

AdRd

“11111”

ce

R1

outalu

20..16

adD

rst

ir=IR_OUT

rst

instruction

pc=i_address

RIN

adS

uins.i

25..21

MDR

incpc

mdr_int

4

+

RALU=d_address

uins.i

RALU

salta

Q

RIM

ck

uins.i

ce

uins.CY2

a) (1,0 pontos) Marcar no desenho acima e/ou descrever todos os caminhos do bloco de dados

efetivamente usados pela instrução JALR Rd, Rs. Isto significa marcar e/ou descrever em

texto todos os caminhos por onde passa informação útil relevante à execução da instrução,

ou seja, os dados e/ou endereços que esta realmente necessita manipular.

b) (1,0 pontos) Gere o código objeto da instrução JALR $gp, $s0.

c) (1,0 pontos) Diga qual operação é executada pela unidade lógica-aritmética (ALU) no

terceiro ciclo de relógio de uma instrução JALR Rd, Rs, justificando sua resposta.

d) (1,0 pontos) Para cada um dos sinais de controle diferente de uins.i, diga se e em que ciclo

da instrução JALR $gp, $s0 ele é ativado e, caso se aplique, diga qual o seu valor em

binário.

Prova P4/PS

Disciplina: Organização de Computadores-EC

Professor: Ney Laert Vilar Calazans

Aluno:

27/junho/2014

Gabarito

1. [3 pontos] Dado o programa em linguagem de montagem do MIPS abaixo, gere código

objeto para as linhas 5, 6 e 7 dele. Comece computando os endereços iniciais das

instruções nestas linhas e anotando na coluna correspondente. Note que o endereço

inicial da linha 1 em hexadecimal é 0x004000E8. Cuidado com os pressupostos de

geração de código para deslocamentos em cada instrução.

Número

de Linha

1

2

3

4

5

6

7

8

9

Rótulo

then:

recur:

Endereço inicial do

código objeto

Instrução

lw

lw

beq

slt

bne

subu

j

subu

addiu

$t2,8($sp)

$t3,12($sp)

$t2,$t3,ret

$t4,$t3,$t2

$t4,$zero,then

$t3,$t3,$t2

recur

$t2,$t2,$t3

$sp,$sp,-16

0x004000E8

0x004000EC

0x004000F0

0x004000F4

0x004000F8

0x004000FC

0x00400100

0x00400104

0x00400108

Código objeto

0x15800002

0x016A5823

0x08100042

Solução da Questão 1

a) (1,0 pontos) Linha 5: bne

$t4,$zero,then.

bne

5

Número de bits/campo: 6

O formato da instrução bne é:

rs rt label

rs rt offset

5 5

16

O código objeto é então: 000101 (5 em seis bits) concatenado com o endereço do Rs no banco

($t4=12 ou 01100 em binário), concatenado com o endereço do Rt no banco, 00000,

concatenado com o offset. Segundo a definição da arquitetura, este é o valor de 16 bits que

corresponde à distância, em instruções, da linha abaixo do bne até a linha do rótulo ou seja, 2 ou

em binário 0000 0000 0000 0010. Juntando os 32 bits (0001 0101 1000 0000 0000 0000 0000

0010) e traduzindo-os de 4 em 4 em valores hexadecimais, obtém-se 0x15800002, no endereço

da memória de instruções 0x004000F8.

b) (1,0 pontos) Linha 6: subu

$t3,$t3,$t2.

O formato da instrução subu é:

subu rd rs rt

0

rs rt rd 0 0x23

Número de bits/campo:

6

5 5 5 5 6

O código objeto é então: 000000 concatenado com 01011 (Rs=$t3=$11 ou 01011 em 5 bits),

concatenado com 01010 (Rt=$t2=$10 ou 01010 em 5 bits), concatenado com 01011 (Rd=$t3=$11

ou 01011 em 5 bits) concatenado com 00000100011. Juntando os 32 bits (0000 0001 0110 1010

0101 1000 0010 0011) e traduzindo-os de 4 em 4 em valores hexadecimais, obtém-se 0x016A5823,

no endereço da memória de instruções 0x004000FC.

c) (1,0 pontos) Linha 7: j recur. O formato da instrução j é:

j label

2 address

Número de bits/campo: 6

26

O código objeto é então: 000010 (2 em seis bits) concatenado com o pseudo-endereço. Para obter

este, parte-se do endereço de memória associado ao rótulo recur (0x00400108), e extrai-se os

quatro bits mais significativos e os dois bits menos significativos. O que sobra são os 26 bits do que

constituem o pseudo-endereço. Juntando estes 32 bits (0000 1000 0001 0000 0000 0000 0100

0010) e traduzindo-os de 4 em 4 em valores hexadecimais, obtém-se 0x08100042, no endereço da

memória de instruções 0x00400100.

Fim da Solução da Questão 1

2. (3,0 pontos) Verdadeiro ou Falso. Abaixo aparecem 10 afirmativas. Marque com V as

afirmativas verdadeiras e com F as falsas. Se não souber a resposta correta, deixe em

branco, pois cada resposta correta vale 0,3 pontos, mas cada resposta incorreta

desconta 0,2 pontos do total positivo de pontos. Não é possível que a questão produza

uma nota menor do que 0 pontos.

a) (V) O processador AT32UC3A0512 da Atmel é o mais poderoso da família de microcontroladores AVR de 32 bits. Ele possui 512 Kbytes de memória flash e 64 Kbytes de RAM, ambas

endereçadas a byte. Logo estas memórias necessitam respectivamente de barramentos de

endereços de 19 e 16 bits.

b) (F) O modo de endereçamento relativo, conforme usado no MIPS, obtém o operando de 32 bits

(a somar com o registrador PC) acrescentando 2 bits em 0 à direita dos bits 15 a 0 da instrução

que o emprega, e agregando à esquerda 16 vezes o bit 15 da mesma instrução (extensão de

sinal).

c) (F) As instruções do MIPS addi e addiu diferenciam-se por realizar somas com e sem sinal,

respectivamente. A primeira usa extensão de sinal e a segunda extensão de zero para gerar o

dado imediato da soma.

d) (V) Suponha que se executa a instrução xori $t0,$t0,0xFFFF. Assuma que antes de executar

esta instrução, $t0 contém 0xAAADF003. Após executar a instrução, $t0 conterá 0xAAAD0FFC.

e) (F) O modo de endereçamento base-deslocamento no MIPS é usado em instruções de acesso à

memória e também em instruções aritméticas.

f) (V) O código objeto 0x18400024 corresponde a uma instrução blez que quando saltar, o faz

necessariamente para uma linha do programa posterior à linha onde há o blez.

g) (V) A instrução lui $t1,0x5555 seguida da instrução ori $t1, $t1,0xAAAA, seguida da instrução

xori $t1,$t1, 0xFFFF termina por deixar em $t1 uma palavra de 32 bits composta por 16 bits em

0 e 16 bits em 1, bits estes que se alternam: todo 0 é seguido e precedido por um 1 e vice-versa.

h) (V) A memória do MIPS é endereçada a byte, e é possível escrever nela apenas dados de 8 ou

16 ou 32 bits usando uma única instrução do processador.

i) (V) O texto de um artigo científico de 6 páginas é composto por 31.985 caracteres ASCII. No

MIPS, este texto ocuparia 7.997 palavras em memória.

j) (F) Se o código objeto 0x0C10003A estiver armazenado em memória a partir do endereço

0x00400058, ele corresponde a um salto para subrotina e esta inicia necessariamente em uma

posição de memória anterior à posição onde se encontra a instrução de salto.

Solução da Questão 2

a) (V) 512Kbytes e endereçamento a byte implicam a necessidade de log2 (512K) linhas de

endereço. Como 512=29, e 1K=210, o logaritmo de 512K é 19. O mesmo raciocínio conduz

a computar log2 (64K)=16. Logo a afirmativa é VERDADEIRA.

b) (F) Ao aplicar o procedimento descrito neste item produz-se um valor de 34 bits e não 32

(bits 15-0 + 00 + 16 bits de extensão). Logo a afirmativa só pode ser FALSA.

c) (F) Há dois erros nesta questão. Primeiro, as instruções não fazem somas de forma

diferenciada, pois a representação em complemento de 2 garante que soma com e sem

sinal não operam de forma distinta. O segundo erro é que ambas usam extensão de sinal

para gerar a constante de 32 bits. Logo a afirmativa é FALSA.

d) (V) A instrução xori usa extensão de 0. Logo o valor a ser operado na ULA com o conteúdo

do registrador $t0 é 0x0000FFFF. Ora, dada a natureza da operação lógica XOR, este

valor vai manter os 16 bits mais significativos de $t0 inalterados (“xoreados” com 0) e vai

inverter os 16 bits menos significativos de $t0 (“xoreados” com 1), o que produzirá em $t0

o novo valor, que será: 0xAAADF00C, pois 0x0 invertido dá 0xF, 0xF invertido dá 0x0 e

0x3 invertido dá 0xC. Logo a afirmativa é VERDADEIRA.

e) (F) O modo base deslocamento somente é usado para instruções de acesso à memória.

Logo a afirmativa é FALSA.

f) (V) Os seis primeiros bits de 0x18400024 são 000110 ou 6 em decimal, o que segundo a

Tabela A.10.2 do Apêndice A identifica a instrução blez. Logo esta parte do item está certa.

Esta instrução usa modo de endereçamento relativo e o endereço de salto será o resultado

de adicionar o PC ao offset da instrução (bits 15-0 do código objeto) com sinal estendido e

multiplicado por 4, para gerar um valor constante de 32 bits. Como os bits 15-0 da

instrução são 0x0024, a extensão produzirá 0x00000024, que multiplicado por 4 fica

0x00000090. Como este valor é positivo, somado aos valores normais do PC (em torno de

0x00400000) certamente gera um endereço de memória maior que aquele contido no PC

ao iniciar a execução da instrução. Logo o salto é para a frente, para linha do programa

posterior à linha da instrução blez. Logo a afirmativa é VERDADEIRA.

g) (V) lui gera em $t1 o valor 0x55550000. A ori deixa em $t1 0x5555AAAA. Finalmente o xori

inverte os 16 bits menos significativos de $t1, gerando 0x55555555, pois o inverso de 0xA

(1010 em binário) é 0x5 (0101 em binário). O padrão de 8 valores 0x5 corresponde ao

valor binário de 32 bits 0101 0101 0101 0101 0101 0101 0101 0101. Logo a afirmativa é

VERDADEIRA.

h) (V) As instruções sb, sh e sw permitem escrever 1 byte, 2 bytes e 4 bytes na memória,

respectivamente. Logo a afirmativa é VERDADEIRA.

i) (V) Cada caractere ASCII ocupa exatamente 1 byte e no MIPS cada 4 bytes correspondem a

uma palavra. Tomando o valor múltiplo de 4 mais próximo do tamanho do arquivo, têm-se

31.988, que dividido por 4 fornece 7.997. Logo a afirmativa é VERDADEIRA.

j) (F) Os seis primeiros bits de 0x0C10003A são 000011 ou 3 em decimal, o que segundo a

Tabela A.10.2 do Apêndice A identifica a instrução jal. Logo esta parte da afirmativa é

correta, pois trata-se de um salto para subrotina. O endereço onde a subrotina inicia é

obtido tomando-se os 26 bits menos significativos do código objeto acrescentando-se dois

bits em 0 à direita destes e colocando à esquerda deste os quatro bits mais significativos

do valor do PC no momento da execução da instrução. O valor do PC no momento da

execução será 0x00400058 + 4, ou seja, 0x0040005C. Assim o endereço da subrotina

para onde se deve saltar é 0000 & 00 0001 0000 0000 0000 0011 1010 & 00, ou seja

0x004000E8, que é posterior ao jal. Logo a afirmativa é FALSA.

Fim da Solução da Questão 2

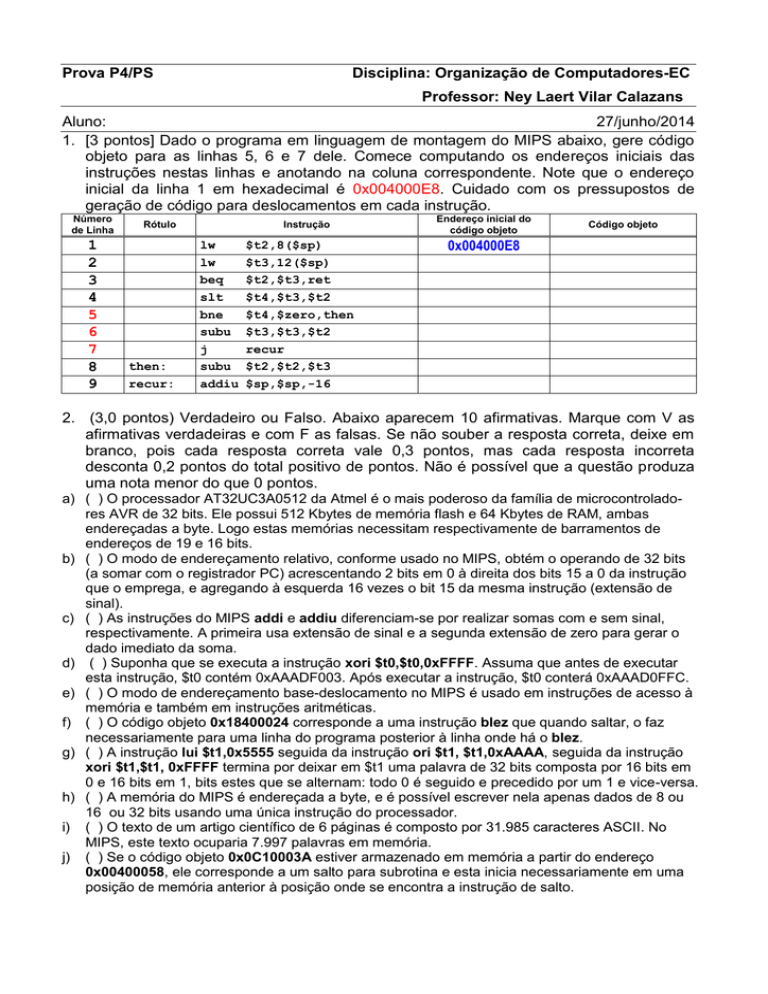

3. (4,0 pontos) Considere a organização do bloco de dados multiciclo abaixo, que

acomoda a execução de um subconjunto da arquitetura do conjunto de instruções do

processador MIPS. Em seguida, responda às questões que seguem a figura.

M1

result

npc

D

Q

M2

uins.i

RNPC

ck

ce

npc

uins.CY1

dtpc

D

PC

ck

Q

ce

uins.wpc

address data

Memória

de

Instruções

D

IR

ck

Q

M3

20..16

d

M4

AdRs

R1

20..16

15..11

RD

AdRt

REGS

R2

uins.i

rst ck

uins.CY1

D

RS

ck

R2

D

s-extend*4

25..0

“0000 ” &

IR[25:0] & “00”

op1

M5

M7

M7

uins.CY2

uins.i

rst

D

Q

RALU

ck

ce

uins.walu

result

RB

uins.ce

uins.rw

address

data

Memória

de Dados

data M8

uins.i

x“0000 00” &

data[7:0]

RB

rst

Q

RMDR

ck

ce

M9

uins.i

uins.i

uins.ce uins.bw

uins.rw

C

o

m

p

D

uins.wmdr

uins.i

IMED

D

D

A

L

U

Q

RA

cte_im

s-extend

15..0

M6

ce

0-extend

15..0

Q

RA

uins.i

ce

uins.CY2

op2

rst

RB

RT

ck

wreg

uins.wreg

15..0

rst

AdRd

“11111 ”

ce

R1

outalu

20..16

adD

rst

ir=IR_OUT

rst

instruction

pc=i_address

RIN

adS

uins.i

25..21

MDR

+

rst

mdr_int

4

incpc

RALU=d_address

uins.i

RALU

salta

Q

IMED

ck

uins.i

ce

uins.CY2

a) (1,0 pontos) Marcar no desenho acima e/ou descrever todos os caminhos do bloco de dados

efetivamente usados pela instrução JALR Rd, Rs. Isto significa marcar e/ou descrever em

texto todos os caminhos por onde passa informação útil relevante à execução da instrução,

ou seja, os dados e/ou endereços que esta realmente necessita manipular.

b) (1,0 pontos) Gere o código objeto da instrução JALR $gp, $s0.

c) (1,0 pontos) Diga qual operação é executada pela unidade lógica-aritmética (ALU) no

terceiro ciclo de relógio de uma instrução JALR Rd, Rs, justificando sua resposta.

d) (1,0 pontos) Para cada um dos sinais de controle diferente de uins.i, diga se e em que ciclo

da instrução JALR $gp, $s0 ele é ativado e, caso se aplique, diga qual o seu valor em

binário.

Solução da Questão 3

a) (1,0 pontos). Ver desenho.

b) (1,0 pontos). JALR $gp, $s0 – Formato R: seis campos de 6, 5, 5, 5, 5, 5 e 6 bits, com

valores respectivos (em hexa): 0 10 0 1C 0 9. Isto convertido em binário dá: 000000 10000

00000 11100 00000 001001. Em hexadecimal o código objeto fica: 0x0200E009.

c) (1,0 pontos). A operação executada na ALU é passar o que está na entrada op1 para a

saída da ALU outalu. Este é o valor do registrador Rs, que contém o endereço a ser

carregado em RALU, e que posteriormente (no próximo ciclo) será transferido para o PC (o

endereço de início da subrotina para onde JALR salta).

d) (1,0 pontos). Observando os sinais da palavra de microinstrução produzida no Bloco de

Controle, nota-se que existem 11 sinais além do sinal uins.i. Os sinais, se eles são ou não

ativados, e o valor binário deles quando ativados são:

1.

uins.CY1

- Ativado (em ‘1’) no primeiro ciclo

2.

uins.CY2

- Ativado (em ‘1’) no segundo ciclo

3.

uins.walu

- Ativado (em ‘1’) no terceiro ciclo

4.

uins.wmdr

- Não ativado (fica em ‘0’) ao longo de toda a instrução

5.

uins.wpc

- Ativado (em ‘1’) no quarto ciclo

6.

uins.wreg

- Ativado (em ‘1’) no quarto ciclo

7.

uins.whilo

- Não ativado (fica em ‘0’) ao longo de toda a instrução

8.

uins.ce

- Não ativado (fica em ‘0’) ao longo de toda a instrução

9.

uins.rw

- Irrelevante, mas não ativado (fica em ‘1’) ao longo de toda a instrução

10.

uins.bw

- Irrelevante, mas não ativado (fica em ‘1’) ao longo de toda a instrução

11.

uins.rst_md - Não ativado (fica em ‘0’) ao longo de toda a instrução

Fim da Solução da Questão 3