FLIP - FLOP

Os circuitos lógicos estudados até agora são circuitos combinacionais nos

quais as saídas, em qualquer instante de tempo, depende de níveis

presentes nas entradas no instante considerado.

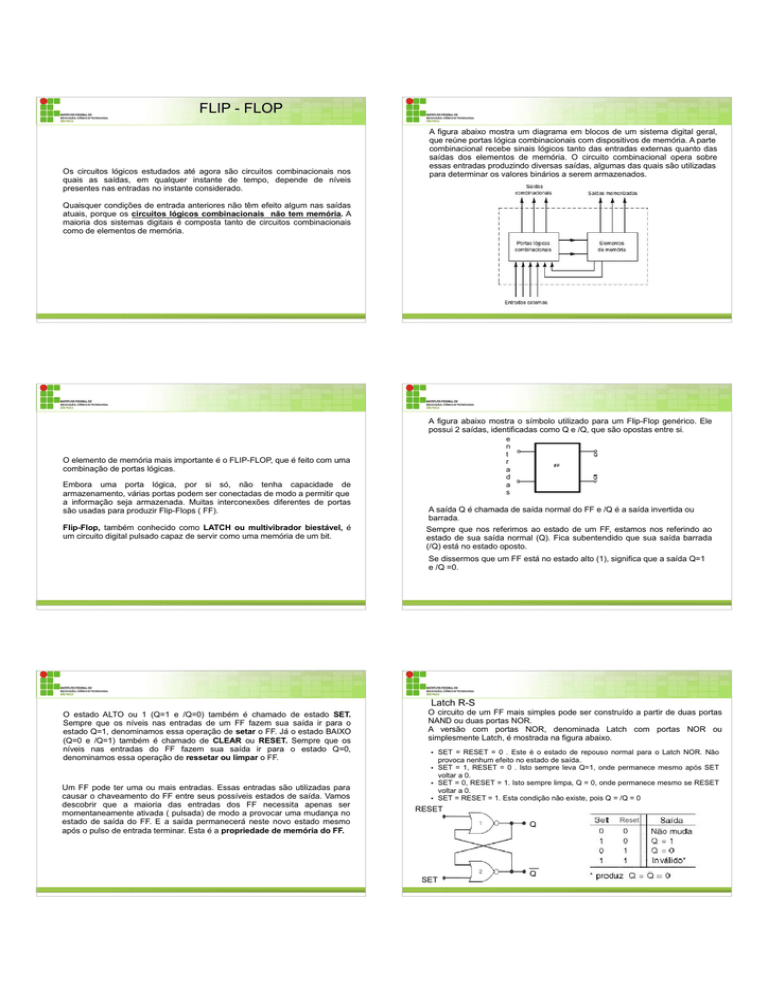

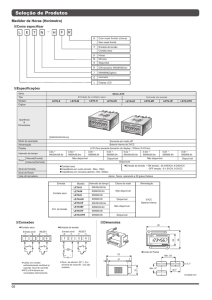

A figura abaixo mostra um diagrama em blocos de um sistema digital geral,

que reúne portas lógica combinacionais com dispositivos de memória. A parte

combinacional recebe sinais lógicos tanto das entradas externas quanto das

saídas dos elementos de memória. O circuito combinacional opera sobre

essas entradas produzindo diversas saídas, algumas das quais são utilizadas

para determinar os valores binários a serem armazenados.

Quaisquer condições de entrada anteriores não têm efeito algum nas saídas

atuais, porque os circuitos lógicos combinacionais não tem memória. A

maioria dos sistemas digitais é composta tanto de circuitos combinacionais

como de elementos de memória.

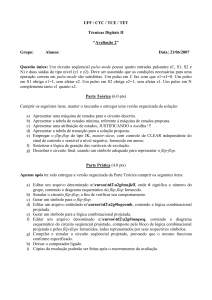

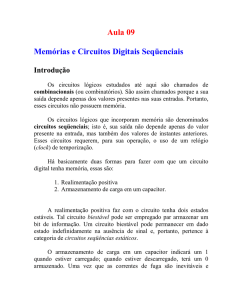

A figura abaixo mostra o símbolo utilizado para um Flip-Flop genérico. Ele

possui 2 saídas, identificadas como Q e /Q, que são opostas entre si.

e

n

t

r

a

d

a

s

O elemento de memória mais importante é o FLIP-FLOP, que é feito com uma

combinação de portas lógicas.

Embora uma porta lógica, por si só, não tenha capacidade de

armazenamento, várias portas podem ser conectadas de modo a permitir que

a informação seja armazenada. Muitas interconexões diferentes de portas

são usadas para produzir Flip-Flops ( FF).

Flip-Flop, também conhecido como LATCH ou multivibrador biestável, é

um circuito digital pulsado capaz de servir como uma memória de um bit.

A saída Q é chamada de saída normal do FF e /Q é a saída invertida ou

barrada.

Sempre que nos referimos ao estado de um FF, estamos nos referindo ao

estado de sua saída normal (Q). Fica subentendido que sua saída barrada

(/Q) está no estado oposto.

Se dissermos que um FF está no estado alto (1), significa que a saída Q=1

e /Q =0.

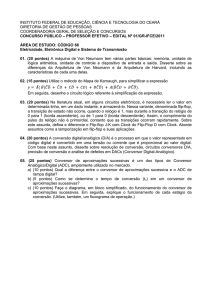

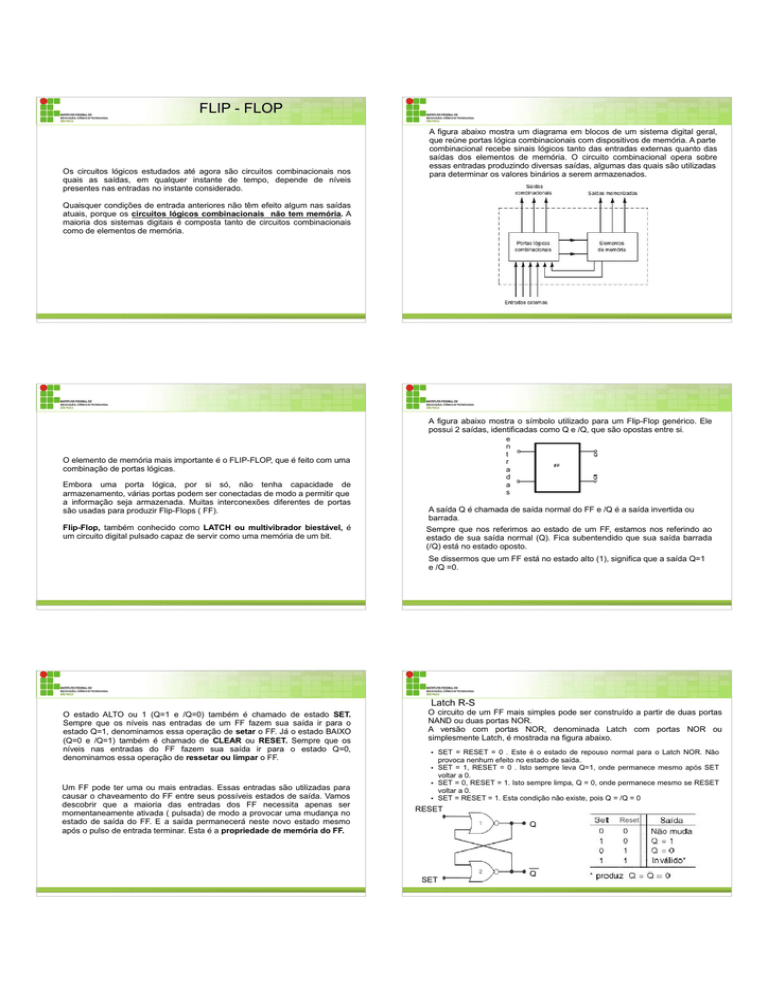

Latch R-S

O estado ALTO ou 1 (Q=1 e /Q=0) também é chamado de estado SET.

Sempre que os níveis nas entradas de um FF fazem sua saída ir para o

estado Q=1, denominamos essa operação de setar o FF. Já o estado BAIXO

(Q=0 e /Q=1) também é chamado de CLEAR ou RESET. Sempre que os

níveis nas entradas do FF fazem sua saída ir para o estado Q=0,

denominamos essa operação de ressetar ou limpar o FF.

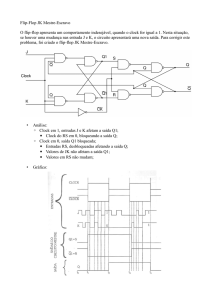

O circuito de um FF mais simples pode ser construído a partir de duas portas

NAND ou duas portas NOR.

A versão com portas NOR, denominada Latch com portas NOR ou

simplesmente Latch, é mostrada na figura abaixo.

●

●

●

Um FF pode ter uma ou mais entradas. Essas entradas são utilizadas para

causar o chaveamento do FF entre seus possíveis estados de saída. Vamos

descobrir que a maioria das entradas dos FF necessita apenas ser

momentaneamente ativada ( pulsada) de modo a provocar uma mudança no

estado de saída do FF. E a saída permanecerá neste novo estado mesmo

após o pulso de entrada terminar. Esta é a propriedade de memória do FF.

●

SET = RESET = 0 . Este é o estado de repouso normal para o Latch NOR. Não

provoca nenhum efeito no estado de saída.

SET = 1, RESET = 0 . Isto sempre leva Q=1, onde permanece mesmo após SET

voltar a 0.

SET = 0, RESET = 1. Isto sempre limpa, Q = 0, onde permanece mesmo se RESET

voltar a 0.

SET = RESET = 1. Esta condição não existe, pois Q = /Q = 0

RESET

Q

SET

Q

Reset

Latch R-S

A versão com portas NAND, denominada Latch com portas NAND ou

simplesmente Latch, é mostrada na figura abaixo

Latch R-S

As saídas das portas, em condições normais, estão sempre em níveis

lógicos inversos. Existem duas entradas no latch: SET é a que seta Q para o

estado 1; a entrada RESET é a que reseta Q para o estado 0

As entradas estão normalmente em repouso no estado ALTO, euma delas é

pulsada em nível baixo sempre que se deseja alterar as saídas do latch.

Inicialmente, se SET = RESET = 1, pode-se levar a duas configurações.

Denominada de lógica reversa

Latch R-S

Quando a entrada SET é momentaneamente pulsada em nível BAIXO, enquanto a

entrada RESET é mantida em nível ALTO, há mudança nas saídas do latch.

●

●

●

●

SET = RESET = 1 É o estado normal de Repouso e não tem nenhum efeito

sobre o estado de saída.

SET = 0, RESET = 1. Sempre faz a saída ir para o estado em que Q=1. Este

permanecerá, mesmo que SET volte a 1.

SET = 1, RESET = 0. Sempre gera um estado de saída em que Q=0.

SET = RESET = 0. Q = /Q= 1 . Situação inexistente.

A figura abaixo demonstra essa mudança para uma das condições anteriormente

vistas do latch.

FLIP-FLOP

Quatro tipos de Flip-Flops possuem 8 aplicações comuns em sistemas de clock nãosequencial: Flip-Flop T ("toggle"), Flip-Flop S-R ("set-reset"), Flip-Flop J-K e o Flip-Flop

D ("data").O comportamento de um Flip-Flop é descrito por sua equação característica,

que prevê a "próxima" (após o próximo pulso de clock) saída, em termos dos sinais de

entrada e/ou da saída atual.

O Flip-Flop pode ser utilizado para armazenar um bit, ou um digito binário de

informação. A informação armazenada em um conjunto de Flip-Flops pode

representar o estado de um sequenciador, o valor de um contador, um caractere

ASCII em uma memória de um computador ou qualquer outra parte de uma

informação.

Um utilização comum é a construção de máquinas de estado finito a partir da

lógica eletrônica. O Flip-Flop lembra o estado anterior de máquina, e a lógica

digital utiliza este estado para calcular o próximo estado.

FLIP-FLOPTIPO D

Este Flip-Flop possui uma única entrada que comanda todo o circuito.

Esta entrada é que lhe dá nome. Denominada “Data” (dados), é abreviada por D, daí o

nome do dispositivo.

Este Flip-Flop opera de uma maneira muito simples: no pulso de clock, ele assume o

estado da entrada, conforme podemos ver pela sua tabela verdade:

A entrada ENABLE serve para habilitar ou desabilitar o CLOCK

FLIP-FLOP TIPO T

O nome vem de “Toggle”ou complementação

Quando a entrada T deste circuito está no nível baixo, o Flip-Flop se mantém em seu

estado anterior, mesmo com a aplicação do pulso de clock.

No entanto, quando a entrada T está no nível alto, o Flip-Flop muda de estado. Se

estava setado, ele resseta e se estava ressetado, ele seta.

Este comportamento significa na realidade a divisão da frequência de clock por dois. Em

outras palavras, este circuito se comporta como um divisor de frequência, encontrando

aplicações práticas bastante importantes em Eletrônica Digital.

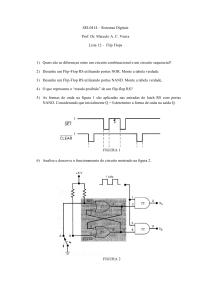

FLIP-FLOP J-K

Um problema que observamos nos Flip-Flops R-S é que temos uma situação “proibida”

que ocorre quando as entradas R e S vão ao nível alto ao mesmo tempo e que pode

levar o circuito a um estado indeterminado.

Esta situação acontece principalmente nas aplicações em computação,quando uma

parte do sinal de saída é usada para realimentar a entrada. Nestas condições podem

ocorrer as situações de conflito com a produção de oscilações indesejadas.

Esta situação pode ser contornada com a utilização de uma nova configuração, que é

justamente a do Flip-Flop J-K utilizada nas aplicações práticas e que analisaremos a

seguir.

Podemos ter quatro combinações possíveis para os sinais aplicados nas entradas J e

K, conforme observamos na tabela abaixo.

J

0

1

0

1

a) J=0 e K=0

Quando a entrada de clock (CLK) passa por uma transição negativa do sinal, o Flip-Flop

mantém sua condição original, ou seja, não muda de estado.

b) J=1 e K=0

Quando a entrada de clock (CLK) passa por uma transição negativa, o Flip-Flop é

“setado”. Se já estiver setado, ele permanece nesta condição.

c) J=0 e K=1

Quando a entrada de clock (CLK) passa por uma transição negativa, o Flip-Flop é

“ressetado”. Se já estiver nesta condição, ele permanece.

d) J=1 e K=1

Nesta condição, ao receber uma transição negativa na entrada de clock (CLK),o Flip-Flop

muda de estado (TOGGLE). Se estiver setado, ele resseta e se estiver ressetado, ele é

setado.

K

0

0

1

1

FLIP-FLOP J-K com SET e RESET

REFERENCIAS BIBLIOGRÁFICAS

●

●

Tocci, Ronald J., Sistemas Digitais - 10º Edição - Neal S. Widner e

Gregory L. Moss

Curso de Eletrônica Digital, Revista SABER ELETRÔNICA,

ESPECIAL Nº 8 - 2002