Introdução a Sistemas Digitais

Lista de Exercı́cios: Circuitos Sequenciais

Nome do aluno:

1. Qual a diferença entre os circuitos combinacionais e os circuitos sequenciais?

2. Qual a diferença entre um circuito sequencial level-triggered e um circuito sequencial edge-triggered ?

3. Qual a diferença entre o latch tipo D e o flip-flop tipo D?

4. Em aula, estudamos o latch Set-Reset implementado com 2 portas NOR. Implemente o latch

Set-Reset com 2 portas NAND.

5. Em aula, estudamos o latch tipo D sensı́vel ao nı́vel 1 do clock. Implemente o latch tipo D sensı́vel

ao nı́vel 0 do clock.

6. Em que situação o sinal de saı́da Q de um latch tipo D não muda de valor?

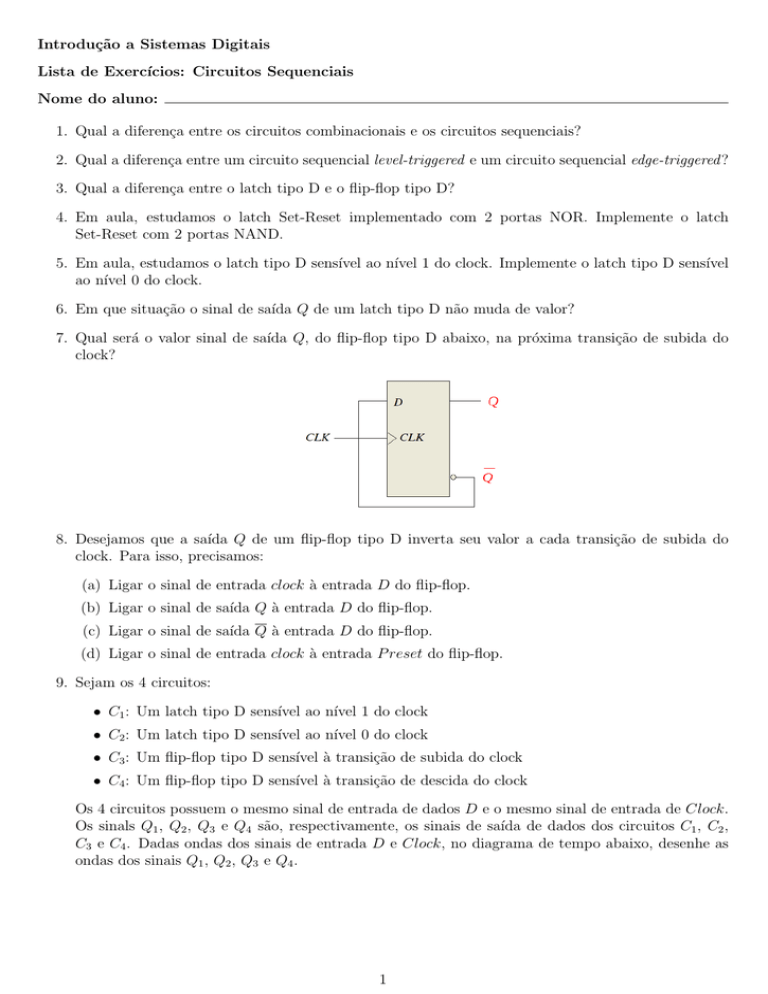

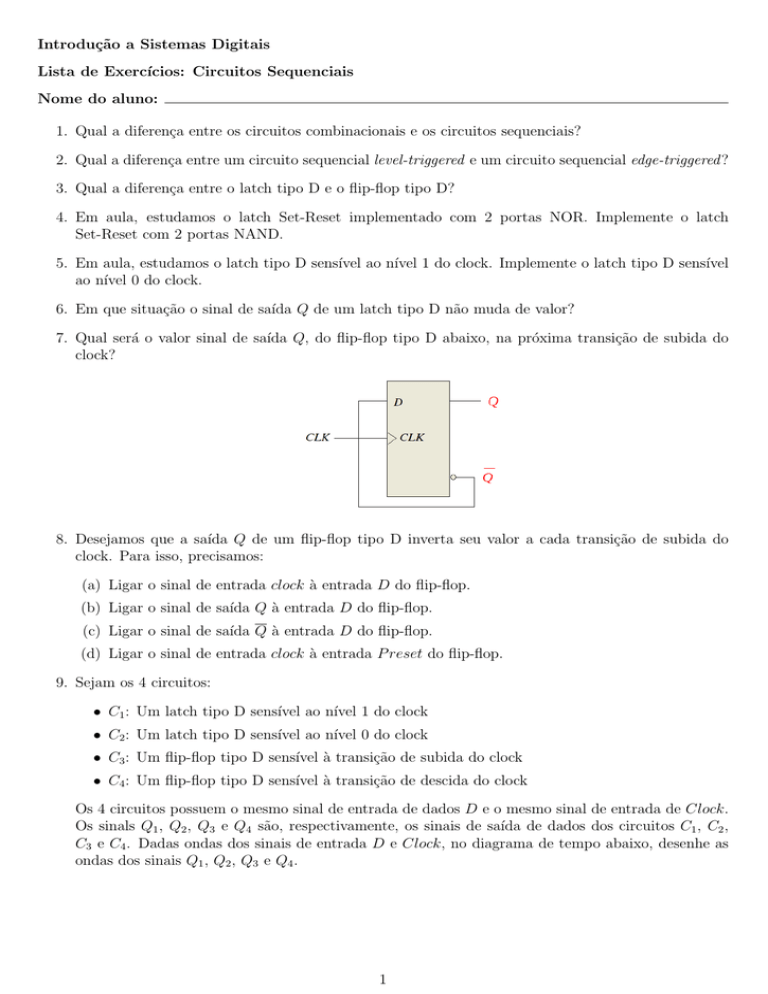

7. Qual será o valor sinal de saı́da Q, do flip-flop tipo D abaixo, na próxima transição de subida do

clock?

8. Desejamos que a saı́da Q de um flip-flop tipo D inverta seu valor a cada transição de subida do

clock. Para isso, precisamos:

(a) Ligar o sinal de entrada clock à entrada D do flip-flop.

(b) Ligar o sinal de saı́da Q à entrada D do flip-flop.

(c) Ligar o sinal de saı́da Q à entrada D do flip-flop.

(d) Ligar o sinal de entrada clock à entrada P reset do flip-flop.

9. Sejam os 4 circuitos:

• C1 : Um latch tipo D sensı́vel ao nı́vel 1 do clock

• C2 : Um latch tipo D sensı́vel ao nı́vel 0 do clock

• C3 : Um flip-flop tipo D sensı́vel à transição de subida do clock

• C4 : Um flip-flop tipo D sensı́vel à transição de descida do clock

Os 4 circuitos possuem o mesmo sinal de entrada de dados D e o mesmo sinal de entrada de Clock.

Os sinals Q1 , Q2 , Q3 e Q4 são, respectivamente, os sinais de saı́da de dados dos circuitos C1 , C2 ,

C3 e C4 . Dadas ondas dos sinais de entrada D e Clock, no diagrama de tempo abaixo, desenhe as

ondas dos sinais Q1 , Q2 , Q3 e Q4 .

1

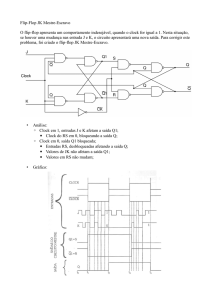

10. Qual circuito está implementado na figura abaixo?

11. Na figura abaixo?

(a) Qual circuito está implementado?

(b) O que ocorre quando o sinal SHIF T /LOAD está em 0?

(c) O que ocorre quando o sinal SHIF T /LOAD está em 1?

2

12. A figura abaixo representa um shift register de 8 bits, serial-in, serial-out. Um dado serial é fornecido

na entrada. Quantos ciclos do clock depois, o primeiro bit de entrada aparecerá na saı́da serial?

13. Qual shift register devemos utilizar para atrasar um dado serial em 4 ciclos do clock?

14. Implemente um contador sı́ncrono de 4 bits, usando flip-flops.

15. Dado o circuito contador sı́ncrono de 4 bits, mostre as ondas (em um diagrama de tempo) dos sinais

clock, Q0 , Q1 , Q2 e Q3 . Suponha que inicialmente todos os sinais estão em 0. Apresente o diagrama

até o 17o ciclo do clock.

16. Qual o valor máximo atingido por um contador crescente de 4 bits?

17. A figura abaixo mostra a sequência de contagem de um contador de 3 bits diferente dos estudados.

O sinal Q2 representa o bit mais significativo. Qual são os valores da sequência de contagem?

18. Um contador assı́ncrono crescente de 4 bits recebe um sinal de entrada clock com frequência de

80KHz. Qual será a frequência da saı́da Q3 do último flip-flop (mais significativo)?

19. Implemente um circuito que tem como entrada um sinal de clock CLKin com uma determinada

frequência f , e gera como saı́da outro sinal de clock CLKout com uma frequência que seja a metade

de f . Isto é, o perı́odo de CLKout é o dobro do perı́odo de CLKin .

3