Aula 09

Memórias e Circuitos Digitais Seqüenciais

Introdução

Os circuitos lógicos estudados até aqui são chamados de

combinacionais (ou combinatórios). São assim chamados porque a sua

saída depende apenas dos valores presentes nas suas entradas. Portanto,

esses circuitos não possuem memória.

Os circuitos lógicos que incorporam memória são denominados

circuitos seqüenciais; isto é, sua saída não depende apenas do valor

presente na entrada, mas também dos valores de instantes anteriores.

Esses circuitos requerem, para sua operação, o uso de um relógio

(clock) de temporização.

Há basicamente duas formas para fazer com que um circuito

digital tenha memória, essas são:

1. Realimentação positiva

2. Armazenamento de carga em um capacitor.

A realimentação positiva faz com o circuito tenha dois estados

estáveis. Tal circuito biestável pode ser empregado par armazenar um

bit de informação. Um circuito biestável pode permanecer em dado

estado indefinidamente na ausência de sinal e, portanto, pertence à

categoria de circuitos seqüências estáticos.

O armazenamento de carga em um capacitor indicará um 1

quando estiver carregado; quando estiver descarregado, terá um 0

armazenado. Uma vez que as correntes de fuga são inevitáveis e

causam a descarga do capacitor, ele necessitará ser regenerado

periodicamente, no processo conhecido como restauração. Portanto,

como na lógica dinâmica, memórias baseadas no armazenamento de

cargas são conhecidas como memórias dinâmicas e pertencem à classe

de circuitos seqüências dinâmicas.

O Latch

O elemento básico de memória, lacth está representado na figura

A.9.1 a). Ele consiste em dois inversores lógicos, G1 e G2, conectados

em malhas fechada. Os inversores forma uma malha de realimentação

positiva.

Figura A.9.1 a) Latch básico. b) O latch com a malha de realimentação

aberta. c)Determinação do ponto de operação do latch.

Princípio de funcionamento

Para entender o funcionamento do latch, vamos abrir a malha de

realimentação do inversor G1 (por, exemplo) e aplicar um voltagem vW

que varia de 0 V até uma tensão maior que VOH; como indicado na

figura A.9.1 b). A característica de transferência dos dois inversores

está mostrada figura A.9.1 c). Observe que essa característica consiste

em três segmentos, com o segmento do meio correspondendo à região

de transição dos inversores.

É mostrada também na figura uma reta com inclinação 1. Essa

reta representa a relação entrada igual a saída (vW = vZ), que é obtida

quando conectamos os pontos W e Z.

Como pode ser observado na figura, a linha reta intercepta a curva

de transferência em três pontos, A, B e C. É deixado por aluno mostrar

que, enquanto os pontos A e C são estáveis, no sentido em que o

circuito permanece em um deles indefinidamente, o ponto B é um ponto

de operação instável; o latch não pode permanecer por um período

significativo.

Portanto o latch é um circuito biestável que possui duas saídas

complementares. O estado estável no qual o latch opera depende da

excitação externa que o força para um estado particular. O latch então

memoriza essa ação externa, permanecendo indefinidamente no estado

a que foi levado. Como elemento de memória, o latch é capaz de

armazenar um bit de informação. Finalmente, deve ser óbvio que o

circuito latch descrito é do tipo estático.

Analisaremos a seguir, o mecanismo pelo qual o latch pode ser

disparado, para mudar de estado. O latch, junto com o circuito de

disparo, forma um flip-flop.

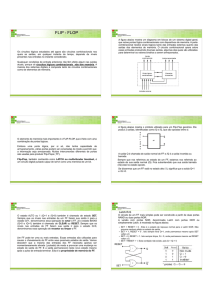

O flip-flop

O tipo mais simples de flip-flop é o set/reset (RS ou SR),

mostrado na figura A.9.2 a). É formado por duas portas NOU (ou NOR)

interligadas por conexões cruzadas entre entradas e saídas e, portanto,

incorpora um latch. A segunda entrada de cada porta NOU é usada para

entradas de disparos do flip-flop. Essas duas entradas são denominadas

S (para set) e R (para reset). As saídas são chamadas Q e Q ,

enfatizando o fato de que elas são complementares. Considera-se o flipflop no estado de set (isto é, armazenando um 1 lógico) quando Q é alta

e Q é baixa. Quando o flip-flop está no outro estado (Q baixa e Q alta),

ele é considerado em reset (armazenando um 0 lógico).

Figura A.9.2 O flip-flop tipo set/reset (SR) e sua tabela verdade.

Q

A operação do flip-flop está resumida pela tabela verdade na

figura A.9.2 b), na qual Qn representa o valor de Q no instante tn antes

da aplicação dos sinais R e S, e Qn+1 representa o valor de Q no

instantes tn+1 após a aplicação dos sinais de entrada.

Operação do flip-flop

Consideraremos o caso em que o flip-flop está memorizando o 0

lógico. Uma vez que Q será baixa, as duas entradas da porta NOU P2

serão baixas. Sua saída então será alta. Esse nível alto é aplicado a

entrada de P1, fazendo com que a saída Q seja baixa, satisfazendo a

condição inicial. Para o estado set do flip-flop, elevamos a entrada S

para o nível lógico 1, enquanto mantemos R em 0. O 1 no terminal A

forçará a saída de P2, Q , para 0. portanto, as duas entradas de P1 serão

0 e sua saída Q será 1. No entanto, mesmo que S volte para 0, o flip-flop

permanecerá no último estado adquirido, set. Obviamente, se elevarmos

S para 1 novamente (com R permanecendo em 0), não haverá

modificação. Para o estado de reset do flip-flop, precisamos elevar R

para 1, enquanto mantemos S = 0. Podemos mostrar de imediato que

isso força o flip-flop ao estado de reset e o flip-flop permanecerá nesse

estado, mesmo depois de R retornar a 0. Devemos observar que o sinal

de disparo simplesmente dá início à ação regenerativa da malha de

realimentação do lacth.

Finalmente deixamos como exercício para o aluno mostrar que as

saída do flip-flop ficam indeterminada, caso as duas entradas forem

elevadas para o nível lógico 1.

Em vez de utilizarmos duas porta NOU, podemos implementar

também um flip-flop SR pela conexão de duas porta NE(ou NAND)

interligadas por conexões cruzadas, em que as funções set e reset

estarão ativas quando em nível baixo e as entradas serão, dessa forma,

chamadas de S e R .

Implementação de flip-flop tipo SR em CMOS

O flip-flop da figura A.9.2 pode ser diretamente implementado em

CMOS simplesmente substituindo cada uma das portas NOU por seu

correspondente circuito CMOS já visto. Deixamos como exercício para

o aluno esboçar o circuito resultante. Embora o circuito assim obtido

funcione muito bem, ele é relativamente complexo. Como alternativa,

consideraremos o circuito simplificado que, além do mais, implementa

uma lógica adicional. Especificamente, a figura A.9.3 mostra outra

versão de flip-flop SR controlada por um sinal de relógio. Visto que as

entradas de relógio formam funções E com as entradas set e reset, o

flip-flop pode ser setado e resetado quando o sinal de relógio φ estiver

em nível alto. Observe que, embora os inversores ligados de forma

cruzadas no núcleo do flip-flop sejam do tipo CMOS complementar,

somente os transistores NMOS realizam as funções de ativar o setreset. Todavia, uma vez que não há um caminho entre VDD e terra

(exceto durante o chaveamento), o circuito não dissipa nenhuma

potência estática.

Figura A.9.3 Implementação CMOS de um flip-flop SR com sinal de

relógio. O sinal de relógio está indicado por φ.

Operação do flip-flop SR dinâmico

Considere inicialmente quando o flip-flop está no estado reset (Q

= 0, Q = 1, isto é, vQ = 0 e vQ = VDD) e desejamos passá-los para o

estado set. Para tanto, aplicaremos um nível alto na entrada S, enquanto

R é mantido em nível baixo. Então, quando o relógio φ for para o nível

alto, tanto Q5 como Q6 conduzirão e farão a tensão vQ abaixar. Se vQ

cair abaixo da tensão de transição do inversor formado por (Q3 e Q4)

sua saída mudará de estado (ou pelo menos começará a mudar de

estado) e a tensão vQ subirá. Esse aumento de vQ será realimentado para

entrada do inversor formado por Q1 e Q2, fazendo com que vQ por sua

vez, tenha sua tensão de saída diminuída até chegar em 0 V. Esse

processo de realimentação positiva é característica do latch.

Duas hipóteses foram admitidas na análise acima do flip-flop

dinâmico:

1. Os transistores Q5 e Q6 fornecem corrente suficiente para abaixar

a tensão no nó Q ao menos levemente abaixo da tensão de

transição do inversor Q3 e Q4. Isso é essencial para que o processo

iniciar regenerativo. Sem essa excitação inicial o flip-flop não

chaveará.

2. O sinal set deve permanecer em nível alto por um intervalo de

tempo suficiente longo para fazer com que o processo

regenerativo aconteça durante o chaveamento. Uma estimativa

para largura mínima necessária para o pulso set pode ser obtida

somando o intervalo em que vQ é reduzido de VDD para VDD/2 com

o intervalo para que a tensão vQ passe de 0 a VDD/2.

Finalmente, dado a simetria do circuito, todas essa observações se

aplicam ao processo reset.

Exemplo:

O flip-flop SR CMOS mostrado na figura A.9.3 é fabricado em

uma tecnologia para qual µnCox = 50 µA/V2, µpCox = 20, VTn0 = - VTp0 =

VT0 = 1,0 V e VDD = 5 V. Os inversores têm (W/L)n = 4 µm/2 µm e

(W/L)p = 10 µm/2 µm. os quatro transistores NMOS no circuito set/reset

têm razões (W/L) idênticas. Determine o valor mínimo necessário para

essa razão garantir que o flip-flop chaveará.

Solução:

A figura A.9.4 mostra a parte relevante do circuito flip-flop para

análise neste exemplo. Observe que o processo de regeneração ainda

não começou e supõe-se que vQ = 0 e, portanto, Q2 estará conduzindo.

Dessa forma, o circuito se comporta como uma porta psedo-NMOS e

nossa tarefa é escolher as razões (W/L) para Q5 e Q6, tal que o valor de

VOL desse inversor seja menor que VDD/2 (isto é, a transição do inversor

formado por Q3 e Q4 (que são casados).

Para encontramos o valor mínimo necessário de (W/L)

utilizaremos dois caminhos. No primeiro igualamos as correntes que

passam por Q2 , Q5 e Q6 na situação onde vQ = VDD/2 e que podemos

supor que os transistores Q5 e Q6 podem ser substituído por um

transistor de (W/L)equiv. (associação em série) igual à metade da razão de

(W/L)5 e (W/L)6. Assim, verificando que os transistores Q5 e Q6 estão

operando na região de triodo, temos

1

1

2

W

W

k n' 1 (VGS − VTn )VDS − (VDS ) 2 = k p' (VSG − | VTp |)VSD − (VSD )

2

2

L Q 5 2

L Q 2

1

1

2

W

10

50 1 (5 − 1)5 / 2 − (5 / 2) 2 = 20 (5 − 1)5 / 2 − (5 / 2 )

2

2

L Q5 2

2 Q 2

W

10

50 1 = 20

L Q5 2

2 Q 2

W

=4

L Q 5

e

logo,

W

=4

L Q 6

Figura A.9.4 Parte importante do circuito do flip-flop para determinar

as razões mínimas (W/L) de Q5 e Q6 para garantir o chaveamento.

A segunda maneira de determinarmos a razão mínima de (W/L)Q5

e (W/L)Q6 é admitindo que a metade da tensão de saída vQ = VDD/2

ficará sobre cada um dos transistores e, como para esta situação o

transistore que fica sujeito a menor tensão VGS é o transistor Q6 , então

faremos a corrente que passa por este transistor igual a corrente que

passa por Q2, portanto

1

1

2

W

W

k n' (VGS − VTn )VDS − (VDS ) 2 = k p' (VSG − | VTp |)VSD − (VSD )

2

2

L Q 6

L Q 2

1

1

2

W

10

50 (5 − 5 / 4 − 1)5 / 4 − (5 / 4) 2 = 20 (5 − 1)5 / 2 − (5 / 2)

2

2

L Q 6

2 Q 2

W 85 200 55

50 =

L Q 6 32 2 Q 2 8

W

≅ 5.2

L Q 6

e

logo,

W

≅ 5.2

L Q 5

Um valor muito próximo do resultado anterior. Lembrando que este é

um valor mínimo absoluto, poderíamos, na prática escolher uma razão

6 ou 7.

Exercício:

Repita o exemplo anterior para determinar o valor mínimo

necessário de (W/L)Q5 = (W/L)Q6 tal que o chaveamento ocorra quando

as entradas S e φ estiverem em VDD/2.

Resposta : 24,4.

Implementação mais simples de flip-flop SR dinâmico

Uma implementação mais simples para uma flip-flop SR

controlado por relógio é mostrada na figura A.9.5. Nesse caso, a lógica

de transistores de passagem é empregada para implementar as funções

set-reset por relógio.

Esse circuito é comum como célula básica de memória estática de

acesso randômico (static random-access memory – SRAM).

Figura A.9.5 Uma implementação CMOS mais simples de um flip-flop

SR controlado por relógio.

Circuitos flip-flop tipo D

Existem vários tipos de flip-flop. Muitos podem ser sintetizados

em termos de portas lógicas. As portas lógicas depois podem ser

substituídas pela implementação CMOS de seus circuitos. Essa

abordagem simples quase sempre leva para uma implementação mais

complexa. Em muitos casos, circuitos mais simples podem ser

projetados em vez do projeto a partir de portas lógicas. Para ilustrar

isso, apresentaremos o projeto de um circuito de um flip-flop de dados

ou tipo D.

O flip-flop tipo D é apresentado em forma de diagrama de blocos

na figura A.9.6. Este tem duas entradas, a entrada de dados D e a

entrada do relógio φ. As saídas complementares Q e Q . Quando a

entrada do relógio for baixa, o flip-flop está no estado de memória ou

repouso; a mudança no sinal de dados não tem nenhum efeito nas

saídas do flip-flop. Quando o relógio vai para o nível alto, o flip-flop

adquire o nível lógico presente em D logo na subida da borda do pulso

de relógio. Diz-se que esse flip-flop é disparado pela borda (edgetriggered). Algumas implementações do flip-flop tipo D incluem

também as entradas de set e reset que se impõem sobre a operação com

o relógio que acabamos de descrever.

Figura A.9.6 Representação na forma de diagrama de blocos de um flipflop tipo D

Uma simples implementação de um flip-flop tipo D é apresentada

na figura A.9.7. O circuito consiste em dois inversores conectados em

uma malha de realimentação positiva como se fosse um latch estático

semelhante àquele mostrado na figura A.9.1, exceto que aqui a malha

de realimentação fica fechada por apenas uma parte do tempo.

Especificamente, a malha de realimentação estará fechada quando o

sinal de relógio estiver em nível baixo (φ =0, φ = 1 ). A entrada D está

conectada no flip-flop por meio de uma chave que fecha quando o sinal

de relógio está em nível alto. O princípio de funcionamento é direto:

quando φ =1, a malha de realimentação estará aberta e a entrada D

estará conectada na entrada do inversor P1. A capacitância de entrada

do nó P1 será carregada com o mesmo valor de D e a capacitância no de

entrada P2 será carregada com o valor de D . Então, quando o sinal de

relógio passar a nível baixo, a linha de entrada ficará isolada do flipflop, a malha de realimentação passa a ficar fechada e o latch adquire o

valor de D assim que φ vai para nível baixo, fornecendo uma saída Q =

D.

Este circuito combina a técnica de realimentação positiva presente

em circuitos biestáveis estáticos com a técnica de armazenamento de

cargas de circuitos dinâmicos.

Finalmente, é importante observar que para uma operação

apropriada deste e de muitos outros circuitos que empregam sinais de

relógio é necessário que φ e φ não devem estar simultaneamente em

nível alto em nenhum instante. Essa condição é definida em relação as

duas fases de relógio como fases não sobrepostas (nonoverlapping).

Figura A.9.7 Uma simples implementação de um flip-flop tipo D. a)

emprega um sinal de relógio com duas fases não superpostas mostradas

em b).

Observando mais atentamente o circuito da figura A.9.7 notamos

que, durante o intervalo de tempo em que φ está em nível alto, a saída

do flip-flop segue o mesmo sinal da linha de entrada D. Isso pode

ocasionar problemas em determinadas situações de projetos lógico. O

problema pode ser resolvido de forma efetiva utilizando a configuração

mestre-escravo (master-slave) mostrada na figura A.9.8.

O circuito mestre-escravo consiste em um par de circuitos do tipo

mostrado na figura A.9.7, controlado por fases de relógio alternadas.

Aqui, para enfatizar que as duas fases de relógio não devem apresentar

sobreposição, vamos representá-las por φ1 e φ2, conforme mostrado na

figura A.9.7 b). A operação do circuito é a seguinte:

1. Quando φ1 está em nível alto e φ2 está em nível baixo, a entrada

está conectada ao latch-mestre cuja malha de realimentação está

aberta, enquanto o latch escravo está isolado. Portanto, a saída Q

permanece no valor previamente armazenado no latch escravo

cuja malha de realimentação está agora fechada. As capacitâncias

nodais do latch mestre são carregadas com as tensões apropriadas

correspondentes ao valor presente de D.

2. Quando φ1 vai para nível baixo, o latch-mestre está isolado da

linha de dados da entrada. Então, quando φ2 vai para o nível alto,

a malha de realimentação do latch-mestre passa a estar fechada e

o valor de D fica constante e armazenado. Além disso, sua saída

está conectada ao latch escravo cuja malha de realimentação está

agora

aberta.

As

capacitâncias

nodais

no

escravo

são

apropriadamente carregadas tal que, quando φ1 vai para nível alto

novamente, o latch escravo trava em um novo valor de D e

fornece-o na saída, Q = D.

A partir dessa descrição, notamos que, na transição positiva do sinal

de relógio φ2, a saída Q adota o valor de D que havia na linha D no

fim da fase de relógio anterior, φ1. Esse valor de saída permanece

constante por um período de relógio. Finalmente, note que, durante o

intervalo sem sobreposição em nível baixo, ambos os latches têm

suas malhas de realimentação abertas e teremos as capacitâncias

nodais mantendo a maior parte da sua carga. Nesse caso, o intervalo

sem sobreposição deve ser feito o mais curto possível (da ordem de

1ns ou menos na prática).

Figura A.9.8 a) Um flip-flop D mestre-escravo. b) Formas de onda do

relógio não superpostas.