ANÁLISE DE TOPOLOGIAS DE ESPELHOS DE CORRENTE COM

TECNOLOGIA CMOS de 130nm(1)

Matheus Cortez(2), Paulo César C. de Aguirre (3), Alessandro G. Girardi (4)

(1) Trabalho

executado com recursos do Edital FAPERGS 2014 - PROBITI, da Pró-Reitoria de Pesquisa

Estudante, Bolsista, Universidade Federal do Pampa - UNIPAMPA; Alegrete, Rio Grande

[email protected].

(3) Co-orientador; Universidade Federal do Pampa.

(4) Orientador; Universidade Federal do Pampa.

(2)

do

Sul;

RESUMO: Os espelhos de corrente são circuitos muito utilizados para polarização em amplificadores operacionais e como

carga ativa devido à sua alta impedância de saída. Assim, esse trabalho se baseia na obtenção dos seguintes parâmetros

de algumas topologias de espelhos de corrente: condutância de saída (𝑔𝑜𝑢𝑡 ), tensão mínima de saída (𝑉𝑜𝑢𝑡 𝑚𝑖𝑛 ), área de

silício e erro da corrente de cópia devido a variações na tensão de saída. Isto permitiu a criação de um banco de dados

utilizando uma tecnologia de fabricação CMOS de 130nm.

Palavras-Chave: espelhos de corrente, corrente de cópia, corrente de referência, tecnologia 130nm.

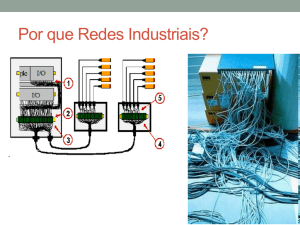

INTRODUÇÃO

Os espelhos de corrente usando dispositivos ativos são vantajosos devido à sua facilidade de

integração e uso em circuitos integrados analógicos. Eles podem ser utilizados como elementos de

polarização em dispositivos de carga ativa para amplificadores substituindo resistências, devido à sua

pequena área de silício utilizada para fornecerem corrente de polarização (GRAY et al., 2009).

Dessa forma, a obtenção dos parâmetros e análise das variações no comportamento das topologias de

espelho de corrente visam a criação de um banco de dados com informações das suas características

elétricas para guiar o projetista na escolha da topologia mais adequada para sua aplicação.

METODOLOGIA

Os espelhos de corrente utilizam o princípio de que, se os potenciais 𝑉𝑔𝑠 de dois transistores MOS

idênticos são iguais, as correntes de dreno 𝐼𝑑 devem ser iguais para um dado potencial, 𝑉𝑑𝑠 , também igual.

Assume-se que a corrente de referência 𝐼𝑟𝑒𝑓 é fixa e definida por uma fonte de corrente ou por outro circuito

externo e a corrente de cópia é a saída ou corrente "espelhada". (ALLEN; HOLBERG, 2002)

A partir disso pode-se definir que se todos os transistores operarem na região de saturação esse circuito

irá atuar como um espelho de corrente. Sua corrente de cópia, devido à igualdade dos transistores e tensões

de polarizações, irá depender apenas das características físicas construtivas desses transistores.

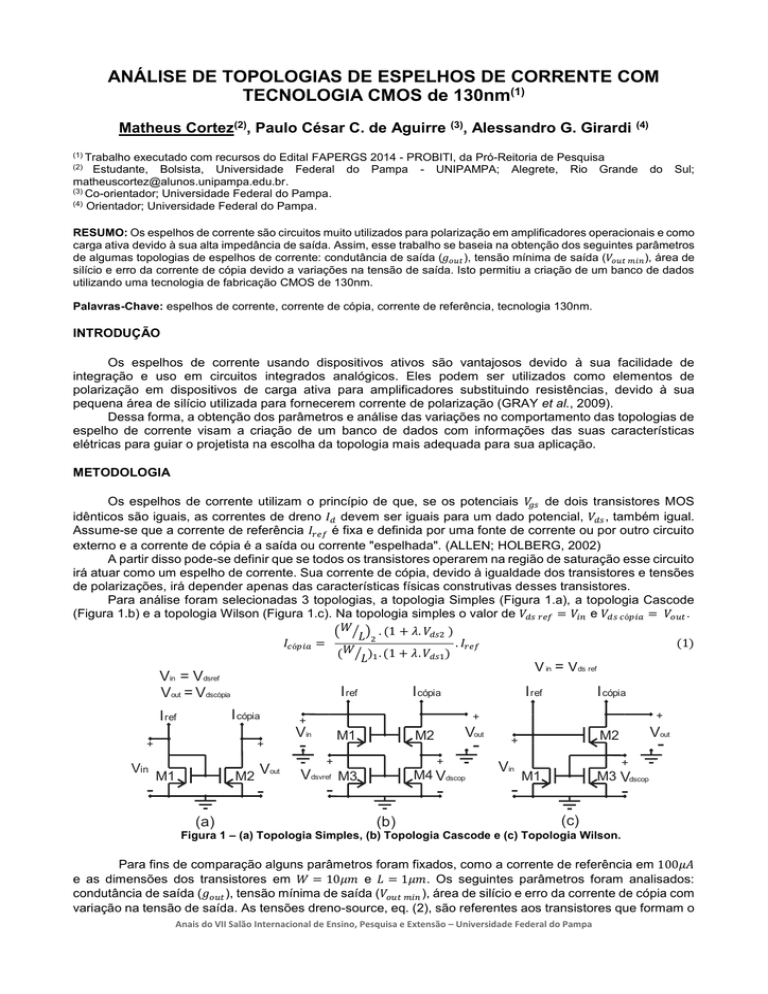

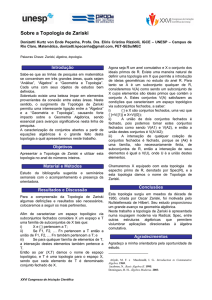

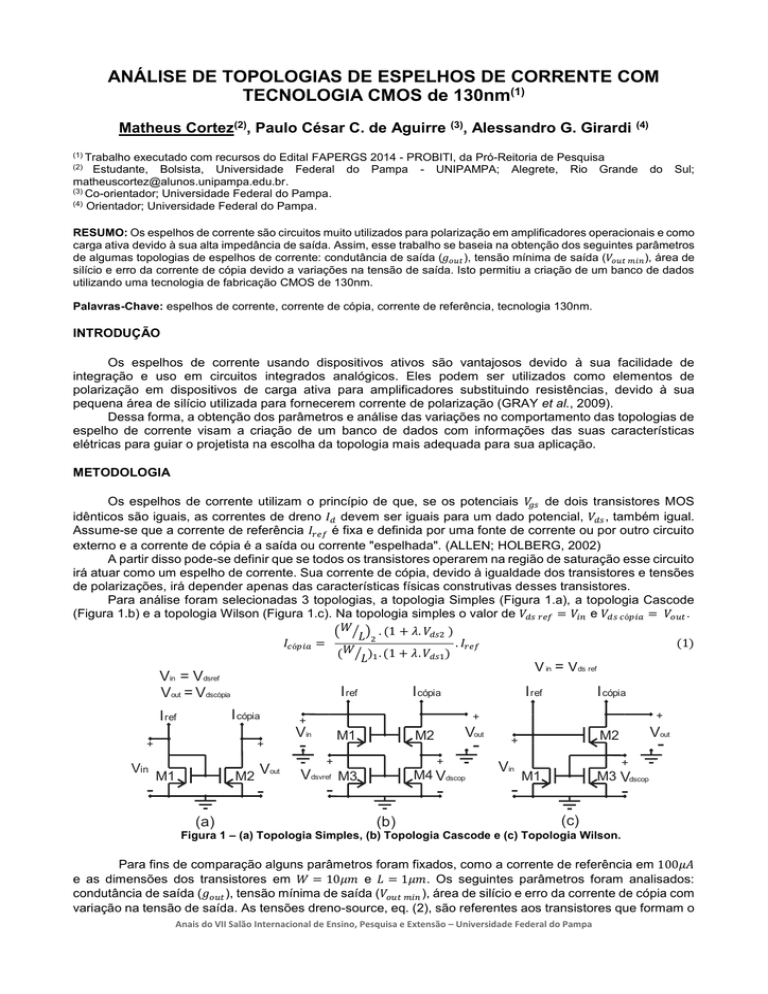

Para análise foram selecionadas 3 topologias, a topologia Simples (Figura 1.a), a topologia Cascode

(Figura 1.b) e a topologia Wilson (Figura 1.c). Na topologia simples o valor de 𝑉𝑑𝑠 𝑟𝑒𝑓 = 𝑉𝑖𝑛 e 𝑉𝑑𝑠 𝑐ó𝑝𝑖𝑎 = 𝑉𝑜𝑢𝑡 .

(𝑊⁄𝐿) . (1 + 𝜆. 𝑉𝑑𝑠2 )

2

𝐼𝑐ó𝑝𝑖𝑎 =

. 𝐼𝑟𝑒𝑓

(1)

(𝑊⁄𝐿)1 . (1 + 𝜆. 𝑉𝑑𝑠1 )

V in = Vds ref

Vin = Vdsref

Vout = Vdscópia

I ref

I cópia

I ref

Vin

-

+

M1

M2

Vout

(a)

I ref

I cópia

+

+

+

Vin

+

I cópia

M1

-

Vout

M2

-

+

+

Vdsvref M3

M4 Vdscop

-

-

(b)

Vin

-

Vout

M2

+

-

+

M1

M3 Vdscop

-

(c)

Figura 1 – (a) Topologia Simples, (b) Topologia Cascode e (c) Topologia Wilson.

Para fins de comparação alguns parâmetros foram fixados, como a corrente de referência em 100𝜇𝐴

e as dimensões dos transistores em 𝑊 = 10𝜇𝑚 e 𝐿 = 1𝜇𝑚. Os seguintes parâmetros foram analisados:

condutância de saída (𝑔𝑜𝑢𝑡 ), tensão mínima de saída (𝑉𝑜𝑢𝑡 𝑚𝑖𝑛 ), área de silício e erro da corrente de cópia com

variação na tensão de saída. As tensões dreno-source, eq. (2), são referentes aos transistores que formam o

Anais do VII Salão Internacional de Ensino, Pesquisa e Extensão – Universidade Federal do Pampa

espelho de corrente. A tensão de Early, 𝑉𝑎 , é um parâmetro relacionado à inclinação da região de saturação

do transistor e varia conforme a tecnologia utilizada e com o comprimento de canal do transistor 𝐿.

𝑉𝑑𝑠 𝑐ó𝑝𝑖𝑎 − 𝑉𝑑𝑠 𝑟𝑒𝑓

𝜖=

(2)

𝑉𝑎

RESULTADOS E DISCUSSÃO

As características elétricas das topologias analisadas foram extraídas através de simulação:

simulação de esquemático, leiaute e extração de elementos parasitas e simulação com inserção dos

elementos parasitas. A área encontrada para cada circuito está associada à área do leiaute otimizada, levando

em consideração a redução da área de silício.

As curvas apresentadas na Figura 2 mostram o comportamento da corrente de cópia à uma variação

na tensão 𝑉𝑜𝑢𝑡 e com isso foi possível extrair os resultados apresentados na tabela 1. O 𝑉𝑜𝑢𝑡 𝑚𝑖𝑛 é a tensão

mínima para que o circuito se comporte como espelho de corrente e a condutância é a derivada da curva na

região de saturação, para isso foram escolhidos 2 pontos quaisquer na região de saturação e calculado

através da eq. (3)

𝐼𝑐ó𝑝𝑖𝑎 𝑝𝑜𝑛𝑡𝑜 1 − 𝐼𝑐ó𝑝𝑖𝑎 𝑝𝑜𝑛𝑡𝑜 2

𝐺𝑜𝑢𝑡 =

(3)

𝑉𝑜𝑢𝑡 𝑝𝑜𝑛𝑡𝑜 1 − 𝑉𝑜𝑢𝑡 𝑝𝑜𝑛𝑡𝑜 2

Os resultados dos erros mostram que apesar de apresentar um baixo 𝑉𝑜𝑢𝑡 𝑚𝑖𝑛 a topologia simples de

espelho de corrente possui uma resistência muito baixa, tendo assim uma inclinação da região de saturação

e a dependência da tensão de saída muito alta. O circuito menos dependente da tensão de saída é a topologia

cascode devido à inserção de transistores para acréscimo de resistência. Na topologia Wilson clássica é

observado um erro de cópia de corrente devido a propria topologia cujo valor é proporcional a tensão vgs2 e

inversamente proporcional a tensão de Early.

Figura 2 – Comportamento 𝑰𝒄ó𝒑𝒊𝒂 𝒙 𝑽𝒅𝒔𝟐 .

Topologia

Simples

Cascode

Wilson

𝑔𝑜𝑢𝑡

28,6458𝜇𝑠

0,9803𝜇𝑠

1,1833𝜇𝑠

Tabela 1 – Parâmetros das topologias

Erro (𝑉𝑑𝑠 𝑐𝑜𝑝 + 10𝑚𝑉)

𝑉𝑜𝑢𝑡 𝑚𝑖𝑛

Área do leiaute

384,2𝑚𝑉

0,12%

56,41𝜇𝑚²

825,8𝑚𝑉

0,0049%

149,33𝜇𝑚²

787,5𝑚𝑉

88,26𝜇𝑚²

5,2577&

Erro (𝑉𝑑𝑠 𝑐𝑜𝑝 − 10𝑚𝑉)

0,12%

0,0037%

5,2675%

Fonte: Elaborado pelo autor

CONCLUSÕES

Os resultados aqui obtidos são adequados para que se possa simplificar a análises de grandes

circuitos onde existam estágios de carga ativa ou polarização com espelhos de corrente.

As topologias demonstram características diferentes e cada uma possui vantagens e desvantagens.

Não se pode concluir qual topologia é melhor, pois depende das características dos circuitos onde esse

estágio será empregado, ou seja, depende da oferta de área de silício, o valor da alimentação do circuito e

se o circuito precisa de uma precisão maior na corrente de cópia.

Por fim, como projeto futuro esse banco de dados deverá ser exposto para uso do grupo de

pesquisa no que tange a escolha da topologia de espelho de corrente mais adequada para cada aplicação.

REFERÊNCIAS

ALLEN, Phillip E.; HOLBERG, Douglas R. CMOS Analog Circuit Design. 2.ed. New York: Oxford University press, 2002.

GRAY, Paul R.; HURST, Paul J.; LEWIS, Stephen H.; MEYER, Robert G. ANALYSIS AND DESIGN OF ANALOG

INTEGRATED CIRCUITS. 5.ed. Hoboken: JohnWiley & Sons, 2009.

Anais do VII Salão Internacional de Ensino, Pesquisa e Extensão – Universidade Federal do Pampa