Universidade Estácio de Sá – Curso de Informática

Disciplina de Organização de Computadores II

Prof. Gabriel P. Silva - 1o Sem. / 2005

2ª Lista de Exercícios

1) O que é o relógio de um sistema digital?

É um sinal elétrico periódico que é utilizado para cadenciar todas as operações

realizadas pelo processador.

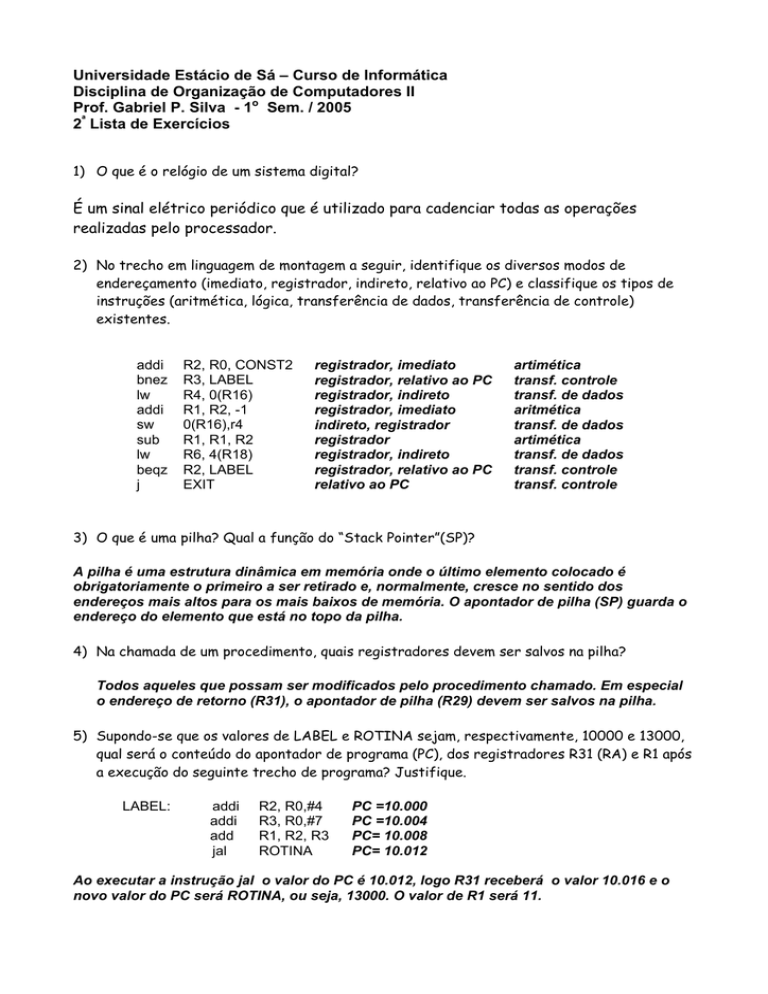

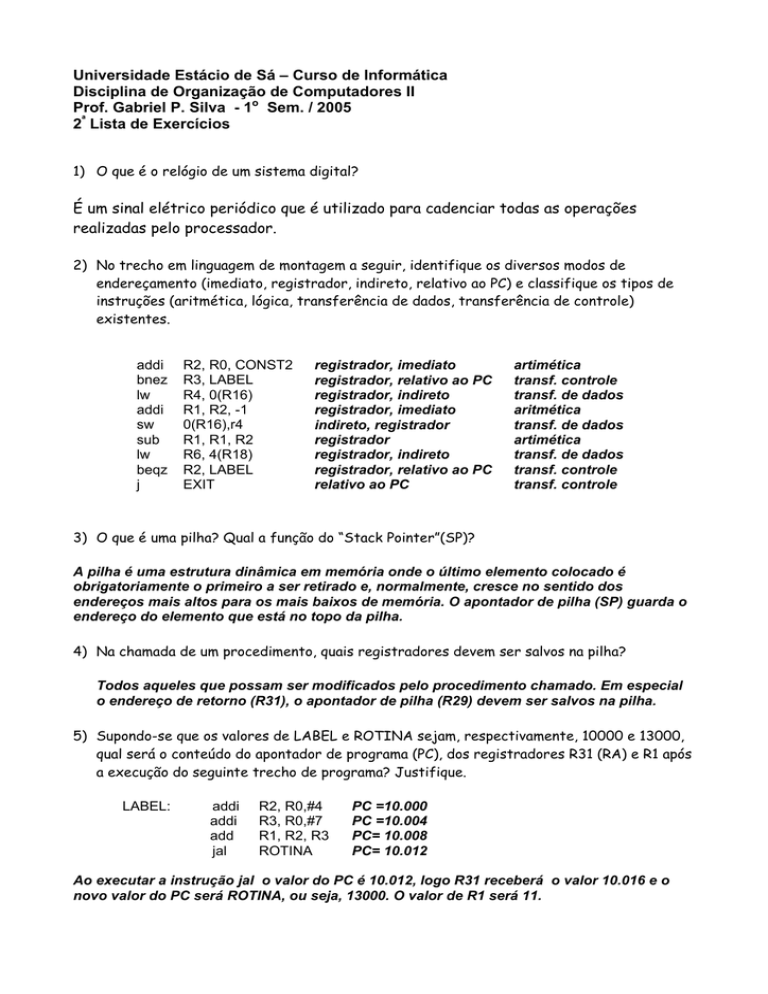

2) No trecho em linguagem de montagem a seguir, identifique os diversos modos de

endereçamento (imediato, registrador, indireto, relativo ao PC) e classifique os tipos de

instruções (aritmética, lógica, transferência de dados, transferência de controle)

existentes.

addi

bnez

lw

addi

sw

sub

lw

beqz

j

R2, R0, CONST2

R3, LABEL

R4, 0(R16)

R1, R2, -1

0(R16),r4

R1, R1, R2

R6, 4(R18)

R2, LABEL

EXIT

registrador, imediato

registrador, relativo ao PC

registrador, indireto

registrador, imediato

indireto, registrador

registrador

registrador, indireto

registrador, relativo ao PC

relativo ao PC

artimética

transf. controle

transf. de dados

aritmética

transf. de dados

artimética

transf. de dados

transf. controle

transf. controle

3) O que é uma pilha? Qual a função do “Stack Pointer”(SP)?

A pilha é uma estrutura dinâmica em memória onde o último elemento colocado é

obrigatoriamente o primeiro a ser retirado e, normalmente, cresce no sentido dos

endereços mais altos para os mais baixos de memória. O apontador de pilha (SP) guarda o

endereço do elemento que está no topo da pilha.

4) Na chamada de um procedimento, quais registradores devem ser salvos na pilha?

Todos aqueles que possam ser modificados pelo procedimento chamado. Em especial

o endereço de retorno (R31), o apontador de pilha (R29) devem ser salvos na pilha.

5) Supondo-se que os valores de LABEL e ROTINA sejam, respectivamente, 10000 e 13000,

qual será o conteúdo do apontador de programa (PC), dos registradores R31 (RA) e R1 após

a execução do seguinte trecho de programa? Justifique.

LABEL:

addi

addi

add

jal

R2, R0,#4

R3, R0,#7

R1, R2, R3

ROTINA

PC =10.000

PC =10.004

PC= 10.008

PC= 10.012

Ao executar a instrução jal o valor do PC é 10.012, logo R31 receberá o valor 10.016 e o

novo valor do PC será ROTINA, ou seja, 13000. O valor de R1 será 11.

6) Enumere e descreva suscintamente os tipos de conflitos que podem ocorrer em um pipeline

de instruções de um processador.

Conflito Estruturais – Quando um recurso é utilizado por dois ou mais estágios do pipeline.

Conflito por Dados – Quando uma instrução depende de um resultado (registrador) que vai

ser produzido por uma instrução anterior que ainda está no pipeline.

Conflitos de Controle - Quando uma instrução de desvio condicional é executada, podem

ser buscadas instruções para o pipeline que posteriormente serão anuladas, dependendo

do resultado do desvio.

7) O uso de caches separadas para dados e instruções permite resolver que tipo de conflito

no pipeline?

Resolve o conflito estrutural, que ocorre quando o estágio de Busca e o de Memória

precisam fazer acesso simultâneo à memória.

8) Além do uso do desvio atrasado, que outros mecanismos são utilizados para resolver o

conflito de controle no pipeline?

O uso de mecanismos de predição estática e/ou dinâmica de desvio.

9) No trecho a seguir, identifique as instruções que possuem dependência direta de dados:

I1 Î I2 (R1)

I2 Î I4 (R2)

I3 Î I5 (R3)

10) Qual a característica em comum entre as arquiteturas VLIW e superescalares dos

modernos processadores?

A busca, decodificação e execução de múltiplas instruções por ciclo.

11) Quais as principais diferenças entre as arquiteturas do tipo RISC e CISC?

As arquiteturas CISC possuem instruções complexas, com diversos modos de

endereçamento, com formatos diversos e tempo de execução variável. Vários tipos de

instruções podem referenciar operandos na memória.

As arquiteturas RISC possuem instruções mais simples, com poucos modos de

endereçamento, com poucos formatos e com tempo de execução determinado. Apenas as

instruções de “load” e “store” podem referenciar operandos na memória.

12) Relacione as principais características das arquiteturas SMT.

As arquiteturas SMT (multithreading simultâneo) buscam obter um maior desempenho

despachando instruções de multiplos fluxos de instruções (threads) para as diversas

unidades funcionais de um processador superescalar. A cada instante de tempo,

instruções de diferentes “threads” podem estar sendo executadas nos diversos estágios

do pipeline.

13) O que é um processador “superpipelined”?

É aquele com um elevado número de estágios no pipeline, praticamente todos os

modernos processadores superescalares são superpipelined.

14) Durante o projeto de um processador, verifica-se que os tempos de execução dos

estágios de um pipeline são os seguintes:

a.

b.

c.

d.

e.

busca da instrução: 2 ns

decodificação/leitura dos registradores: 3 ns

execução/cálculo do endereço: 2,5 ns

acesso à memória: 4 ns

escrita do resultado: 3,5 ns

Qual será o tempo de ciclo do relógio que deverá ter este processador? Justifique.

4 ns. Porque é o estágio com maior latência que determina a duração do período do ciclo

do relógio do processador.

15) O código a seguir é executado em um processador com um pipeline de 5 estágios, sem

adiantamento de dados, como definido na questão anterior:

add

lw

sub

R5, R6, R7

R6, 100(R7)

R7, R6, R8

Considerando que um ciclo de relógio é o tempo gasto para acesso à memória principal,

quantos ciclos serão gastos para executar este trecho de código? Justifique.

1

2

3

4

5

6

7

8

9

B

add

lw

sub

-

D

E

M

W

add

lw

sub

sub

sub

-

add

lw

sub

-

add

lw

sub

-

add

lw

sub

Resposta: 9 ciclos.

16) Considere a execução do seguinte trecho de código, em um processador com o mesmo

pipeline descrito na questão acima:

add

sub

add

addi

sub

R1,

R4,

R7,

R10,

R13,

R2,

R5,

R8,

R11,

R14,

R3

R6

R9

#12

R15

M

E

D

B

Se a primeira instrução está sendo buscada no primeiro ciclo, no quarto ciclo de execução,

quais os registradores que estarão sendo lidos? Quais estarão sendo escritos?

No quarto ciclo de execução, deve-se determinar quais as instruções que estão nos

estágios de decodificação e escrita. Os registradores que estarão sendo lidos são os

registradores fontes da instrução, no caso, r8 e r9. Com onão ná nenhuma instrução no

estágio de escrita, nenhum registrador estará sendo escrito.

17) O que é memória cache? Porque é utilizada?

É uma memória mais rápida e de menor capacidade colocada entre o processador e a

memória principal, que guarda cópia dos dados armazenados na memória principal, com a

finalidade de oferecer a ilusão de uma grande capacidade de armazenamento, mas com

uma velocidade de acesso perto da memória rápida. É utilizada porque o tempo do ciclo de

relógio dos processadores tem diminuído muito mais rapidamente que o tempo de acesso

à memória dinâmica (que compõe a memória principal).

18) O funcionamento da memória cache está baseado em que características de localidade

presentes nos programas executáveis? Descreva cada uma delas.

Localidade Temporal – as posições de memória, uma vez referenciadas, tendem a ser

novamente refrenciadas em curto espaço de tempo;

Localidade Espacial – os endereços dos acessos feitos à memória principal tendem a

ser próximos dos endereços dos acessos anteriores;

19) Quais são os três tipos principais de organização da memória cache? Cite as vantagens e

desvantagens de cada uma deles.

Cache com mapeamento direto – Um bloco na memória pode apenas ocupar uma única

posição na memória cache. A vantagem é o baixo custo e rapidez. A desvantagem é

uma menor taxa de acerto.

Cache com mapeamento totalmente associativo – Um bloco da memória principal pode

ser colocado em qualquer posição da cache. A vantagem é alta taxa de acerto. A

desvantagem é o seu alto custo e capacidade reduzida.

Cache com mapeamento associativo por conjunto – Os blocos podem ser colocados em

determinadas posições da cache denominadas de “conjuntos”. O número de

linhas/blocos por conjunto determina o grau de associatividade da cache. A sua grande

vantagem é uma alta taxa de acerto aliado a um baixo custo e rapidez. A desvantagem é

que suas taxas de acerto são um pouco menores que a cache totalmente associativa.

20) Suponha que um bloco é buscado na memória principal e pode ser colocado em duas e

apenas duas posições da memória cache. Que tipo de organização possui esta cache?

Mapeamento Associativo por Conjunto com Associatividaded e Grau 2.

21) Quais são os três algoritmos mais utilizados na substituição de blocos em uma memória

cache com associatividade? Faça uma descrição do funcionamento de cada um deles.

L.R.U – Menos recentemente utilizado, retira do conjunto o bloco cujo acesso mais

recente ocorreu há mais tempo.

F.I.F.O – (First In, First Out), o bloco que foi colocado no conjunto há mais tempo será o

primeiro a ser retirado.

Aleatório – O bloco a ser retirado do conjunto é escolhido aleatoriamente.

22) Suponha que um bloco é buscado na memória principal para uma cache com associatividade

4. Se não houver mais espaço no conjunto destinado para este bloco, qual bloco deverá ser

retirado se o algoritmo utilizado for o F.I.F.O.?

O bloco que foi colocado no conjunto há mais tempo será o primeiro a ser retirado.

23) Descreva quais são as políticas de escrita de dados de uma cache na memória principal.

Write-through – O dado é escrito no bloco da cache e a escrita é repetida

imediatamente na memória principal. O tempo médio de acesso é prejudicado, pois a

cada escrita, mesmo com acerto, o dado deve ser atualizado na memória. O controle

para esse tipo de política é mais simples.

Write-back – O dado é escrito no bloco da cache, mas o bloco só será escrito na

memória principal quando for substituído. As taxas de acerto e o tempo médio de

acesso são melhores, mas o controle é mais complexo.

24) O seguinte programa foi executado pelo processador DLX. O bloco com endereço

correspondente a variável A está válido na cache. Qual será o conteúdo da memória

principal e da memória cache correspondente a variável A após a execução deste programa

se a política de atualização for “write back”?

.data

A:

.word

.text

lw

add

sw

45

r3, A(r0)

r3, r3, #1

A(r0), r3

O conteúdo da variável A na memória principal será 45 e na memória cache será

46. Como a cache é “write-back” o dado só será atualizado na cache e ficará

desatualizado na memória principal até que o bloco seja substituído na cache.

25) Quais as vantagens da utilização de caches separadas de dados e instruções?

A política de escrita só precisa ser aplicada à cache de dados;

Podem ser utilizadas estratégias diferentes para cada cache: capacidade total, tamanho

do bloco, organização, etc.;

Permitem caminhos separados para acesso simultâneo a dados e instruções, por

exemplo, em um pipeline;

Normalmente as taxas de acerto são melhores.

26) Se a taxa de acerto de uma cache é de 98%, o tempo de acesso à cache é de 5 ns e o

tempo de acesso à memória principal é de 50 ns, qual o tempo médio de acesso à memória?

Tma = 0,98 x 5 + 0,02 x 50 = 5,9 ns

27) Considere uma memória cache de 128 Kbytes com mapeamento direto, com 16 bytes em

cada linha da cache. Se o endereço possui 32 bits, quantos bits são gastos para o rótulo e

para o índice?

17

128 Kbytes = 2 => 17 bits

Rótulo = 32 – 17 = 15 bits

4

16 bytes/bloco (2 => 4 bits)

Indice => Total de blocos da memória cache = 128 Kbytes / 16 bytes = 8 K blocos

13

4 Kblocos = 2 => Indíce = 13 bits

Rótulo

15

Índice

13

offset

4

28) A seguir apresentamos uma série de endereços referenciados em uma memória contendo

palavras de 32 bits: 1, 4, 8, 5, 20, 5, 19, 56, 9, 8 e 4. Considere uma cache mapeada

diretamente, com 16 blocos com palavras de 32 bits cada. Estando inicialmente vazia,

identifique cada referência na lista como falha ou acerto no acesso à cache e mostre o

conteúdo final da cache, após o processamento de todas essas referências.

F F F F F A F F F F F

Endereço– 1, 4, 8, 5, 20, 5, 19, 56, 9, 8, 4

INDICE

CONTEUDO

0

1

MEM[1]

2

3

MEM[19]

4

MEM[4]

5

MEM[5]

6

7

8

MEM[8]

9

MEM[9]

10

11

MEM[11]

12

13

14

15

29) Se um barramento síncrono possui largura de 32 bits e freqüência de relógio de 66 Mhz,

qual a sua taxa de transferência máxima (largura de banda)?

R: 32 bits = 4 bytes ==> B = 4B x 66 Mhz= 264 MB/s

30) Quais as diferenças entre um barramento multiplexado e um não multiplexado?

R. O barramento multiplexado compartilha as mesmas linhas para os dados e endereço. O

barramento não multiplexado possui linhas separadas para os dados e endereços.

![Aula 06 - Daves - exercicios [Modo de Compatibilidade]](http://s1.studylibpt.com/store/data/001144987_1-66893eaef68e852efe81e8f280104c23-300x300.png)