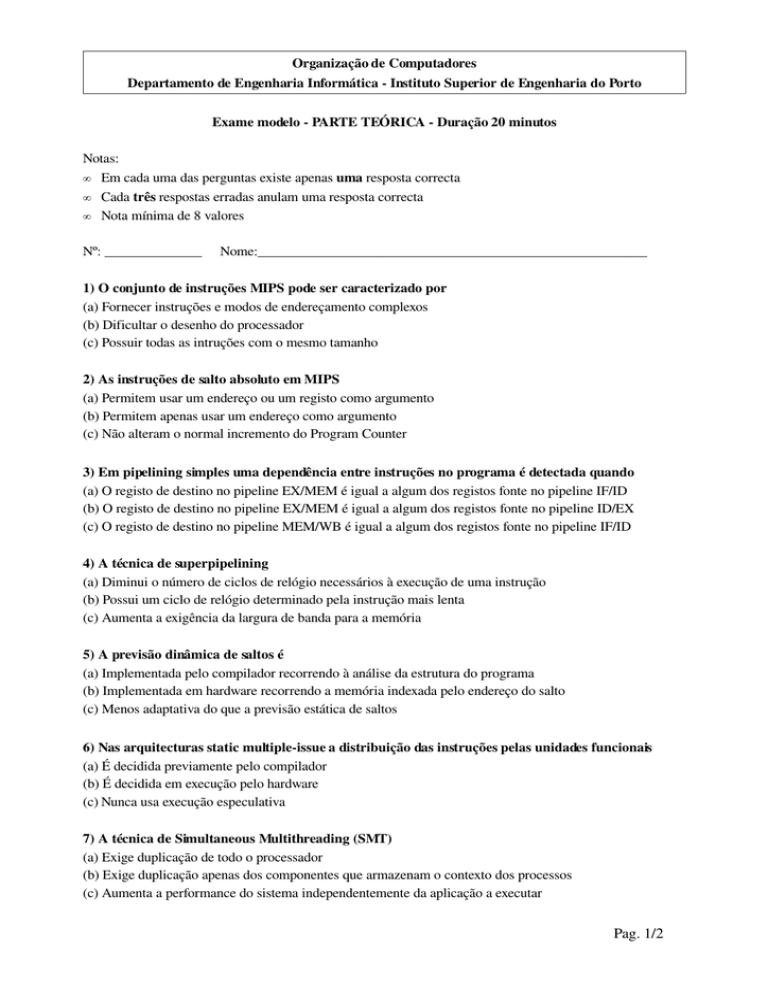

Organização de Computadores

Departamento de Engenharia Informática ­ Instituto Superior de Engenharia do Porto

Exame modelo ­ PARTE TEÓRICA ­ Duração 20 minutos

Notas:

• Em cada uma das perguntas existe apenas uma resposta correcta

• Cada três respostas erradas anulam uma resposta correcta

• Nota mínima de 8 valores

Nº: ______________ Nome:________________________________________________________

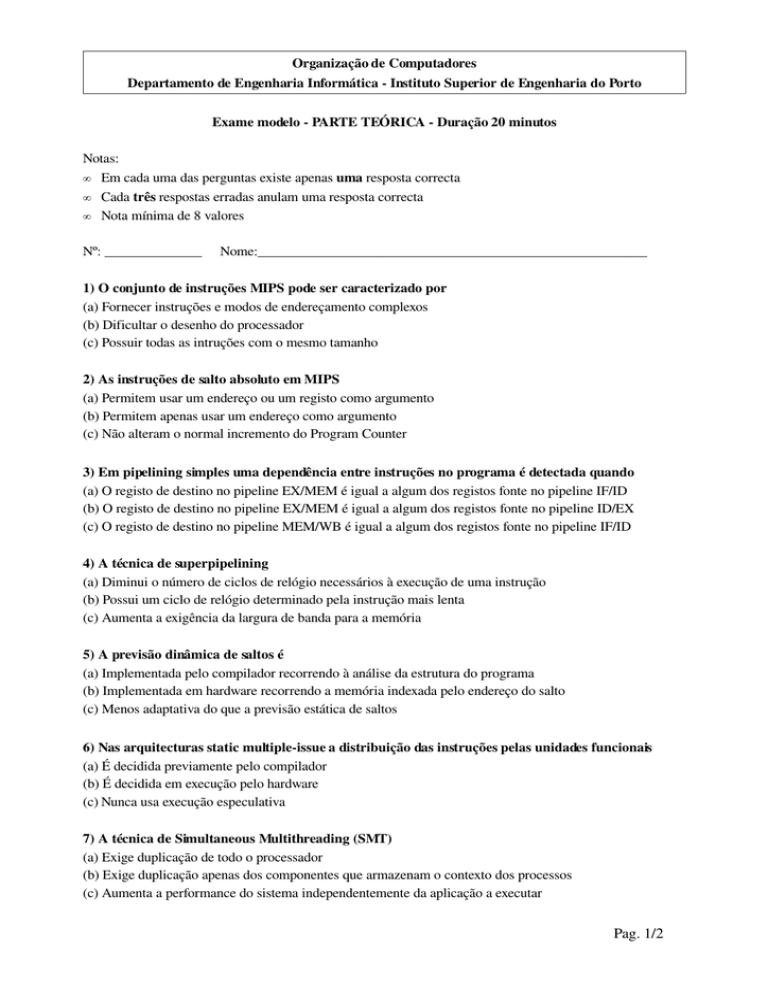

1) O conjunto de instruções MIPS pode ser caracterizado por

(a) Fornecer instruções e modos de endereçamento complexos

(b) Dificultar o desenho do processador

(c) Possuir todas as intruções com o mesmo tamanho

2) As instruções de salto absoluto em MIPS

(a) Permitem usar um endereço ou um registo como argumento

(b) Permitem apenas usar um endereço como argumento

(c) Não alteram o normal incremento do Program Counter

3) Em pipelining simples uma dependência entre instruções no programa é detectada quando

(a) O registo de destino no pipeline EX/MEM é igual a algum dos registos fonte no pipeline IF/ID

(b) O registo de destino no pipeline EX/MEM é igual a algum dos registos fonte no pipeline ID/EX

(c) O registo de destino no pipeline MEM/WB é igual a algum dos registos fonte no pipeline IF/ID

4) A técnica de superpipelining

(a) Diminui o número de ciclos de relógio necessários à execução de uma instrução

(b) Possui um ciclo de relógio determinado pela instrução mais lenta

(c) Aumenta a exigência da largura de banda para a memória

5) A previsão dinâmica de saltos é

(a) Implementada pelo compilador recorrendo à análise da estrutura do programa

(b) Implementada em hardware recorrendo a memória indexada pelo endereço do salto

(c) Menos adaptativa do que a previsão estática de saltos

6) Nas arquitecturas static multiple­issue a distribuição das instruções pelas unidades funcionais

(a) É decidida previamente pelo compilador (b) É decidida em execução pelo hardware

(c) Nunca usa execução especulativa

7) A técnica de Simultaneous Multithreading (SMT)

(a) Exige duplicação de todo o processador

(b) Exige duplicação apenas dos componentes que armazenam o contexto dos processos

(c) Aumenta a performance do sistema independentemente da aplicação a executar

Pag. 1/2

8) A distribuição dinâmica de instruções por hardware

(a) Permite manter compatibilidade com software antigo

(b) Exige um compilador poderoso

(c) Explora paralelismo ao nível dos dados

9) A política de interacção write­back entre cache e memória (a) Nunca implica uma escrita na memória numa intrução de leitura

(b) Garante que múltiplas escritas no mesmo bloco apenas exigem um acesso à memória

(c) Tem como vantagem a coerência entre valores na cache e na memória

10) Numa cache fully associative um bloco pode ser colocado

(a) Numa única entrada possível

(b) Numa qualquer entrada da cache

(c) Numa qualquer entrada de um único conjunto possível

11) Aumentar apenas o tamanho dos blocos da cache pode aumentar o miss rate

(a) Uma vez que existe maior competição pela mesma entrada na cache

(b) Uma vez que existem agora mais blocos disponíveis

(c) A afirmação é falsa. O miss rate nunca aumenta com um maior tamanho dos blocos

12) Aumentar o grau de associatividade de uma cache pode ter como desvantagem

(a) Diminuir o miss rate, diminuindo as colisões entre os blocos

(b) Aumentar o miss rate, aumentando as colisões entre os blocos

(c) Maior custo e tempo de pesquisa de um bloco

13) A tabela de páginas no mecanismo de memória virtual

(a) Implica dois acessos à memória por cada operação lw/sw se não for usada TLB

(b) É necessária porque a colocação das páginas em memória é direct­mapped

(c) Tem um tamanho independente do tamanho da página

14) A sequência “TLB hit ­> Page Table miss ­> Cache miss” é

(a) Possível, TLB falha e a página não está em memória, nem na cache

(b) Impossível, porque não pode haver tradução de endereços se a página não está em memória

(c) Possível, TLB falha e a página é encontrada na memória

15) Numa máquina paralela de memória partilhada ligada por barramento único

(a) Não existem problemas de coerência das caches

(b) Os processadores comunicam através de variáveis partilhadas em memória

(c) Os processadores comunicam através de passagem de mensagens

16) Uma das vantagens das máquinas MPP quando comparadas com as máquinas SMP é

(a) Não existir necessidade de sincronização do acesso à memória

(b) Ser mais fácil programar eficientemente

(c) Menor overhead na comunicação entre processadores

Pag. 2/2