Flip-Flops

Introdução

Os circuitos combinacionais são aqueles onde as saídas dependem

apenas dos níveis lógicos colocados nas entradas. A mesma combinação de

entrada sempre produzirá o mesmo resultado na saída, porque circuitos

combinacionais não possuem memória.

A maioria dos sistemas digitais é composta tanto por circuitos

combinacionais como de elementos de memória. O elemento de memória mais

importante é o flip-flop.

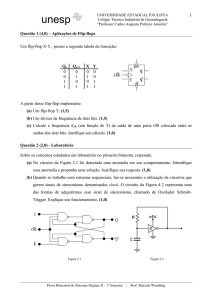

Flip-Flop R-S (Reset – Set)

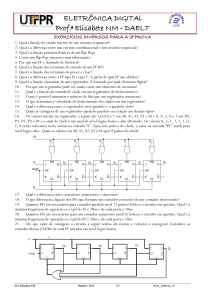

O circuito básico do flip-flop R-S é mostrado na fig.

O circuito acima mostra que o estado futuro das saídas Q e Q

dependem R e S e também do estado atual dessas saídas. Isso é mostrado na

tabela.

Nos casos 0 e 1, com S = 0 e R = 0, as saídas Q e Q permaneceram

inalteradas (memória). Nos casos 2 e 3, com S = 0 e R = 1, a saída Q foi para

0 e Q foi para 1. Nos casos 4 e 5, com S = 1 e R = 0, a saída Q foi para 1 e Q

foi para 0. Nos casos 6 e 7, com S = 1 e R = 1, as saídas Q e Q foram para 1,

ocasionando um problema, já que as saídas Q e Q devem ser

complementares.

Uma tabela simplificada e o símbolo do flip-flop R-S são mostrados na

fig.

O circuito do flip-flop R-S também pode ser implementado usando portas

NOR.

Flip-Flops com Clock

Circuitos que utilizam clock são chamados de circuitos síncronos. Muitos

flip-flops utilizam um sinal de clock para determinar o momento em que suas

saídas mudarão de estado. O sinal de clock é comum para todas as partes do

circuito.

Normalmente, o sinal de clock é uma onda quadrada e durante uma

transição positiva (nível 0 para nível 1) ou transição negativa (nível 1 para nível

0) a saída poderá mudar de estado.

Tempos de Setup e Hold

Os tempos de setup e hold são parâmetros que devem ser observados

para que o flip-flop possa trabalhar de modo confiável. O tempo de setup, tS,

corresponde ao intervalo no qual as entradas devem permanecer estáveis

antes da transição do clock. O tempo de hold, tH, corresponde ao intervalo no

qual as entradas devem permanecer estáveis depois da transição do clock.

Os tempos de setup e hold mínimos devem ser respeitados para o

funcionamento confiável do flip-flop.

TS = Tempos de setup

TH = Tempos de hold

Flip-Flop R-S com Clock

O símbolo do flip-flop R-S com clock é mostrado na fig.

Fig. Circuito lógico interno do flip-flop R-S com clock

O detector de transição é um circuito que habilitará, por alguns instantes,

as entradas SET e RESET, durante a transição de CLOCK. O circuito típico de

um detector de transição é mostrado na fig.

Fig. Circuitos detectores de transição positiva e negativa

Os tempos dos pulsos de CLK* correspondem aos tempos de atraso da

porta NOT, em torno de 5 ns.

Flip-Flop J-K

O símbolo do flip-flop J-K é mostrado na fig.

A operação do flip-flop J-K é semelhante à do flip-flop R-S. A diferença é

que o flip-flop J-K não possui a condição proibida, ou seja, J = K = 1. Nessa

situação, a saída será complementada (valor anterior será invertido).

O circuito interno do flip-flop J-K é mostrado na fig. 4-9:

Flip-Flop D

O símbolo do flip-flop D é mostrado na fig.

O circuito interno do flip-flop D é mostrado na fig. 4-11:

Circuito lógico interno do flip-flop D

Latch D

O símbolo lógico do latch D é mostrado na fig. 4-12. Diferentemente do

flip-flop D, o latch D possui uma entrada EN. Quando esta entrada estiver

habilitada, a saída é a cópia da entrada. Se ela estiver desabilitada, a saída

não mudará.

O circuito interno é mostrado na fig.

Entradas Assíncronas

Todas as entradas dos flip-flops até agora vistos dependem do sinal de

clock. Estas entradas são chamadas entradas síncronas. Em muitos flip-flops

existem outras entradas que são chamadas entradas assíncronas, ou seja, não

dependem do sinal de clock para atuarem.

Essas entradas são usadas para colocar o flip-flop no estado “0” ou “1”,

a qualquer instante. A tabela mostra as entradas assíncronas:

Tabela

PRESET CLEAR Resposta do Flip-Flop

Para a operação normal do flip-flop, as entradas PRESET e CLEAR

devem estar em “1”. A qualquer momento podemos forçar a saída Q a ser “0”

ou “1”. A última combinação não pode ser usada, já que é contraditória.

A fig. mostra as entradas assíncronas de um flip-flop J-K:

Simbologia do flip-flop J-K com as entradas assíncronas

Características de Temporizações dos Flip-Flops

As seguintes características de tempo devem ser respeitadas para o

funcionamento correto dos flip-flops.

Tempos de Setup e Hold – Correspondem aos intervalos de tempo que a

entrada deve permanecer estável antes e depois da transição do clock.

- Atrasos de Propagação – Na mudança de estado da saída, sempre

haverá um atraso entre a aplicação de um sinal na entrada e o momento

que a saída muda.

- Freqüência Máxima de Clock, fMAX – Esta é a freqüência mais alta que

pode ser aplicada no flip-flop de modo a dispará-lo confiavelmente.

- Tempos de Duração do Clock em ALTO e BAIXO – O tempo de duração

do clock em nível ALTO, tw(H) e o tempo de duração em nível BAIXO, tw(L)

são mostrados na figura abaixo.

Tempos de duração de clock em ALTO e BAIXO

Largura dos Pulsos Assíncronos – Assim como foram definidos larguras

mínimas de pulsos para o clock, as entradas assíncronas PRESET e

CLEAR também possuem larguras mínimas de pulsos para uma operação

correta.

Fig. 4-17: Larguras mínimas de pulsos assíncronos

Tempos de Transição do Clock – Para garantir o funcionamento correto

do flip-flop, o tempo transição do clock deve ser o menor possível. Para

dispositivos TTL esse tempo é 50 ns e para dispositivos CMOS, 200 ns.

Circuitos Geradores de Clock

A maioria dos sistemas digitais utiliza algum circuito gerador de clock.

Dentre essas aplicações podemos ter algumas que utilizam um sinal de clock

sem a exigência de precisão. Outras, porém, a precisão é fundamental.

Existem vários tipos de osciladores que podem gerar pulsos de clock

para sistemas digitais. Os menos precisos e menos estáveis (dependendo da

aplicação) utilizam resistores e capacitores. Os mais precisos e estáveis

utilizam cristais de quartzo e com freqüências muito maiores do que os circuitos

que utilizam resistores e capacitores como geradores de clock.

Oscilador Schmitt-Trigger

Um típico gerador de clock usando dispositivos Schmitt-Trigger é

mostrado na figura abaixo:

Fig. Circuito de um oscilador utilizando inversor Schmitt-Trigger

Temporizador 555 como Oscilador

O circuito integrado 555 também pode ser usado como gerador de clock.

A figura abaixo mostra isso:

Fig. Circuito de um oscilador utilizando o temporizador 555

Osciladores a Cristal de Quartzo

A principal característica dos osciladores a cristal de quartzo é sua

estabilidade e precisão quanto à freqüência de oscilação. A figura seguinte

mostra circuitos osciladores que utilizam cristais de quartzo.

Contadores

Introdução

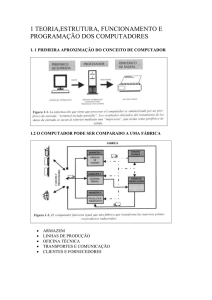

Os flip-flops têm funções ilimitadas em sistemas digitais. Podemos

associá-los e utilizá-los como contadores, registradores e muitos outros

circuitos.

Os contadores podem ser assíncronos ou síncronos. Basicamente, a

principal diferença entre eles é que o síncrono utiliza um sinal de clock comum

a todos os flip-flops e o assíncrono possui um sinal de clock que é dividido até

o último flip-flop.

Os registradores também são arranjos de flip-flops, mas com o objetivo

de armazenar, manipular e transferir dados entre outros registradores ou

circuitos.

Contadores Assíncronos

Os contadores assíncronos também são chamados de contadores por

pulsação (ripple counter). Um circuito típico de um contador assíncrono é

mostrado na fig.

Fig. Contador assíncrono utilizando flip-flops J-K

Estado D C B A Decimal

A tabela mostra os estados de contagem deste contador assíncrono

de quatro bits.

Podemos perceber que a cada 16 estados esse contador reinicia sua

contagem. Então ele é um contador assíncrono módulo 16, ou seja, tem 16

estados (0000 até 1111) distintos. Equacionando:

Módulo 2N

onde N é o número de flip-flops conectados (número de bits).

Nos contadores assíncronos, a freqüência do clock é dividida por 2 em

cada flip-flop, ou seja: na saída A teremos Clock / 2, na saída B teremos Clock /

4, na saída C teremos Clock / 8 e na saída D teremos Clock / 16. Concluindo,

os contadores assíncronos são divisores de freqüência e no último flip-flop

teremos a freqüência de clock dividida pelo módulo desse contador.

Contadores de Módulo < 2N

Um contador assíncrono com N flip-flops terá, no máximo, módulo 2N. Se

precisarmos de um contador com módulo menor do que 2N será necessário

utilizar um circuito adicional, conforme mostrado na fig. 5-2:

Fig. Contador assíncrono com módulo < 2N

A fig. mostra um contador módulo 6. Se não houvesse a porta NAND

ligada nas entradas CLEAR dos flip-flops, o módulo seria 8. A seqüência de

contagem é mostrada na tabela

Tabela

5.4- Diagrama de Transição de Estados

O diagrama de transição de estados é mostrado na fig.

Fig. Diagrama de transição de estados de um contador módulo 6

Neste diagrama, as linhas contínuas correspondem aos estados estáveis

e as linhas tracejadas indicam o estado temporário.

O procedimento para a construção de um contador módulo X é:

- Determinar o menor número de flip-flops tal que 2N X. Se 2N = X, não é

necessário conectar a porta NAND na entrada assíncrona CLEAR;

- Conectar a porta NAND nas entradas assíncronas CLEAR de todos os flipflops;

- Determinar quais saídas estarão em ALTO na contagem X. Então é só

conectar essas saídas nas entradas da porta NAND.

Contadores de Década

Contadores de década ou decádicos são contadores que possuem 10

estados distintos, não importando a seqüência. Quando um contador decádico

conta em seqüência de 0000 a 1001 (0 a 9), ele é chamado de contador BCD.

Circuitos Integrados de Contadores Assíncronos

Existem vários circuitos integrados de contadores assíncronos, tanto

TTL como CMOS.

O circuito integrado TTL 74LS293 é um contador com quatro flip-flops JK.

Vários circuitos TTL têm suas versões CMOS. O circuito integrado CMOS

74HC4024 é um contador com sete flip-flops que não possui correspondente

TTL.

Contador Assíncrono Decrescente

Os contadores que contam progressivamente a partir do zero são

denominados contadores crescentes. Já os contadores decrescentes contam

do valor máximo até zero.

Um contador decrescente pode ser construído conforme mostrado na fig.

Nesse circuito vemos que o clock de cada flip-flop é acionado com a

saída invertida do flip-flop anterior. Com isso a saída é invertida, ou seja,

conforme a tabela abaixo:

próximo pulso fará com que o contador BCD de unidades vá a 0.

Nesse momento também ocorrerá uma transição de 1 para 0 (borda de

descida) da saída D que está ligada ao clock do contador BCD de dezenas. E

agora o display mostrará o valor 010.

Isso continua até 999 quando, no próximo pulso, os contadores irão para

000, iniciando novamente a contagem.

Registradores

Introdução

A utilização mais comum dos flip-flops é no armazenamento e

transferência de informações. Essas informações são armazenadas em grupos

de flip-flops chamados registradores.

Além de armazenar informações, os registradores têm a capacidade de

transferir essas informações para outros registradores. Isso é bastante

interessante, já que o armazenamento e a transferência de dados são as

principais características dos sistemas digitais.

Registradores de Deslocamento

A fig. mostra um registrador de deslocamento de 4 bits e suas

formas de onda.

A cada pulso de clock, o valor contido nas entradas J e K dos flip-flops é

transferido para a saída. Essa saída está conectada na entrada do próximo flipflop

e no final de 4 pulsos de clock, o valor da entrada DADOS, que foi

transferido serialmente, estará armazenado no registrador.

6.3- Transferência Paralela de Dados entre Registradores

A fig. mostra a transferência paralela de dados entre dois

registradores:

Fig.: Transferência paralela de dados entre registradores

As saídas dos flip-flops que constituem o registrador X estão conectadas

nas entradas dos flip-flops que constituem o registrador Y. Depois do pulso

TRANFER, o conteúdo armazenado no registrador X é transferido para o

registrador Y.

Transferência Serial de Dados entre Registradores

A fig. 6-3 mostra a transferência serial de dados entre dois registradores.

Fig.: Transferência serial de dados entre registradores

Comparação entre a Transferência Paralela e a

Transferência Serial

Na transferência paralela, os dados são transmitidos simultaneamente

na ocorrência de um único pulso de transferência. Na transferência serial, cada

bit é transmitido a cada pulso de transferência.

Com relação à velocidade de transmissão, a transferência paralela é

mais rápida do que a serial. Em compensação, a transferência paralela

necessita de um número maior de conexões entre os registradores.

Circuitos Integrados de Registradores

Os registradores podem ser classificados da forma com a qual seus

dados são transferidos:

- Entrada paralela / saída paralela – 74174, 74LS174, 74HC174;

- Entrada serial / saída serial – 4731B;

- Entrada paralela / saída serial – 74165, 74LS165, 74HC165;

- Entrada serial / saída paralela – 74164, 74LS164, 74HC164.

Existem outras versões de registradores como, por exemplo:

- 74194, 74LS194, 74HC194 – registrador de deslocamento bidirecional

universal de quatro bits com entrada paralela e saída paralela.

- 74373, 74LS373, 74HC373, 74HCT373 – registrador de oito bits de entrada

paralela e saída paralela que contém oito latches tipo D com saídas em

tristate.

- 74374, 74LS374, 74HC374, 74HCT374 – registrador de oito bits de entrada

paralela e saída paralela que contém oito flip-flops tipo D com saídas em

tristate.

Unidade Lógica e Aritmética

O principal objetivo de uma ULA é aceitar dados binários armazenados

na memória e executar as operações lógicas e aritméticas sobre estes dados

de acordo com as instruções da unidade de controle.

A fig. mostra os principais blocos funcionais de uma ULA:

Fig.: Blocos funcionais de uma ULA

A ULA é constituída de, pelo menos, dois registradores: o registrador B e

o registrador acumulador. Ela também possui lógica combinacional que realiza

as operações lógicas e aritméticas sobre os números binários armazenados

nos registradores B e acumulador.

Por exemplo, os passos para a execução de uma operação de adição

são mostrados a seguir:

- A unidade de controle recebe uma instrução da unidade de memória

especificando que um número armazenado em uma posição particular de

memória deve ser adicionado ao número que está armazenado na

acumulador;

- O número a ser adicionado é transferido da memória para o registrador B;

- O número no registrador B e o número no acumulador são somados nos

circuitos lógicos (ao comando da unidade de controle). O resultado é

enviado para o acumulador para ser armazenado.

Somador Binário Paralelo

Vamos analisar a seguinte operação de adição de dois números

binários:

Podemos ver que cada bit das parcelas é somado para gerar um bit no

resultado da adição. No caso de um carry (vai-um), esse também é somado,

ou seja:

O diagrama de blocos de um somador binário paralelo é mostrado na fig.

Diagrama em blocos de um somador binário paralelo

O bloco SC #0 é chamado somador completo porque soma bits A0 e B0

das parcelas e ainda um possível bit C0 de carry.

Projeto de um Somador Completo

O bloco do somador completo possui três entradas (A, B e CIN) e duas

saídas (S e COUT). As entradas A e B são os bits a serem adicionados e CIN é o

carry do bit anterior. A saída S é o resultado da adição e COUT é a saída de

carry, indicando um vai-um.

A tabela 8-2 relaciona todos os possíveis casos de uma adição.

Fig.: Bloco lógico do somador completo de 1 bit

Pelo método do Mapa de Karnaugh podemos encontrar a expressão

para S e COUT:

S A.B.CIN A.B.CIN A.B.CIN A.B.CIN A B CIN

C A.C B.C A.B OUT IN IN

A fig. mostra o circuito de um somador completo (SC).

Circuito lógico do somador completo de 1 bit

A fig. 8-6 mostra um circuito de um somador paralelo completo de 4 bits

com registrador.

O procedimento para um operação de adição é o seguinte:

- Pulsar CLEAR para fazer registrador A = 0000;

- Colocar a primeira parcela a ser somada nas entradas D3D2D1D0 (esse

dado pode estar vindo de uma memória). Pulsar LOAD para que as

entradas sejam transferidas para o registrador B;

- Pulsar TRANSFER para a realização da operação de adição do conteúdo

do registrador A com o conteúdo do registrador B. Nesse caso, o valor de B

é transferido para A, resultando A = B;

- Colocar a segunda parcela a ser somada nas entradas D3D2D1D0. Pulsar

LOAD para que as entradas sejam transferidas para o registrador B;

- Pulsar TRANSFER para a realização da operação de adição do conteúdo

do registrador A com o conteúdo do registrador B. O resultado da adição

está no registrador A (saídas).

Somador Paralelo Integrado

Os circuitos integrados 7483A, 74LS83A, 74283 e 74LS283 são

somadores paralelos de quatro bits.

Ligação em Cascata de Somadores Paralelos

Blocos de somadores podem ser associados em cascata de forma a

efetuar adições de números binários maiores. Por exemplo, se dois somadores

de quatro bits forem associados em cascata podemos efetuar adições de

números com oito bits.

8.12- Circuito Integrados de ULAs

As ULAs são circuitos capazes de realizar diversas operações lógicas e

aritméticas sobre os dados binários de entrada. Dentre essas operações

podemos citar:

- Operação Clear;

- Operação Soma;

- Operação Subtração;

- Operação EX-OR;

- Operação OR;

- Operação AND;

- Operação PRESET.

Os circuitos integrados 74LS382 e 74HC382 são ULAs que possuem as

características acima citadas.

O 74LS181/HC181 é uma ULA de quatro bits e tem até 16 operações

diferentes. O 74LS881/HC881 é similar ao circuito integrado 181, mas tem a

capacidade de realizar algumas operações lógicas adicionais.

Memórias

Introdução

A principal vantagem dos sistemas digitais sobre os analógicos é a

capacidade de armazenar grandes quantidades de informações. Esta

capacidade é que torna os sistemas digitais tão versáteis e adaptáveis às

diversas situações.

Um dispositivo de memória conhecido é o flip-flop. Grupos de flip-flops,

chamados registradores, são elementos de memória de alto desempenho que

são muito usados nas operações internas de um computador. Um outro

dispositivo de memória pode ser um capacitor onde os dados são

armazenados como cargas.

Estes dois dispositivos são os principais elementos que formadores das

memórias dos sistemas digitais atuais.

Definição de Termos Básicos

Célula de memória – dispositivo ou circuito capaz de armazenar um bit.

Por exemplo, um flip-flop, um capacitor, etc.

Palavra de memória – grupo de bits (células) em uma memória que

representa instruções ou dados.

- Byte – conjunto de 8 bits.

- Capacidade – número de bits que podem ser armazenados em um

dispositivo de memória.

a) Um certo chip de memória semicondutora é especificado como 2K x 8.

Quantas palavras podem ser armazenadas neste chip? Qual é o tamanho

da palavra? Quantos bits esse chip pode armazenar no total?

R: A memória possui capacidade de 2K = 2 x 1024 = 2048 palavras. Cada

palavra tem 8 bits (um byte). O número total de bits é 2048 x 8 = 16384 bits.

b) Qual das memórias armazena mais bits: uma memória de 5M x 8 ou uma

memória que armazena 1M palavras com um tamanho de palavra de 16 bits?

R:

5M x 8 = 5 x 1048576 x 8 = 41943040 bits

1M x 16 = 1048576 x 16 = 16777216 bits

A memória de 5M x 8 armazena mais bits.

Densidade – termo relativo à capacidade. Se um dispositivo é mais denso

que outro ele tem capacidade de armazenar mais bits no mesmo espaço.

Endereço – número que localiza a posição de uma palavra na memória.

Tabela

Cada palavra tem um endereço binário específico

- Leitura ou busca – operação na qual uma palavra binária localizada numa

determinada posição (endereço) de memória é detectada e transferida para

outro dispositivo.

- Escrita ou armazenamento – operação na qual uma nova palavra é

colocada numa determinada posição de memória.

- Tempo de acesso – tempo necessário entre a memória receber uma nova

entrada de endereço e os dados se tornarem disponíveis na saída da

memória. Este parâmetro é usado para medição de desempenho da

memória.

- Ciclo de Memória – intervalo mínimo entre dois acessos sucessivos à

memória.

- Memória volátil – tipo de memória que necessita de aplicação de energia

para poder armazenar a informação.

- Memória de acesso aleatório (RAM) – memória onde o tempo de acesso

é o mesmo para qualquer posição.

- Memória de acesso seqüencial (SAM) – memória onde, para se localizar

uma determinada posição, é preciso passar por todos os endereços. Por

exemplo, fitas magnéticas.

- Memória de leitura e escrita (RWM) – memória que pode ser tanto lida

como escrita.

- Memória somente de leitura (ROM) – Memória onde as informações

armazenadas só podem ser lidas.

- Memória estática – tipo de memória onde os dados permanecem

armazenados enquanto existir energia, sem a necessidade de atualização

periódica da informação.

- Memória dinâmica – tipo de memória onde os dados permanecem

armazenados enquanto existir energia, mas com periódica atualização da

informação (Refresh).

Princípios de Operação das Memórias

Independente dos tipos de memórias existentes, o princípio básico de

operação é o mesmo:

- Selecionar o endereço a ser acessado (leitura ou escrita);

- Selecionar o tipo de operação: leitura ou escrita;

- Se a operação for escrita, fornecer os dados de entrada;

- Se a operação for leitura, os dados estarão disponíveis na saída;

- Habilitar a memória para que a operação seja concluída e desabilitar a

memória para que ela não responda às entradas de endereço e ao

comando de leitura/escrita.

Fig. Diagrama de uma memória de 32 x 4

Entradas de Endereços

Usando a memória mostrada na fig. 11-1, podemos notar que ela possui

5 entradas de endereço (A0 a A4). Logo existem 32 posições (2N, onde N é o

nº de bits) de armazenamento que podem ser ocupadas por palavras de 4 bits

(D0 a D3).

A Entrada ada R / W

Esta entrada controla a operação que deve ser realizada na memória:

leitura (R – Read) ou escrita (W – Write). Quando esta entrada estiver em “1”

ocorre a operação de leitura, quando em “0” ocorre a operação de escrita.

Algumas memória usam os símbolos W (escrita) ou WE (habilitação de

escrita) para identificar esta entrada.

Habilitação de Memória (ME)

A todo momento a memória possui níveis lógicos em suas entradas e o

pino de habilitação de memória impede que ela responda a estes níveis

lógicos, evitando assim um acesso errôneo nesta memória.

Esta entrada pode ser identificada como CE (chip enable) ou CS (chip

select).

Exemplo: Uma determinada memória tem uma capacidade de 4K x 8.

Quantas linhas de entrada/saída de dados ela tem?

R: Oito, pois o tamanho da palavra é oito bits.

Quantas linhas de endereço ela tem?

R: A memória armazena 4K = 4 x 1024 = 4096 palavras. Tendo em vista que

4096 = 212, logo a memória tem 12 bits (linhas) de endereço.

Qual é a sua capacidade em bytes?

R: Um byte tem oito bits, então esta memória tem uma capacidade de 4096

bytes.

Conexões da Memória com a CPU

As memórias RAM e ROM são interfaceadas com a CPU através de três

grupos de linhas de sinais ou barramentos: barramentos de endereço,

barramento de dados e barramento de controle.

- Barramento de endereços – barramento unidirecional que leva o endereço

proveniente da CPU para a memória para selecionar uma posição de

memória.

- Barramento de dados – barramento bidirecional que transfere dados entre

a CPU e a memória.

- Barramento de controle – barramento que leva sinais de controle da CPU

para a memória.

Exemplo:

Operação de escrita:

- A CPU coloca o endereço binário da posição de memória onde o dado deve

ser armazenado no barramento de endereços.

- A CPU coloca o dado a ser armazenado no barramento de dados.

- A CPU ativa as linhas de controle para a operação de escrita.

- A memória decodifica o endereço e localiza a posição onde o dado deve ser

armazenado.

- O barramento de dados é transferido para a posição de memória.

Operação de leitura:

- A CPU coloca o endereço binário da posição a ser lida da memória no

barramento de endereços.

- A CPU ativa as linhas de controle para operação de leitura.

- A memória decodifica o endereço e localiza a posição a ser lida.

- A memória transfere o dado armazenado nesta posição para o barramento

de dados, onde a CPU vai buscá-los.

Memória Somente de Leitura (ROM)

Introdução

A memória somente de leitura (ROM) é um tipo de memória onde os

dados nela armazenados não são alterados ou não mudam com freqüência.

Diagrama em Blocos de uma ROM

O diagrama típico de uma ROM é mostrado na fig.

Fig. Diagrama de uma ROM

O sinal de controle CS (seleção do chip) habilita a operação de leitura

da posição indicada no barramento de endereços. O dado é transferido para o

barramento de dados. Quando CS está em ALTO, as saídas da ROM ficam

desabilitadas (alta impedância).

Arquitetura de uma ROM

Uma ROM é constituída conforme a fig. 12-2.

Fig. Arquitetura interna de uma ROM (16 x 8)

- Matriz de registradores – onde os dados serão armazenados. Cada

registrador contém um número de células de memória igual ao tamanho da

palavra utilizada. Cada registrador tem duas entradas de habilitação (E):

ambas devem estar em ALTO para que os dados do registrador sejam

colocados no barramento de dados.

- Decodificadores de endereços – o barramento de endereço é separado

em duas vias: a primeira seleciona a linha e a segunda seleciona a coluna

onde o registrador se localiza.

Exemplo: Qual o registrador que será habilitado pelo endereço 1101? Que

endereço irá habilitar o registrador 7?

- Buffers de saída – o registrador que está habilitado pelas entradas de

endereço coloca seu conteúdo no barramento de dados. Estes dados vão

para os buffers de saída, que colocarão os dados na saída de dados

externa, desde que CS esteja em BAIXO. Se CS estiver em alto, os buffers

de saída ficarão em alta impedância.

12.4- Temporização de uma ROM

O atraso de propagação entre a aplicação dos sinais de entrada e o

aparecimento dos dados na saída, durante a operação de leitura, é chamado

tempo de acesso (tACC). Existe um outro parâmetro de temporização chamado

tempo de habilitação da saída (tOE), que representa o atraso entre a entrada

CS e a saída de dados válidos.

Fig.: Temporização de uma ROM

Tipos de ROM

- ROM Programada por Máscara – este tipo de ROM tem suas posições

escritas (programadas) pelo fabricante de acordo com as especificações do

cliente. Uma máscara (tipo de negativo fotográfico) é usada para informar

as conexões elétricas do chip. Este tipo de ROM é usado para armazenar

tabelas ou informações pré-programadas como códigos geradores de

caracteres de terminais de vídeo.

- ROM Programável (PROM) – tipo de memória ROM onde a programação é

feita apenas uma única vez pelo usuário. Esta programação consiste na

queima ou não de um fusível que corresponde a um bit de informação por

um equipamento chamado programador.

- ROM Programável e Apagável (EPROM) – tipo de memória ROM que

pode ser programada e apagada pelo usuário várias vezes. O processo de

programação consiste em aplicar certos níveis de tensões que provocam a

condução permanente ou não condução de transistores MOS. O

apagamento da memória é feito pela exposição dos circuitos internos à luz

ultravioleta através de uma “janela”.

- PROM Apagável Eletricamente (EEPROM) – é uma melhoria em relação

às EPROMs pois pode ser tanto programada como apagada eletricamente.

Assim, elas podem ser programadas e apagadas no próprio circuito, sem a

necessidade de luz ultravioleta ou um programador especial.

- CD ROM – tipo de armazenamento somente para leitura que utiliza

tecnologia laser. Os bits são definidos pela reflexão ou não de um feixe

laser apontado para um ponto do disco.

- Memória Flash – tipo de memória não-volátil, apagável eletricamente como

a EEPROM, mas com densidades e custos semelhantes aos da EPROM,

com o mesmo tempo de acesso de ambas.

Fig. Comparação entre tipos de ROM

Aplicações de ROMs

- Firmware – armazenamento de programas ou dados que devem estar

disponíveis no processo de inicialização de sistemas microprocessados. Por

exemplo, produtos como videocassetes, CD players, fornos microondas etc.

- Memória de Bootstrap – tipo de programa armazenado em uma ROM que

trata da inicialização do hardware de um computador. Após a inicialização,

o programa de bootstrap chama o sistema operacional e o computador

começa a executar o sistema operacional.

- Tabela de Dados – as ROMs são bastante utilizadas para armazenar

tabelas de dados que não variam. Por exemplo, tabela trigonométricas,

códigos ASCII, etc.

- Conversor de Códigos – este tipo de aplicação toma valores expressos

em um determinado tipo de código e produz uma saída expressa em outro

código. Por exemplo, o código BCD pode ser convertido para 7 segmentos

por uma ROM.

- Gerador de Funções – basicamente, um gerador de funções é um circuito

que produz formas de onda senóides, triangulares e quadradas. Uma ROM

com tabelas de valores armazenados e um conversor D/A podem ser

usados para gerar essas formas de onda.

- Armazenamento Auxiliar – dados podem ser armazenados em memórias

ROM apagáveis (EPROM, EEPROM, FLASH), tornando essas memórias

como alternativa aos discos magnéticos de armazenamento.

Memória de Acesso Aleatório (RAM)

Introdução

A memória de acesso aleatório (RAM) semicondutora é um tipo de

memória onde podemos tanto ler como escrever dados.

A principal vantagem de uma RAM é o fato de ela poder ser escrita e lida

rapidamente com a mesma facilidade. Uma desvantagem seria o fato da RAM

ser volátil, isto é, se a alimentação for desligada ela perde a informação.

Arquitetura de uma RAM

A arquitetura típica de uma RAM é mostrada na fig.

Fig. Organização Interna de uma RAM de 64 x 4

A fig. mostra uma RAM que armazena 64 palavras de quatro bits

(memória 64 x 4). Estas palavras têm endereços que vão de 0 a 63. Para

selecionar uma das 64 posições para escrita ou leitura, um endereço binário é

fornecido ao circuito decodificador. Cada endereço ativa uma saída do

decodificador, habilitando o seu registrador correspondente.

Operação de Leitura

A operação de leitura do conteúdo de um registrador é feita da seguinte

maneira:

- Coloca-se o endereço da posição de memória a ser lida no barramento de

endereços;

- Indica-se a operação de leitura através s da entrada R / W , colocando essa

entrada em ALTO;

- Habilita-se o chip de memória para concluir a operação colocando a entrada

CS em BAIXO.

Quando a memória está habilitada para leitura, os buffers de entrada

são desabilitados e os buffers de saída são habilitados e o conteúdo da

posição de memória selecionada é colocada nas quatro saídas de dados.

Operação de Escrita

A operação de escrita de um dado novo em um registrador selecionado

é feita do seguinte modo:

- Coloca-se o endereço da posição de memória a ser escrita no barramento

de endereços;

- Coloca-se o dado a ser escrito no barramento de dados;

- Indica-se a operação de escrita através da entrada R / W , colocando essa

entrada em BAIXO;

- Habilita-se o chip de memória para concluir a operação colocando a entrada

CS em BAIXO.

Quando a memória está habilitada para escrita, os buffers de entrada

são habilitados e os buffers de saída são desabilitados e o conteúdo da

posição de memória selecionada é perdida com a escrita do novo dado.

Quando a entrada CS (chip select – seleção de chip) está em ALTO

(memória desabilitada), tanto suas entradas como suas saídas estão em tristate

(alta impedância), evitando assim escrita ou leitura errônea neste chip.

RAM Estática (SRAM)

Este tipo de memória armazena os dados enquanto for mantida a

alimentação. Suas células são compostas de flip-flops, e por isso seu conteúdo

não é perdido enquanto houver alimentação.

Temporização de uma RAM Estática

Um computador utiliza RAMs como memórias principais e essas

memórias devem ser rápidas o suficiente para responderem aos comandos de

leitura e escrita que a CPU está constatemente realizando.

Ciclo de Leitura

O ciclo de leitura é mostrado na fig.

Fig. Ciclo de leitura de uma RAM estática

Onde:

trc = intervalo de duração do ciclo de leitura;

tacc = tempo de acesso à RAM;

tco = tempo que a saída da RAM leva para sair de alta impedância e ter um

dado válido;

tod = tempo decorrido entre a desabilitação da RAM e o instante que as saídas

da RAM vão para alta impedância.

Durante o ciclo de leitura, a CPU coloca um endereço no barramento de

endereços ligado à RAM. Este endereço corresponde à posição de memória

que deve ser lida.

A CPU sinaliza a operação de leitura através de um nível ALTO na

entrada ada R / W . A CPU habilita a memória colocando a entrada CS em nível

BAIXO. A RAM responde a isso colocando o conteúdo da posição endereçada

nas saídas de dados. Depois disso a memória é desabilitada (CS é ALTO) e

suas saídas ficam em tri-state (alta impedância).

Ciclo de Escrita

O ciclo de escrita é mostrado na fig.

Fig. Ciclo de escrita de uma RAM estática

Onde:

twc = intervalo de duração do ciclo de escrita;

tas = tempo para estabilização do barramento de endereços, antes de habilitar

a RAM;

tah = intervalo necessário para que o barramento de endereços permaneça

estável;

tw = tempo de escrita, onde CS e R / W ficam em BAIXO;

tds = tempo que os dados devem ser mantidos na entrada antes da

desabilitação de CS e R / W;

tdh = tempo que os dados devem ser mantidos na entrada depois da

desabilitação de CS e R / W.

No ciclo de escrita, a CPU coloca um endereço estável no barramento

de endereços. Nesse endereço o dado deve ser escrito. Ela coloca o dado a

ser armazenado no barramento de dados.

A CPU sinaliza a operação de escrita, colocando nível BAIXO na entrada

R / W . A CPU habilita a memória colocando a entrada CS em nível BAIXO. O

dado é transferido para a posição de memória indicada pelo endereço. A

memória é, então, desabilitada (CS é ALTO) e suas saídas ficam em tri-state.

Exemplos de Memórias Estáticas

- 6264 – 8K x 8

- 62256 – 32K x 8

RAM Dinâmica (DRAM)

Nesse tipo de memória a informação é armazenada em pequenos

capacitores. Como existe uma tendência normal dos capacitores se

descarregarem, há a necessidade de uma recarga (refresh – refrescamento)

desses capacitores. De tempos em tempos (tipicamente de 2 a 8 ms) o bit

armazenado no capacitor é atualizado.

Esse tipo de memória constitui a memória principal de um computador

por causa de sua alta capacidade e baixo consumo. Em relação à velocidade,

as RAM estáticas são mais rápidas.

A principal vantagem deste tipo de memória é a simplicidade na sua

construção, alcançando, assim, alto grau de integração.

Estrutura e Operação da RAM Dinâmica

Simbolicamente uma célula de memória dinâmica é constituída conforme

a fig..

Fig.: Representação simbólica de uma célula de memória dinâmica

Para escrever em uma célula, os sinais provenientes da decodificação

de endereços e da lógica de leitura/escrita fecham as chaves SW1e SW2,

mantendo SW3 e SW4 abertas. Isto conecta a entrada de dados a C. Um nível

lógico 1 carrega C e um nível lógico 0 o descarrega. Depois disso todas as

chaves são abertas, de modo que C fica desconectado do resto do circuito.

Mesmo desconectado, existe uma corrente de fuga que causa a descarga

gradual do capacitor e por isso o capacitor deve ser “refrescado”.

Para ler uma célula, as chaves SW2, SW3 e SW4 são fechadas, e SW1

permanece aberta. Isso conecta a tensão armazenada no capacitor ao

amplificador sensor. Assim, na saída do amplificador teremos o valor

armazenado no capacitor, que é atualizado via SW4 no momento da leitura.

Multiplexação de Endereços

A multiplexação de endereços é uma técnica que visa diminuir a

quantidade de entradas de endereços em uma DRAM. Isso permite que

DRAMs com altas capacidades ocupem espaços menores em placas de

computadores.

Essa multiplexação consiste em colocar no barramento de endereços a

metade superior do endereço (que localiza a linha) e colocar em BAIXO um

sinal chamado RAS (strobe do endereço da linha). Depois é colocado no

barramento de endereços a metade inferior do endereço (que localiza a coluna)

e colocar em BAIXO um sinal chamado CAS (strobe do endereço da coluna).

Após esse procedimento, a posição de memória é localizada e as operações

de leitura ou escrita podem ser realizadas.

Fig. Multiplexação de endereços em uma DRAM com 16 linhas de

endereço.

Refrescamento da DRAM

O refrescamento de uma DRAM é feito por circuitos externos ou no

próprio chip de memória. Existem dois métodos:

Refresh em rajada – a operação normal da memória é suspensa e cada linha

da DRAM é refrescada em seqüencia até que todas tenham sido refrescadas;

Refresh distribuído – o refrescamento é intercalado com as operações

normais da DRAM.

Tecnologia de RAM Dinâmica Usada em Computadores

Os tipos de DRAM existentes variam em função da capacidade,

velocidade, consumo, custo e versatilidade:

- SIMM (single-in-line memory module) e DIMM (dual-in-line memory

module) – são módulos de memória que permitem uma instalação rápida e

são padrões de diversos tipos de DRAMs. Os módulos SIMM e DIMM

definem apenas como a DRAM é “empacotada”.

- DRAM FPM (fast page module) – permite acesso mais rápido a qualquer

posição de memória dentro da “página” corrente. Normalmente, a maioria

dos dados gravados na memória são seqüenciais. Nesse tipo de DRAM o

endereço da linha (RAS) é enviado uma vez e o endereço da coluna (CAS)

é incrementado.

- DRAM EDO (extended data output) – é uma melhoria em relação às FPM.

Os dados são colocados na saída e a DRAM EDO já pode decodificar o

próximo endereço sem que esses dados tenham sido lidos;

- DRAM BEDO (burst EDO) – Possui uma arquitetura que permite alcançar

alta velocidade ao se acessar dados seqüenciais;

- SDRAM (synchronous DRAM) – são organizadas em dois bancos que são

acessados alternadamente utilizando um sinal de clock sincronizado com a

CPU. Desse modo essas memórias alcançam altas taxas de transferências.

Memórias com Funções Especiais

- Armazenamento de Dados com o Sistema Desligado – muitos

equipamentos armazenam seus dados em memórias RAM alimentadas com

baterias de reserva (NVRAM – RAM não-volátil);

- Memória Cache – tipo de memória de alta velocidade e baixa capacidade

de armazenamento que interage diretamente com a CPU. Na cache estão

contidos os dados mais requisitados pelo processador e isso evita um

acesso desnecessário na RAM.

- Memória First-In, First-Out (FIFO) – também conhecidas como buffers

para armazenamento temporário. Por exemplo, os dados são transferidos

em altas taxas do PC para a impressora. Como a impressão é mais lenta

que a transferência, esses dados devem ser armazenados em FIFOs e daí

podem ser impressos.

Expansão do Tamanho da Palavra e da Capacidade

Introdução

Em aplicações com memórias muitas vezes não dispomos de um chip

que nos forneça o tamanho da palavra ou a capacidade necessária. Para

conseguir isso devemos associar os chips de memória a fim de fornecer o

tamanho da palavra ou a capacidade desejada.

Expansão do Tamanho da Palavra

Neste tipo de arranjo, as memórias são combinadas de forma a fornecer

o tamanho da palavra desejada. Por exemplo, se determinado projeto

necessita de uma memória de 16 x 8 (16 palavras de 8 bits) e só possuímos

chips de memória de 16 x 4 (16 palavras de 4 bits) podemos associar duas

dessas memórias para obter a memória desejada, conforme a fig.

Fig.: Arranjo com duas RAM de 16 x 4 para fornecer um módulo de 16 x 8.

Cada memória da figura acima pode armazenar 16 palavras de 4 bits.

Como queremos armazenar 16 palavras de 8 bits, cada chip armazena metade

de cada palavra. Assim, a RAM0 armazena os 4 bits mais significativos de

cada uma das 16 palavras e a RAM1 armazena os 4 bits menos significativos

de cada uma das 16 palavras.

Podemos selecionar qualquer uma das 16 palavras aplicando-se o

endereço da palavra no barramento de endereços. As duas memórias

localizarão ao mesmo tempo a mesma posição de memória.

Se a operação for leitura, a, a entrada R / W deve estar em ALTO e CSem

BAIXO. A RAM0 coloca sua palavra de 4 bits na parte alta do barramento de

dados e a RAM1 coloca sua palavra de 4 bits na parte baixa do barramento de

dados. Desse modo o barramento de dados contém a palavra completa de 8

bits.

Se a operação for escrita, a, a entrada R / W deve estar em BAIXO e CS

em BAIXO. Os 4 bits mais significativos do dado serão escritos na RAM0 e os 4

menos significativos serão escritos na RAM1.

Expansão da Capacidade

Neste tipo de arranjo, as memórias são combinadas de forma que

possam armazenar mais palavras. Por exemplo, se precisamos de uma

memória que possa armazenar 32 palavras de 4 bits e temos chips de 16

palavras de 4 bits, podemos associá-las conforme a fig.

Fig. Arranjo de duas memórias de 16 x 4 para formar uma memória de 32 x 4.

Cada chip de memória armazena 16 palavras de 4 bits, resultando em

32 palavras de 4 bits. O barramento de dados é compartilhado entre as duas

memórias e por isso somente um chip de memória poderá ser habilitado de

cada vez.

Como a capacidade total é 32 x 4, devem existir 32 endereços

diferentes. Isso requer 5 linhas de barramento de endereços. A linha de

endereços mais significativa (A4) é usada para selecionar qual memória deve

ser acionada.

Tabela

Se desejarmos associar mais chips de memórias devemos tomar o

cuidado de selecionar apenas uma das memórias, já que o barramento de

dados é compartilhado. Para isso é usado um decodificador de endereços (por

exemplo, 74LS138) que, através de uma combinação em suas entradas,

seleciona apenas uma saída.

Por exemplo, se desejarmos associar 4 PROMs de 16 x 4 para gerar

uma capacidade de 64 x 4 devemos fazer conforme a fig.

Fig. Uso de 4 PROMs de 16 x 4 para obter uma capacidade de 64 x 4

Tabela