Aula 15: Ciclo de Execução e Introdução ao Pipeline

Diego Passos

Universidade Federal Fluminense

Fundamentos de Arquiteturas de Computadores

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

1 / 42

.

Revisão

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

2 / 42

.

Na Última Aula. . .

Começamos a falar sobre as instruções de máquina.

▶

Operações simples que o hardware é capaz de executar.

Programas executados por um computador são armazenados como sequências de

instruções na memória.

▶

▶

▶

Há um registrador especial chamado PC.

Ele armazena o endereço da próxima instrução a ser executada.

A cada nova instrução executada, PC é incrementado.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

3 / 42

.

Na Última Aula. . . (II)

Discutimos tipos de instrução.

▶

▶

▶

▶

▶

Instruções

Instruções

Instruções

Instruções

...

aritméticas.

lógicas.

de desvio condicional.

de desvio incondicional.

Vimos exemplos destes tipos de instrução na arquitetura MIPS.

▶

▶

▶

▶

add.

beq.

and.

...

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

4 / 42

.

Na Última Aula. . . (III)

Também vimos que instruções têm formatos específicos.

▶

▶

Esquema de representação.

Define quais e como informações são guardadas na instrução.

Finalmente, discutimos os operandos de uma instrução.

▶

▶

“Parâmetros” da operação a ser executada.

Podem ser, por exemplo, imediatos (constantes numéricas) ou registradores.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

5 / 42

.

Ciclo de Execução de uma Instrução

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

6 / 42

.

Ciclo de Execução de uma Instrução

Um processador funciona em ciclos.

▶

▶

▶

De tempos em tempos, ele executa a mesma sequência de passos.

Potencialmente, com entradas diferentes.

Manipulando as entradas, obtemos os resultados desejados.

Estes ciclos consistem na execução de instruções.

▶

▶

As entradas são os dados.

Mas também as instruções em si.

⋆

Mudando o programa, também mudamos a saída.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

7 / 42

.

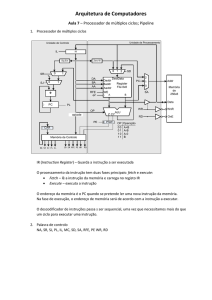

Composição (Básica) do Ciclo de Execução de uma Instrução

Vista na aula passada:

Interpretar Instrução

Buscar Instrução

Executar Instrução

Próxima instrução é buscada na memória.

Instrução é interpretada.

▶

i.e., reconhecem-se o tipo, os operandos, etc.

Operação indicada é executada.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

8 / 42

.

Ciclo de Execução: Mais Detalhadamente

Partes do ciclo mostrado no slide anterior são “complexas”.

▶

▶

Interpretar instrução.

Executar instrução.

Há vários detalhes que ocorrem dentro de cada uma.

Usualmente, definimos o ciclo de execução de uma instrução de forma mais detalhada.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

9 / 42

.

Ciclo de Execução: Mais Detalhadamente (II)

Buscar Instrução

na Memória

Início

Decodificar a

Operação a

Ser Realizada

Buscar

Operandos

(Se Houver)

Armazenar

Resultado

(Se Houver)

Executar a

Operação

Término

Há fases de Busca de Operandos e Armazenamento de Resultado.

▶

No esquema anterior, faziam parte de Interpretar Instrução e Executar Instrução.

Nos próximos slides, discutiremos cada uma destas fases.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

10 / 42

.

Buscar Instrução

Primeiro passo na execução da instrução:

▶

Descobrir qual ela é.

Instruções são armazenadas na MP.

Processador só consegue manipular informações em seus registradores.

▶

▶

Logo, antes de mais nada, processador precisa trazer instrução da MP para algum registrador.

Não um registrador qualquer: o IR.

⋆

Instruction Register.

Em algumas arquiteturas, as instruções têm comprimento fixo.

▶

e.g., MIPS, com instruções de 32 bits.

Em outras, comprimento pode ser variável.

▶

▶

e.g., x86, com instruções de até 15 bytes.

Neste caso, busca da instrução pode não ser tão simples.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

11 / 42

.

Buscar Instrução (II)

A busca de uma instrução, portanto, é basicamente uma leitura da memória.

Como o processador sabe o endereço a ser lido?

▶

▶

▶

Já discutido anteriormente.

Há um outro registrador especial que o armazena.

O Program Counter, ou PC.

⋆

Outros nomes: IC (Instruction Counter ), IP (Instruction Pointer ).

PC tem que ser constantemente atualizado.

▶

▶

▶

Para apontar para a próxima instrução a ser executada.

Normalmente, instruções são executadas na ordem em que aparecem em memória.

Logo, após a leitura da instrução atual, PC já é incrementado.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

12 / 42

.

Decodificar a Instrução

Objetivo geral: entender a instrução.

▶

i.e., entender o que a sequência de bits representa.

Envolve uma série de sub-tarefas:

▶

▶

▶

Qual é a operação a ser realizada?

Qual é o formato da instrução?

Onde estão os operandos?

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

13 / 42

.

Decodificar a Instrução (II)

0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0

0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0

Opcode:

000000(2) = 0(10)

Operando 1:

10001(2)=17(10)

Operando 2:

10010(2)=18(10)

Resultado:

01000(2)=8(10)

Significado:

Operação Lógica

ou

Aritmética

Significado:

Primeiro

Operando está

no Reg. 17

Significado:

Segundo

Operando está

no Reg. 18

Significado:

Armazenar

Resultado

no Reg. 8

Campo não

Utilizado

Nesta

Instrução

(deve sempre

ser 0)

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

Função:

100000(2)=32(10)

Significado:

Operação de

Soma

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

14 / 42

.

Decodificar a Instrução (III)

Primeiro passo, normalmente, é reconhecer o opcode.

▶

▶

▶

Dado o opcode, geralmente, o restante do formato da instrução é conhecido pelo processador.

i.e., processador sabe como tratar os demais bits da instrução.

Adicionalmente, opcode define o tipo de operação a ser realizada.

0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0

Opcode:

000000(2) = 0(10)

Operando 1:

Registrador

Operando 2:

Registrador

Resultado:

Registrador

Deslocamento

Função

Significado:

Operação Lógica

ou

Aritmética

Formato: R

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

15 / 42

.

Decodificar a Instrução (IV)

Uma vez reconhecido o formato da instrução, pode-se descobrir a localização dos

operandos.

▶

▶

▶

Podem estar já em registradores.

Podem ser constantes numéricas especificadas na própria instrução.

Podem ser endereços de memória.

O opcode da instrução determina a semântica dos bits dos operandos.

▶

▶

i.e., o que fazer com eles para encontrar os operandos.

e.g., usar como identificador de um registrador, somar com uma constante para obter um

endereço de memória.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

16 / 42

.

Busca de Operandos

Note que nem toda instrução possui operandos.

Exemplo: instrução nop no x86.

▶

▶

No Operation.

Instrução que não faz “nada”.

⋆

Embora cause efeitos colaterais, como incrementar o PC.

Mas na enorme maioria dos casos, instruções possuirão ao menos um operando.

▶

Sempre verdade no MIPS, por exemplo.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

17 / 42

.

Busca de Operandos (II)

A busca de operandos consiste na tarefa de encontrar os valores sob os quais será

realizada a operação.

Os respectivos bits são passados como entrada de componentes internos do processador.

▶

Como somadores, deslocadores, multiplexadores, . . .

Um caso comum ocorre quando operando está na MP.

▶

▶

Endereço é dado por alguma combinação de valores em registradores e constantes específicas

na própria instrução.

Processador requisita leitura à MP.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

18 / 42

.

Busca de Operandos (III)

Registrador 0

1

Seletor

0

0

Registrador 1

1

0

0

Mux

Outro

Dado

0

1

1

1

Note que mesmo para operandos em

registradores, há algo a se fazer nesta

etapa.

▶

Bits do registrador especificado devem

ser “conectados” ao(s) componente(s)

adequado(s).

Somador

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

19 / 42

.

Busca de Operandos (IV)

Registrador 0

1

0

0

1

0

Seletor

Registrador 1

0

Mux

Imediato

(Instrução)

0

1

1

1

Note ainda que certos casos de busca de

operandos requerem a execução de algum

tipo de processamento.

▶

▶

Comumente, somas.

Algumas vezes deslocamentos

(multiplicações por potências de 2).

Exemplo: instrução load word no MIPS.

Somador

▶

Endereço: valor de registrador +

imediato.

Endereço do

Operando

na MP

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

20 / 42

.

Execução da Operação

Uma vez que os bits dos operandos estejam “conectados” aos componentes corretos do

processador, a instrução é executada.

Esta execução geralmente consiste em algum tipo de operação lógica-aritmética.

▶

▶

▶

Somar dois números.

Calcular um xor bit a bit.

...

Em alguns casos particulares, a operação pode ser simplesmente não fazer nada com o

dado.

▶

▶

e.g., deixar o dado passar.

Exemplo: operações de leitura ou escrita na memória.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

21 / 42

.

Execução da Operação (II)

Esta fase também consiste em “configurar” alguns componentes da CPU.

Determinados componentes precisam de informações adicionais.

▶

▶

Linhas de controle.

Especificam como o componente deve agir sobre os dados.

Exemplos clássicos:

▶

▶

Um multiplexador: sinal na linha de controle seleciona entre primeira e segunda entrada.

Unidade lógica-aritmética: sinal nas linhas de controle selecionam operação lógica aritmética

a ser realizada.

Os sinais destas linhas de controle são geralmente determinados a partir de campos da

instrução.

▶

Como opcode e função, no caso do MIPS.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

22 / 42

.

Armazenamento dos Resultados

Etapa similar à de busca de operandos.

▶

▶

Mas no sentido inverso.

i.e., ao invés de ler valores, estes são armazenados em local apropriado.

Este “local” pode ser um registrador ou algum endereço da MP.

▶

Assim como ocorre na busca de operandos, opcode e formato da instrução determinam o

local.

Também de forma similar, pode ser necessário realizar “processamento” para determinar

exatamente este local.

▶

▶

i.e., algum tipo de conta.

Exemplo clássico: instruções de transferência para a MP do MIPS.

⋆

Soma de registrador com imediato.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

23 / 42

.

Armazenamento dos Resultados

Note ainda que certas instruções não geram dados a serem armazenados.

▶

Ao menos não na MP ou em registradores de propósito geral.

▶

e.g., instruções de desvio.

Única (possível) escrita é no PC.

▶

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

24 / 42

.

Introdução ao Conceito de Pipeline

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

25 / 42

.

Ciclos de CPU vs. Instruções

Processadores operam em ciclos.

Duração de um ciclo do processador é determinada pela frequência do seu clock.

▶

Clock de 1 GHz rightarrow 1 bilhão de ciclos por segundo.

Pergunta: quantas instruções um processador operando a 1 GHz de clock executa

por segundo?

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

26 / 42

.

Ciclos de CPU vs. Instruções

Processadores operam em ciclos.

Duração de um ciclo do processador é determinada pela frequência do seu clock.

▶

Clock de 1 GHz rightarrow 1 bilhão de ciclos por segundo.

Pergunta: quantas instruções um processador operando a 1 GHz de clock executa

por segundo?

▶

▶

▶

▶

Resposta: depende!

Pode ser exatamente 1 bilhão.

Pode ser menos.

Pode ser mais.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

26 / 42

.

Ciclos de CPU vs. Instruções

Por que depende?

▶

É possível projetar um processador que execute exatamente uma instrução a cada ciclo.

⋆

▶

O que veremos nas próximas aulas.

Mas há vantagens em quebrar a execução de uma instrução em vários ciclos de clock.

⋆

⋆

⋆

Reutilização de componentes.

Permitir que instruções mais simples levem menos tempo.

Permitir paralelismo.

Voltaremos a este ponto em aulas posteriores.

▶

Mas por hora, o foco será no último ponto.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

27 / 42

.

Pipeline: Uma Analogia

Vamos usar uma analogia1 para entender o conceito de Pipeline (Patterson):

▶

▶

▶

Suponha uma república de estudantes com 4 pessoas: Ann, Brian, Cathy, Dave.

Toda segunda-feira à noite, eles lavam roupa.

Cada um possui um conjunto de roupas sujas.

⋆

▶

1

Aproximadamente a mesma quantidade de roupas.

Processo composto por 4 etapas:

⋆

Máquina de lavar: 30 minutos.

⋆

Secador/passar roupas: 30 minutos.

⋆

Dobrar roupas: 30 minutos.

⋆

Guardar roupas: 30 minutos.

.

.

.

. . . .

. . . .

. . . .

Adaptado de http://www.cs.berkeley.edu/˜pattrsn/61CS99/lectures/lec25-pipeline.pdf

. .

.

. . . . . . . . . . . . .

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

FAC

.

.

.

.

.

.

.

.

28 / 42

.

Pipeline: Uma Analogia (II)

Solução sequencial:

▶

Cada pessoa aguarda a conclusão da anterior.

6 PM 7

A

Ordem

das

Tarefas

8

9

10

11

12

2 AM

1

3 0 3 0 30 3 0 3 0 3 0 3 0 30 30 30 30 3 0 3 03 0 3 0 3 0

Time

B

C

D

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

29 / 42

.

Pipeline: Uma Analogia (III)

Solução alternativa:

▶

A medida que uma pessoa termina uma fase, a seguinte inicia aquela fase do seu conjunto de

roupas.

6 PM 7

8

9

303 0 30 30 30 30 30

10

11

12

2 AM

1

Time

A

Ordem

das

Tarefas

B

C

D

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

30 / 42

.

Pipeline: Uma Analogia (IV)

Na solução original, cada pessoa demora 4 × 30 = 120 minutos para lavar sua roupa.

Na solução alternativa também.

Mas o tempo total na solução alternativa é muito menor:

▶

210 minutos, contra 480 minutos.

Em outras palavras:

▶

▶

O tempo de resposta para uma única tarefa (pessoa) não mudou.

Mas a vazão do sistema (pessoas atendidas por unidade de tempo) aumentou 118%.

Maior eficiência vem do uso de pipeline.

▶

▶

i.e., executar etapas de tarefas diferentes em paralelo.

Evita que recursos fiquem ociosos.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

31 / 42

.

Ciclo de Execução de Instrução e Pipeline

Podemos aplicar a mesma técnica para a execução de instruções em uma CPU?

▶

Sim, desde que possamos quebrar a tarefa de execução das instruções em

sub-tarefas independentes.

Podemos, por exemplo, considerar as subtarefas como as etapas do ciclo de execução de

uma instrução.

▶

▶

▶

▶

▶

Busca da instrução.

Decodificação.

Busca dos operandos.

Execução.

Armazenamento do Resultado.

Assumindo, é claro, que não haja dependência entre as etapas de instruções

subsequentes.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

32 / 42

.

Ciclo de Execução de Instrução e Pipeline: Eficiência

No jargão de arquitetura de computadores, cada “subtarefa” é chamada de estágio do

pipeline.

Considerando um pipeline com 5 estágios, o estado do pipeline ao longo do tempo:

S1: 1

S2:

S3:

S4:

S5:

1

2

1

3

2

1

4

3

2

1

2

3

4

5

4

3

2

1

5

6 7

5 6

4 5

3 4

2 3

6 7

8

7

6 ...

5

4

8

Tempo

Quantas instruções são executadas por ciclo de clock?

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

33 / 42

.

Ciclo de Execução de Instrução e Pipeline: Eficiência (II)

Com 5 estágios, primeira instrução demora 5 ciclos de clock.

Após este tempo, a cada 1 ciclo, temos mais uma instrução sendo concluída.

Para executar n instruções, precisamos de t = 5 + n − 1 = n + 4 ciclos.

▶

▶

n

Logo, processador executa n+4

instruções por ciclo de clock.

Para n grande, isso é praticamente 1.

Eficiência não é perfeita porque os k primeiros ciclos são gastos enchendo o pipeline.

▶

Onde k é o número de estágios.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

34 / 42

.

Pipeline vs. Monociclo

Na conta anterior, verificamos que com o pipeline quase conseguimos atingir uma

instrução por ciclo.

▶

Então qual é a vantagem de usar um pipeline com vários estágios ao invés de uma solução

que faz tudo em um ciclo só?

A vantagem está na duração do ciclo.

▶

▶

Como, individualmente, cada estágio do pipeline faz algo “simples”, a duração de um ciclo

pode ser curta.

Na implementação monociclo, cada ciclo é mais complexo, longo.

Exemplo: o que é melhor?

▶

▶

Quase uma tarefa por ciclo, com ciclo de 1 ns.

Exatamente uma tarefa por ciclo, com ciclo de 5 ns.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

35 / 42

.

Pipeline e Desvios

A técnica de pipeline é efetiva, desde que mantenhamos o pipeline cheio.

▶

i.e., quando uma instrução está no estágio i, a próxima está no estágio i + 1.

Mas como o processador sabe qual é a próxima instrução?

▶

▶

A princípio, uma tarefa fácil.

Programas são sequências de instruções armazenadas em memória.

⋆

Também de forma sequencial.

Mas há um caso especial: as instruções de desvio.

▶

Próxima instrução pode estar em alguma posição diferente.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

36 / 42

.

Pipeline e Desvios (II)

Suponha que uma instrução de desvio chegue ao último estágio do pipeline.

Neste ponto, a CPU descobre que será realizado um desvio (ao invés da execução

sequencial).

O que fazer?

▶

▶

▶

Outras instruções já estão no pipeline.

Elas não deveriam ser executadas.

Solução: flush do pipeline.

⋆

⋆

Esvaziamos o pipeline, não permitindo a conclusão das demais instruções.

Recomeçamos com o pipeline vazio a partir do endereço do desvio.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

37 / 42

.

Pipeline e Desvios (III)

S1: 1

S2:

S3:

S4:

S5:

1

2

1

3

2

1

4

3

2

1

2

3

4

5

4

3

2

1

5

6 11 12

5

11

...

4

3

2

6 7 8

Tempo

Flush

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

38 / 42

.

Pipeline e Desvios (IV)

O flush em um pipeline impede que executemos instruções erradas.

▶

▶

Mas desempenho é prejudicado.

Enfrentamos novamente o custo inicial de encher o pipeline.

Lembre-se: há dois tipos de desvios diferentes.

▶

▶

Desvios condicionais.

Desvios incondicionais.

No caso de desvios incondicionais, podemos amenizar o problema:

▶

▶

Se conseguirmos detectar o desvio cedo, precisamos descartar apenas um subconjunto das

instruções já executadas.

O pipeline ainda ficará “meio cheio”.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

39 / 42

.

Pipeline e Desvios (V)

Mas e para desvios condicionais?

▶

▶

Se soubéssemos cedo o resultado da condição, poderíamos usar a mesma estratégia dos

desvios incondicionais.

Mas isso geralmente não é possível.

⋆

⋆

Desvios condicionais são mais complexos.

Precisam chegar a estágios finais do pipeline para sabermos seu resultado.

Não há solução, então?

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

40 / 42

.

Predição de Desvios

Processadores modernos geralmente possuem um branch predictor.

▶

▶

▶

Preditor de desvios.

Tenta “advinhar” o resultado de uma instrução de desvio condicional.

Baseado em histórico.

Quando CPU decta (cedo) a execução de uma instrução de desvio condicional:

▶

▶

▶

Preditor prevê se desvio ocorrerá ou não.

Se preditor diz que desvio não ocorrerá, próxima instrução é colocada no pipeline.

Caso contrário, instrução do endereço de destino é utilizada.

Se o preditor acerta, pipeline continua cheio.

Se o preditor erra, temos que fazer um flush.

▶

E pagar a penalidade de desempenho.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

41 / 42

.

Exercício

Suponha um processador com pipeline de 5 estágios.

▶

▶

▶

▶

Em instruções de desvio condicional, o preditor sempre prevê que o salto não ocorrerá.

Assuma que ao final do quarto estágio a CPU é capaz de determinar o resultado de

instruções de desvio condicional.

Caso o desvio seja tomado, é preciso dar um flush nas três instruções nos estágios anteriores.

Caso contrário, o pipeline continua cheio.

Determine o número médio de instruções executadas por ciclo de clock considerando:

▶

▶

▶

20% das instruções são de desvio condicional.

30% destes desvios ocorrem.

Não há nenhuma outra fonte de ineficiência do pipeline.

.

Diego Passos (UFF)

Ciclo de Execução; Intro. ao Pipeline

.

.

.

.

.

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

FAC

.

.

.

.

.

.

.

42 / 42

.