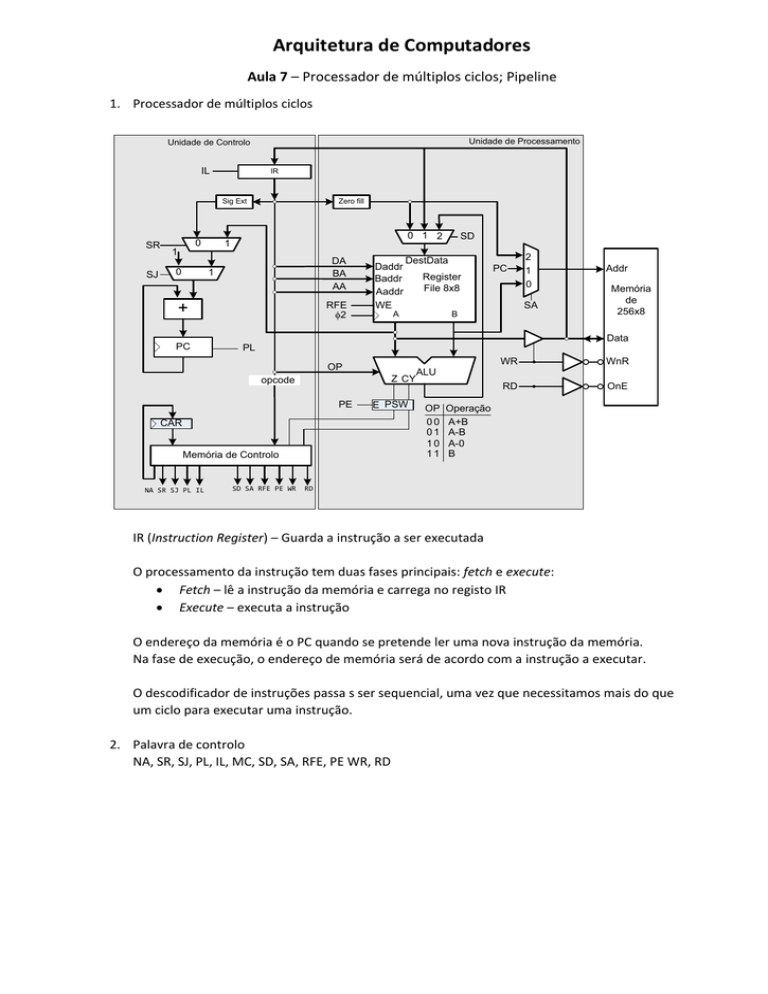

Arquitetura de Computadores

Aula 7 – Processador de múltiplos ciclos; Pipeline

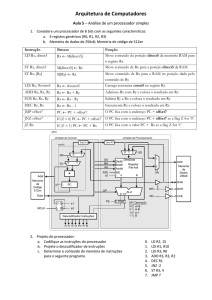

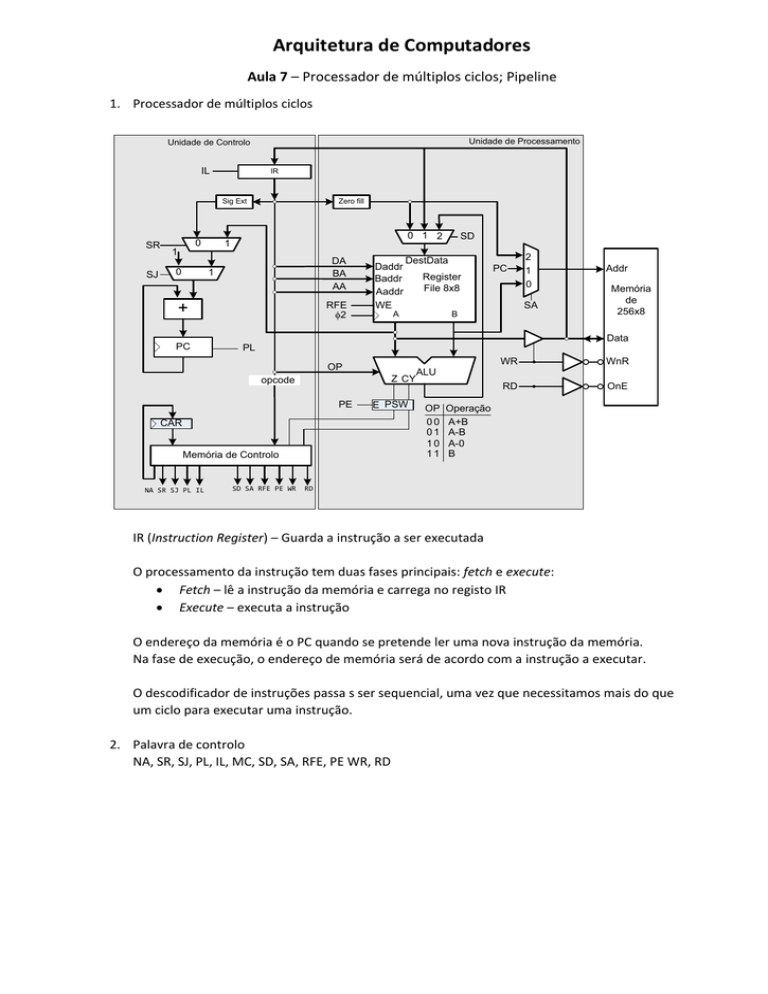

1. Processador de múltiplos ciclos

Unidade de Processamento

Unidade de Controlo

IL

IR

Sig Ext

SR

SJ

0

0 1 2

1

1

0

Zero fill

DA

BA

AA

1

RFE

f2

+

PC

Daddr

Baddr

Aaddr

WE

DestData

Register

File 8x8

PC

2

1

0

SA

A

B

Addr

Memória

de

256x8

Data

PL

OP

Z CY

opcode

PE

E PSW

CAR

Memória de Controlo

NA SR SJ PL IL

SD

SD SA RFE PE WR

WR

WnR

RD

OnE

ALU

OP

00

01

10

11

Operação

A+B

A-B

A-0

B

RD

IR (Instruction Register) – Guarda a instrução a ser executada

O processamento da instrução tem duas fases principais: fetch e execute:

Fetch – lê a instrução da memória e carrega no registo IR

Execute – executa a instrução

O endereço da memória é o PC quando se pretende ler uma nova instrução da memória.

Na fase de execução, o endereço de memória será de acordo com a instrução a executar.

O descodificador de instruções passa s ser sequencial, uma vez que necessitamos mais do que

um ciclo para executar uma instrução.

2. Palavra de controlo

NA, SR, SJ, PL, IL, MC, SD, SA, RFE, PE WR, RD

3. Descodificação da instrução

Circuito sequencial:

Entradas: instrução (opcode, flags, endereço memória de controlo)

Saídas: palavra de controlo

CAR

0

1

1

1

1

1

1

1

1

1

1

1

1

1

instr

---LD rx, direct5

LD rx, [ry]

ST rx, [ry]

LDi, Rx, #const5

ADD rz, rx, ry

SUB rz, rx, ry

DEC rx, rx

JMP offset7

JNZ offset7

JC offset7

JZ rx

Z

0

1

-

C

0

1

-

NA

1

0

0

0

0

0

0

0

0

0

0

0

0

0

SR

0

0

0

1

SJ

0

1

1

1

1

PL

1

0

0

0

0

0

0

0

1

1

0

0

1

1

IL

1

0

0

0

0

0

0

0

0

0

0

0

0

0

SD

-01

01

-00

10

10

10

-------

SA

01

10

00

00

-----------

RFE

0

1

1

0

1

1

1

1

0

0

0

0

0

0

PE

0

0

0

0

0

1

1

1

0

0

0

0

0

0

4. Processador com pipeline

Para melhorar o desempenho, usamos a técnica de pipeline.

Consideremos o exemplo simples do processador de 2 ciclos anterior.

Ciclos de clock

1

IF

2

3

4

5

6

7

8

9

EX

(add r2,r1,r3)

IF

EX

(ldi r1, #0)

IF

EX

(ld r2, 5)

stall

IF

EX

(sub r1,r2,r1)

IF

EX

(jz rx )

stall??

IF

Desempenho sem pipeline: 6 ciclos x 2 = 12 ciclos de clock

Desempenho ideal com pipeline: 7 ciclos (nº instruções + nº ciclos encher pipeline)

Desempenho com pipeline com stalls: 9 ciclos

EX

WR

0

0

0

1

0

0

0

0

0

0

0

0

0

0

RD

1

1

1

0

0

0

0

0

0

0

0

0

0

0