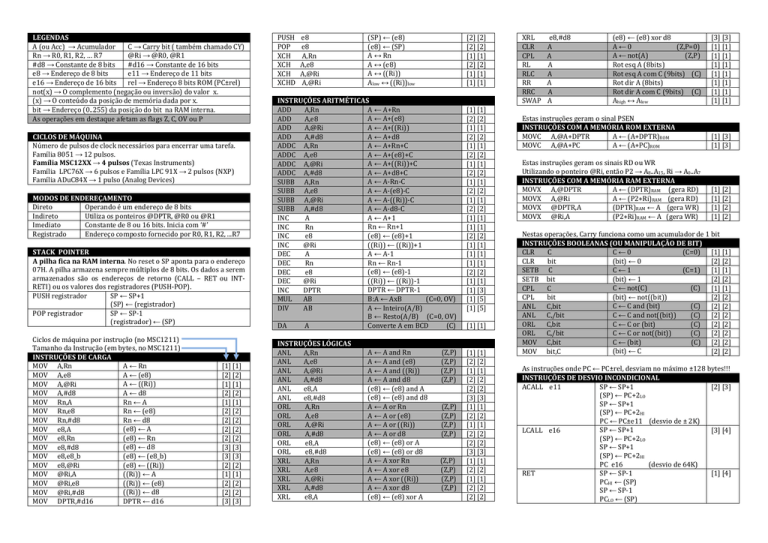

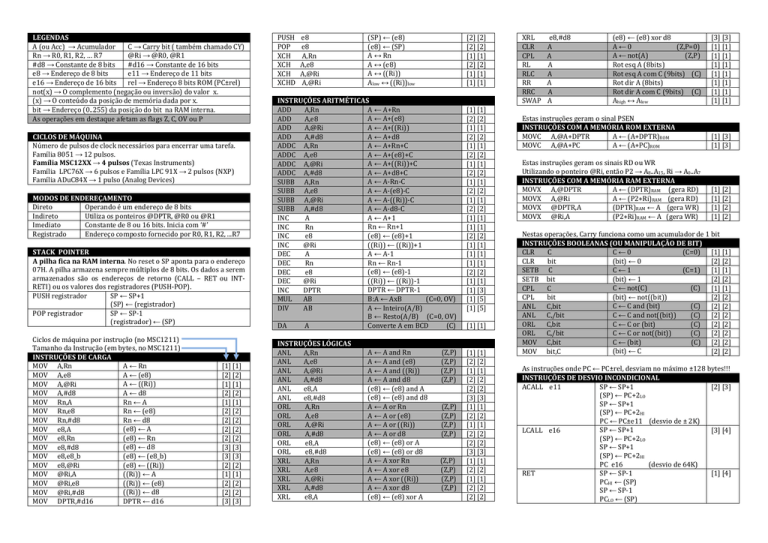

LEGENDAS

A (ou Acc) → Acumulador

C → Carry bit ( também chamado CY)

Rn → R0, R1, R2, … R7

@Ri → @R0, @R1

#d8 → Constante de 8 bits

#d16 → Constante de 16 bits

e8 → Endereço de 8 bits

e11 → Endereço de 11 bits

e16 → Endereço de 16 bits

rel → Endereço 8 bits ROM (PC±rel)

not(x) → O complemento (negação ou inversão) do valor x.

(x) → O conteúdo da posição de memória dada por x.

bit → Endereço (0..255) da posição do bit na RAM interna.

As operações em destaque afetam as flags Z, C, OV ou P

CICLOS DE MÁQUINA

Número de pulsos de clock necessários para encerrar uma tarefa.

Família 8051 → 12 pulsos.

Família MSC12XX → 4 pulsos (Texas Instruments)

Família LPC76X → 6 pulsos e Família LPC 91X → 2 pulsos (NXP)

Família ADuC84X → 1 pulso (Analog Devices)

MODOS DE ENDEREÇAMENTO

Direto

Operando é um endereço de 8 bits

Indireto

Utiliza os ponteiros @DPTR, @R0 ou @R1

Imediato

Constante de 8 ou 16 bits. Inicia com ‘#’

Registrado

Endereço composto fornecido por R0, R1, R2, ...R7

STACK POINTER

A pilha fica na RAM interna. No reset o SP aponta para o endereço

07H. A pilha armazena sempre múltiplos de 8 bits. Os dados a serem

armazenados são os endereços de retorno (CALL – RET ou INTRETI) ou os valores dos registradores (PUSH-POP).

SP ← SP+1

PUSH registrador

(SP) ← (registrador)

SP ← SP-1

POP registrador

(registrador) ← (SP)

Ciclos de máquina por instrução (no MSC1211)

Tamanho da Instrução (em bytes, no MSC1211)

INSTRUÇÕES DE CARGA

A ← Rn

MOV A,Rn

A ← (e8)

MOV A,e8

A ← ((Ri))

MOV A,@Ri

A ← d8

MOV A,#d8

Rn ← A

MOV Rn,A

Rn ← (e8)

MOV Rn,e8

Rn ← d8

MOV Rn,#d8

(e8) ← A

MOV e8,A

(e8) ← Rn

MOV e8,Rn

(e8) ← d8

MOV e8,#d8

(e8) ← (e8_b)

MOV e8,e8_b

(e8) ← ((Ri))

MOV e8,@Ri

((Ri)) ← A

MOV @Ri,A

((Ri)) ← (e8)

MOV @Ri,e8

((Ri)) ← d8

MOV @Ri,#d8

DPTR ← d16

MOV DPTR,#d16

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[2] [2]

[2] [2]

[2] [2]

[3] [3]

[3] [3]

[2] [2]

[1] [1]

[2] [2]

[2] [2]

[3] [3]

PUSH

POP

XCH

XCH

XCH

XCHD

e8

e8

A,Rn

A,e8

A,@Ri

A,@Ri

(SP) ← (e8)

(e8) ← (SP)

A ↔ Rn

A ↔ (e8)

A ↔ ((Ri))

Alow ↔ ((Ri))low

[2] [2]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[1] [1]

INSTRUÇÕES ARITMÉTICAS

A ← A+Rn

ADD

A,Rn

A ← A+(e8)

ADD

A,e8

A ← A+((Ri))

ADD

A,@Ri

A ← A+d8

ADD

A,#d8

A ← A+Rn+C

ADDC A,Rn

A ← A+(e8)+C

ADDC A,e8

A ← A+((Ri))+C

ADDC A,@Ri

A ← A+d8+C

ADDC A,#d8

A ← A-Rn-C

SUBB A,Rn

A ← A-(e8)-C

SUBB A,e8

A ← A-((Ri))-C

SUBB A,@Ri

A ← A-d8-C

SUBB A,#d8

A ← A+1

INC

A

Rn ← Rn+1

INC

Rn

(e8) ← (e8)+1

INC

e8

((Ri)) ← ((Ri))+1

INC

@Ri

A ← A-1

DEC

A

Rn ← Rn-1

DEC

Rn

(e8) ← (e8)-1

DEC

e8

((Ri)) ← ((Ri))-1

DEC

@Ri

DPTR ← DPTR-1

INC

DPTR

B:A ← AxB

(C=0, OV)

MUL

AB

A ← Inteiro(A/B)

DIV

AB

B ← Resto(A/B) (C=0, OV)

DA

A

Converte A em BCD

(C)

INSTRUÇÕES LÓGICAS

ANL

A,Rn

ANL

A,e8

ANL

A,@Ri

ANL

A,#d8

ANL

e8,A

ANL

e8,#d8

ORL

A,Rn

ORL

A,e8

ORL

A,@Ri

ORL

A,#d8

ORL

e8,A

ORL

e8,#d8

XRL

A,Rn

XRL

A,e8

XRL

A,@Ri

XRL

A,#d8

XRL

e8,A

A ← A and Rn

A ← A and (e8)

A ← A and ((Ri))

A ← A and d8

(e8) ← (e8) and A

(e8) ← (e8) and d8

A ← A or Rn

A ← A or (e8)

A ← A or ((Ri))

A ← A or d8

(e8) ← (e8) or A

(e8) ← (e8) or d8

A ← A xor Rn

A ← A xor e8

A ← A xor ((Ri))

A ← A xor d8

(e8) ← (e8) xor A

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

(Z,P)

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[1] [1]

[1] [1]

[2] [2]

[1] [1]

[1] [1]

[1] [1]

[2] [2]

[1] [1]

[1] [3]

[1] [5]

[1] [5]

[1] [1]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[2] [2]

[3] [3]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[2] [2]

[3] [3]

[1] [1]

[2] [2]

[1] [1]

[2] [2]

[2] [2]

XRL

CLR

CPL

RL

RLC

RR

RRC

SWAP

e8,#d8

A

A

A

A

A

A

A

(e8) ← (e8) xor d8

A←0

(Z,P=0)

A ← not(A)

(Z,P)

Rot esq A (8bits)

Rot esq A com C (9bits) (C)

Rot dir A (8bits)

Rot dir A com C (9bits) (C)

Ahigh ↔ Alow

[3] [3]

[1] [1]

[1] [1]

[1] [1]

[1] [1]

[1] [1]

[1] [1]

[1] [1]

Estas instruções geram o sinal PSEN

INSTRUÇÕES COM A MEMÓRIA ROM EXTERNA

A ← (A+DPTR)ROM

MOVC A,@A+DPTR

A ← (A+PC)ROM

MOVC A,@A+PC

[1] [3]

[1] [3]

Estas instruções geram os sinais RD ou WR

Utilizando o ponteiro @Ri, então P2 → A8..A15, Ri → A0..A7

INSTRUÇÕES COM A MEMÓRIA RAM EXTERNA

A ← (DPTR)RAM (gera RD)

MOVX A,@DPTR

A ← (P2+Ri)RAM (gera RD)

MOVX A,@Ri

(DPTR)RAM ← A (gera WR)

MOVX @DPTR,A

(P2+Ri)RAM ← A (gera WR)

MOVX @Ri,A

[1] [2]

[1] [2]

[1] [2]

[1] [2]

Nestas operações, Carry funciona como um acumulador de 1 bit

INSTRUÇÕES BOOLEANAS (OU MANIPULAÇÃO DE BIT)

C←0

(C=0) [1] [1]

CLR

C

(bit) ← 0

CLR

bit

[2] [2]

C←1

(C=1) [1] [1]

SETB C

(bit) ← 1

SETB bit

[2] [2]

C ← not(C)

(C) [1] [1]

CPL

C

(bit) ← not((bit))

CPL

bit

[2] [2]

C ← C and (bit)

(C) [2] [2]

ANL

C,bit

C ← C and not((bit))

(C) [2] [2]

ANL

C,/bit

C ← C or (bit)

(C) [2] [2]

ORL

C,bit

C ← C or not((bit))

(C) [2] [2]

ORL

C,/bit

C ← (bit)

(C) [2] [2]

MOV C,bit

(bit) ← C

MOV bit,C

[2] [2]

As instruções onde PC ← PC±rel, desviam no máximo ±128 bytes!!!

INSTRUÇÕES DE DESVIO INCONDICIONAL

SP ← SP+1

ACALL e11

[2] [3]

(SP) ← PC+2LO

SP ← SP+1

(SP) ← PC+2HI

PC ← PC±e11 (desvio de ± 2K)

SP ← SP+1

LCALL e16

[3] [4]

(SP) ← PC+2LO

SP ← SP+1

(SP) ← PC+2HI

PC e16

(desvio de 64K)

SP ← SP-1

RET

[1] [4]

PCHI ← (SP)

SP ← SP-1

PCLO ← (SP)

RETI

AJMP

LJMP

SJMP

JMP

e11

e16

rel

@A+DPTR

Retorno de Interrupção

PC ← PC±e11 (desvio de ± 2K)

PC ← e16

(desvio de 64K)

PC ← PC±rel

PC ← (A+DPTR)ROM

INSTRUÇÕES DE DESVIO CONDICIONAL

Se bit = 1 então PC ← PC±rel

JB

bit,rel

Se bit = 0 então PC ← PC±rel

JNB

bit,rel

JBC

bit,rel

Se bit = 1, então

PC ← PC±rel e bit ← 0

Se Z=1 então PC ← PC±rel

JZ

rel

Se Z=0 então PC ← PC±rel

JNZ

rel

Se C=1 então PC ← PC±rel

JC

rel

Se C=0 então PC ← PC±rel

JNC

rel

Se A≠(e8) : PC ← PC±rel

(C)

CJNE

a,e8,rel

Se A≠d8 : PC ← PC±rel

(C)

CJNE

a,#d8,rel

Se Rn≠d8 : PC ← PC±rel

(C)

CJNE

Rn,#d8,rel

Se ((Ri))≠d8 : PC ← PC+rel (C)

CJNE

@Ri,#d8,rel

Rn ← Rn-1

DJNZ

Rn,rel

Se Rn≠0 então PC ← PC±rel (Z)

(e8) ← (e8)-1

DJNZ

e8,rel

Se (e8)≠0 então PC ← PC±rel (Z)

NOP

Não faz nada

[1] [4]

[2] [3]

[3] [4]

[2] [3]

[1] [3]

[3] [4]

[3] [4]

[3] [4]

[2] [3]

[2] [3]

[2] [3]

[2] [3]

[3] [4]

[3] [4]

[3] [4]

[3] [4]

[2] [3]

[3] [4]

[1] [1]

AC → Auxiliar Carry (transporte do bit 3 para o bit 4)

RS1/RS0 → Controla o banco de registradores (R0..R7)

OV → Overflow (para números sinalizados de -128...+127)

P → Bit de paridade par (para que o total de “1s” seja par)

Utiliza os registradores IE, IP e TCON.3 ... TCON.0

INTERRUPÇÕES

Endereço

0000H

Interrupção

Prioridade

Reset

++

Nenhum

INT0

+

EA, EX0, IT0, IE0,

PX0

000BH

TIMER0

EA, ET0, TF0, PT0

INT1

EA, EX1, IT1, IE1,

PX1

TIMER1

EA, ET1, TF1, PT1

0013H

Modo operação (M1M0): 0, 1 ou 2

Modo0 → Prescaler (÷32) + Contador de 8 bits.

Modo1 → Contador de 16 bits.

Modo2 → Contador de 8 bits autocarregável.

PROGRAMA DE TESTE (ASSEMBLY) – MSC1211

led

EQU

93H

; endereço do bit P1.3

X

EQU

244

Y

EQU

255

ORG

0000H

LJMP

main

001BH

main:

0023H

-

EA, ES, RI, TI, OS

Se EA = 0 então todas as interrupções estão desativadas

INTx → Ativada por borda (ITx = 0) ou por nível (ITx = 1)

INTERRUPÇÕES

delay:

loop1:

loop2:

ORG

0100H

CPL

led

LCALL delay

LJMP

main

MOV

MOV

NOP

DJNZ

DJNZ

RET

R6,#X

R7,#Y

EX1

ET0

EX0

IP (Interrupt Priority)

-

PX1

PT0

PX0

OS

PT1

TMOD (Timer Mode)

GATE

C/T

M1

Timer 1

M0

GATE

C/T

M1

Timer 0

M0

TCON (Timer Control)

TF1

TR1

TF0

Timer1 & Timer0

TR0

IE1

IT1

IE0

INT1 & INT0

IT0

F=2MHz

; Alterna o valor do pino led

; delay 0.5s

; Supondo f = 2MHz → Tciclo = 2us

; Nciclos = 10+X(5+4Y)

; Nciclos = 250.000

R7,loop2

R6,loop1

PROGRAMA DE TESTE (C) – MSC1211

#include <MSC1211.h>

#include <stdio.h>

REGISTRADORES IMPORTANTES

IE (Interrupt Enable)

EA

ES

ET1

PSW (Processor Status Word)

CY

AC

RS1

RS0

OV

C (ou CY) → Carry bit (transporte do bit 7 para o bit 8)

Bits de Controle

0003H

Serial

Condição dos Registradores e/ou bits no reset do µC

CONDIÇÕES NO RESET

PC ← 0

IE ← 0xx0000

A←0

IP ← xxx00000

B←0

PSW ← 00x000x0

SP ← 07H

SCON ← 0, SBUF ← xxxxxxxx

DPTR ← 0

PCON ← 0xxxxxxx

P0..P3 ← FFH

TMOD ← 0

TCON ← 0

TH1, TL1, TH0, TL0 ← 0

TIMER0 e TIMER1

F=2MHz

sbit at 0x93 led;

// declaração do pino P1.3

void delay(unsigned int i);

void main(void)

{

While(1)

{

led = !(led);

delay(50000); // delay de aproximadamente 250.000 ciclos

}

}

void delay(unsigned int i)

{

while(i) i--;

}

P

Júlio César Marques de Lima – [email protected]