Universidade do Estado de Santa Catarina

CCT – Centro de Ciências Tecnológicas

Amplificadores de Múltiplos Estágios

Acadêmicos:

Chrystian Lenon Remes

Fernando Raul Esteche Pedrozo

Gilmar Nieckarz

Hallan William Veiga

Leandro Santos Monteiro

Professor:

Celso José Faria de Araújo

Disciplina:

Eletrônica Analógica I

2011/01

Joinville - SC

2

Introdução

Trata da criação de circuitos amplificadores mais complexos, e que normalmente resultam em um

maior ganho, podendo ser de tensão ou de corrente.

Como demonstrado na figura abaixo, em amplificadores de múltiplos estágios, a entrada de um

estágio é a saída do próximo.

Saída de um, entrada de outro

Além disso, para que se mantenha o máximo de tensão nos estágios, o estágio de entrada deve

possuir alta impedância. Da mesma forma, o estágio de saída deve possuir baixa impedância de

saída, para que a maior parte da tensão fique na carga e não nos transistores.

Outro cuidado bastante importante é o de manter todos os transistores na região ativa, sem um

transistor comprometer o outro.

Conforme podemos ver na figura acima, temos uma tensão de entrada Vi. Dessa tensão, vai

primeiramente para o primeiro estágio. Este estágio possui uma alta impedância de entrada, como

comentado anteriormente, e normalmente apresenta baixo ganho. Os estágios intermediários,

representado na figura acima pelo 2º estágio, possui funcionalidades como por exemplo a mudança

de nível, e por último, o estágio de saída possui uma baixa impedância e normalmente fornece um

alto ganho.

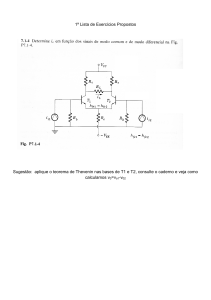

1. Amplificador em Cascata acoplado capacitivamente

O amplificador acoplado capacitivamente é a mais simples é mais largamente utilizado ,

onde a tensão CA (corrente alternada) na saída do primeiro estágio aplicada ao terminal de

entrada do próximo estágio por meio de um capacitor de acoplamento como ilustrado na

figura 1. O capacitor de acoplamento possibilita a isolação CC entre estágios e, portanto,

mantém as condições de polarização inalterada. A reatância capacitiva do capacitor de

acoplamento em freqüências médias deve ser suficientemente baixa a fim de que a

transferência do sinal se faça sem perda e sem distorção de fase.

3

Figura 1

Exemplo: Para o a figura acima ache o ganho de tensão.

Análise DC:

Considerando que os capacitores abrem, temos a figura a seguir:

Figura 2 a

Figura 2 b

Fazendo thevenin na figura 2 a temos:

V

V = R = R // R 4

Fazendo por malha obtemos as seguintes equações:

V = I . R + V + I . R I = mas

Então:

I =

V =R . I

) ;

;

I =

)

V = V − R I

;

)

; I = V = V − R I

Da mesma maneira calculamos as correntes e tensões na figura 2 b.

Análise AC:

Considerando que o capacitor curtam para pequenas variações de sinais e mudando para o circuito

equivalente π e desconsiderando o r tem-se:

5

Seja: R = R // R ; R = R // R //R

R Sendo o a saída do primeiro estágio e o uma entrada qualquer sem considerar a

resistência do gerador. Então o ganho do primeiro estágio será:

!

! = !" = -%& (R // r )

#$

No segundo estágio temos o como a tensão de entrada e o '()

'() como tensão de saída.

Então o ganho do segundo estágio será:

!

! = !*+, = -%& (R // R )

" Multiplicando os dois ganhos temos:

!

!

! . ! = !" . !*+, = %& (R // r )%&(R // R )

#$

" O ganho total será:

!- =%& %&(R // r ) (R // R ).

." // 0 " // 6

Exemplo: Encontrar o ganho do circuito abaixo (considere VBE =0,7V ; 1=200 ; VT =

26 mV)

Análise DC: Polarização

É igual para os dois circuitos, já que estão polarizados com os mesmos parâmetros:

Temos que:

7

23

6

23

:;

/1/

<; 0,7 1@A 1:; 6 0

/2/

45

7,95

Substituindo /1/ em /2/ encontramos:

:; 6 1,99. 104 <; 6 4,7<

:D 6 4EFG 6 6,5J

Ganho do Segundo Estágio: (AV2)

Utilizando o equivalente T para o segundo estágio:

Temos que:

<KK 6 2,2@. M. NG /1/

NG 6

2#OO

PQ

/2/

Substituindo /1/ em /2/ encontramos:

2 OO

2 6 ROO 6 336,78 V/V

2

#

8

Ganho do Primeiro Estágio: (AV1)

Utilizando o equivalente T para o primeiro estágio:

A resistência de entrada do segundo estágio Re2 é a resistência vista pela entrada do

circuito do segundo estágio de amplificação:

Calculando pela resistência equivalente de Thévenin:

9

UQ

6 45 7,95 MNG NG

NG 6 P 6 V,4

Q

/1/

/2/

Substituindo /1/ em /2/ encontramos:

WG 6 957,09J

Cálculo do Ganho do Primeiro Estágio: (AV1)

Agora, com a resistência

sistência de entrada do segundo estágio calculada, calcularemos o

ganho do primeiro estágio:

<K 6 M2,2@//WG NG

/1/

10

NG 6

2O

PQ

/2/

Substituindo /1/ em /2/ encontramos:

2 6

<K

6 102,10</<

<K

Logo, o Ganho total será dado por:

XY 6 XYZ ∗ XY\ 6 ]^]_`, \Y/Y

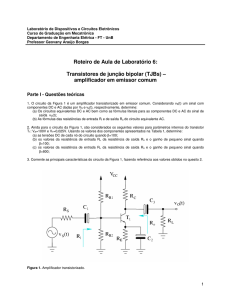

2. Amplificadores em cascata diretamente acoplados

Neste tipo de acoplamento, os dois transistores estão diretamente acoplados,

fazendo com que o ganho seja maior do que se houvesse somente um Transistor.

Diferentemente do caso em que os transistores estão acoplados por um capacitor, a

polarização deve ser analisada com os dois transistores simultaneamente.

Exemplo de conexão em cascata diretamente acoplada:

11

Exercício: encontrar o ganho do circuito acima: (considere VBE =0,6V ; A=100 ; VT =

25 mV)

Análise DC: Polarização

Temos que:

V23

75

2

3

6 5

:;

/1/

:;

<; 0,6 1,4@A 1:

; 60

/2/

Substituindo /1/ em /2/ encontramos:

:; 6 9,048 a

<; 6 1,88

1

<

:D 6 0,9138 E

V23

5

FG 6 27,36 J

6 :; A:;

/3/

;

<; 0,6 1,7@A 1:

; 6 0 /4/

Substituindo /3/ em /4/ encontramos:

:; 6 20,67 a

<; 6 4,15

4

<

:D 6 2,088 E

FG 6 11,98

11

J

Análise AC:

Substituindo capacitores por curto-circuito

curto circuito e os transistores pelo seu circuito

equivalente T:

2#$

6 NG

PQ

Q

Q PQ ,95//5

5

/1/

MNG NG 6 MNG

/2/

<'() 6 1,7@//1@NG

/3/

Substituindo /1/ em /2/ encontramos:

b2#$

PQ

6 NG M 1 PQ ,95//5

5

/4/

Substituindo /4/ em /3/ encontramos:

! 6

<

∝ 1,7@//1@

6

<'() F M 1 FG 1,7@//1@ G

2@

Xd 6 e_, f Y/Y

13

3. Amplificador Cascode

•

•

•

O amplificador cascode é um tipo de amplificador em cascata diretamente acoplado

(transistores em série).

Para acoplar diretamente esses dois estágios, conecta-se o emissor do segundo estágio

no coletor do primeiro, de forma que a mesma corrente flua através de ambos os

transistores. Também obtêm-se a polarização de base através de um divisor de tensão

composto por três resistores.

A idéia básica é combinar a alta impedância de entrada com baixo ganho de tensão no

estágio 1 (um).

Versão acoplada bipolar do cascode

Depois, conexão entre o emissor do segundo estágio para o coletor do primeiro estágio.

(Mesmos passos do exemplo anterior).

Sejam os passos do amplificador cascata:

Sejam as tensões do Coletor de Q1 e no Emissor de Q2 iguais, chegamos em

E chegamos na forma mais comum de desenho de um amplificador cascode:

14

Sendo que os capacitores e os resistores fazem parte do circuito para manter a polarização dos

transistores (desconsiderando a carga e a tensão do gerador).

O circuito do amplificador cascode com capacitores e resistores para polarização:

Os circuitos amplificadores cascode MOS e BJT desconsiderando os detalhes de polarização:

15

Transistor cascode

Podemos utilizar o modelo T para pequenos sinais para a análise AC, e perceberemos no

exemplo que a análise fique muito simples fazendo uso disso:

Se analisarmos um datasheet de um cascode, modelo MBC13916T1 da Freescale, verificamos

que no encapsulamento já existem os dois transistores polarizados dessa forma, conforme a

figura abaixo retirado o datasheet:

16

Exemplo: Calcule o ganho do amplificador cascode da figura abaixo:

Análise DC:

17

Algumas considerações através da análise do circuito:

:g 6 A. :;

(1)

:g = A. :;

(2)

:g = M. :D

(3)

:g = M. :D

(4)

:g = :D

(5)

Fazendo então a análise das correntes nos transistores:

:D = :; + :g

(6)

:D = :; + :g

(7)

:g = :; + :g

(7)

Substituindo (5) → (7)

Fazendo (7) + (6)

:D = :; + :; + :g

(8)

hi

b

(8)

Substituindo (1), (2), (3) → (8)

=

hi

+

hi

+ :g

:g . j − k = :g . j + 1k

b

(9)

18

b

:g . j − k = :g . j + 1k

(10)

Seja A = 200 para os dois transistores, temos:

:g . 1,005 − 0,005 = :g . 0,005 + 1

lmZ = lm\ . Z, nn`

(11)

(12)

Fazendo (1)/(2):

hi

hi

h

6 . h3

(13)

3

lo\ . Z, nn` = loZ

(14)

E fazendo (3)/(4):

hi

hi

b hp

b hp

6 .

(15)

lq\ . Z, nn` = lqZ

(16)

Mas temos a consideração de (5), e então:

l

qZ

lq\ 6 lm\ . Z, nn` = Z,nn`

(17)

E temos que, fazendo (17) → (7)

:g . 1,005 = :; + :g

(18)

:g . 1,005 − 1 = :;

(19)

lm\ . n, nn` = lo\

(20)

Temos então que :; ≪ :g . Fazendo o divisor de tensão no circuito, para determinar a tensão

na base dos transistores Q2 e Q1, respectivamente, com o divisor nas resistências

W; , W; , W;s :

`.et^.ut

Zn.]t

^.ut

^.ut

Yo\ = e._t`.et^.ut . Ymm = Zu.Zt . Z_ = Zn, _^Y

YoZ 6 e._t`.et^.ut . Ymm = Zu.Zt . Z_ = ^, f`Y

(21)

(22)

Aproximando :D v:D , pois como visto em (17), e da mesma forma com (12) e (14):

h

p

:D 6 ,4

≅ :D

(23)

:g = :g . 1,005 ≅ :g

(24)

:; . 1,005 = :; ≅ :;

(25)

E fazendo a análise de malha do circuito:

19

−<; + 0,7 + WD . :D = 0

lqZ =

YoZ n,u

xq

=

^,f`n,u

Z,Zt

= ], _e^yX

E sabemos que aproximamos em (23), (24) e (25).

Análise AC:

Para a análise AC teremos o seguinte circuito:

E arrumando:

E trocando os transistores pelo modelo equivalente:

(26)

(27)

20

Onde temos que os valores em Q2 terão o 2 após as nomenclaturas, como zG , FG , e os do

transistor Q1 serão zG , FG .

Procedendo aos cálculos, e aproximando :D = :D, pois como visto em (17):

h

p

:D = ,4

≅ :D

(28)

E então:

2

2

FG = FG = h { = h { = 6,47

p

p

(29)

h

Calculando o parâmetro %& = 2i , mas sabemos de (24) e de (5) que:

{

|yZ = |y\ =

lmZ

Y}

=

lm\

Y}

=

lqZ

Y}

=

lq\

Y}

= |y = n, Z`^`e

(30)

Tirando o ganho do circuito, no estágio 1:

XYZ 6

Y~Z

YZ

6

|y .dZ .\

dZ

= −|y . \ = −Z YY

(31)

Tirando o ganho do circuito, no estágio 2:

Y

XY\ 6 Y~\ 6

~Z

|y .d\ .xm

d\

= |y . xm = \u_, \n_ YY

(32)

E o ganho total do circuito:

X

Y

Y

XY 6 XY\ 6 Y~\ . Y~Z =

YZ

~Z

Z

Y~\

YZ

= −\u_, \n_ YY

(33)

21

E temos um grande ganho de tensão nesse caso. Como percebemos, o estágio 1 (Q1) não

possui ganho nenhum, apenas inverte a tensão. No entanto, o estágio 2 (Q2), chamado de

Transistor Cascode, possui um alto ganho de tensão.

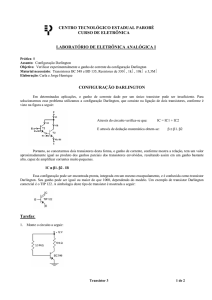

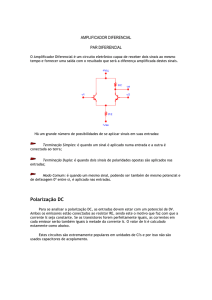

4. Amplificador Darlington

O amplificador Darlington é um amplificador de múltiplos estágios, onde o estágio de

saída de corrente do emissor de um transístor é ligado a base de outro transístor.

Desta forma :D será igual a :; , e esta corrente será novamente amplificada pelo

outro transístor. Podemos demonstrar isto usando as equações do transístor, pois:

:D 6 A 1):; mas :D = :; , então :D = (A + 1):; , por fim, temos:

lq\ = (1Z + Z)(1\ + Z)loZ

Como em geral A assume valores muito maiores que 1, e temos uma multiplicação

destes valores, os termos unitários podem ser desconsiderados, fazendo com que:

lq\ 6 1 loZ

Onde 1 6 1Z 1\ e com isso, a corrente no coletor será aproximada pela corrente de

emissor.

Desta forma, o par darlington pode ser encarado como um único transístor de

constante A

, e com duas quedas sucessivas de tensão de base para emissor, tendo

então um novo <;D 6 1.6<, que é o dobro da queda de tensão vista para um único

transístor (caso esta seja de 0.8V). A figura a seguir ilustra a equivalência do circuito

composto de um par darlington e um circuito composto de apenas um transístor de

características equivalentes:

Transistor equivalente do par darlington

Se estivermos em análise AC, a mesma ideia vista acima é válida, e os dois transístores

do par darlington podem ser vistos como um único transístor, fazendo com que os

cálculos para ganho, resistência de entrada e saída sejam os mesmos.

22

Modelo equivalente do par darlington para AC

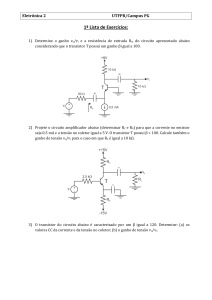

Exemplo 1:

Dado o circuito abaixo com um par Darlington, calcule as correntes de polarização em

DC. Em seguida construa o equivalente em AC, levando em conta que as capacitâncias

podem ser consideradas suficientemente altas e considerando uma resistência de

entrada, com F 6 5 J. (A

6 A A 6 8000 v A 6 A v <;D 6 <;D 6 0.8 <.

Circuito referente ao exemplo 1

Solução: Analise DC

Em DC, abrimos os capacitores, e devemos agora achar as correntes :; , :g v :D além

das tensões <; , <g v <D . Primeiramente, vamos denifir:

:; 6 :;

:D 6 :D

:g 6 :g :g

23

Refletindo a resistência WD pelo transístor equivalente do par darlington, e

equacionando o circuito para :; temos: lo 6

Ymm Yoq

xo 1 xq

6 \. `eX, então:

lq 6 1 Zlo ≈ 1 lo ≈ lm ≈ \n. ^_yX

Ym 6 Z_Y

Yq 6 xq lq 6 _Y

Yo 6 Yq Yoq 6 f. eY

Análise AC

Temos agora todos os valores provenientes da analise DC. Faremos agora a análise AC,

utilizando o modelo PI:

Modelo equivalente para AC

Podemos primeiro determinar a corrente N; 6

!# !R

' 6 N; A

1)WD ⇒ ' =

Tendo F =

2{

hp

P#

, mas sendo:

− (A

+ 1)WD

F

= 1,22J, já podemos tirar o ganho:

(A

+ 1)WD

'

=

≈ 1 <<

(F + (A

+ 1)WD )

!

Fazendo equivalente de thevenin, podemos determinar W) = # = F + A

WD , agora

3

basta um paralelo e temos W = W) //W; = 1,6J.

24

Fazendo equivalente de thevenin para saída agora W') 6 !*

z

!

mas

!*

!#

6 1, então

#

W') = ()z

Como

!#

3

= F + A

WD , temos W') =

por fim W'() =

Up

P# Up

( )

≈ WD . Desta forma W'() = W') //WD e

= 195J.

Xd = Z YY

x 6 Z, e

x~ = Zf`

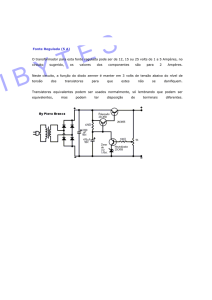

5. Inversor CMOS

Conceito

São amplamente aplicados em circuitos digitais. Possui inúmeras vantagens como alta

excursão de sinal, alta capacidade de corrente e a principal que é a resposta rápida. Em sua

configuração utilizam-se dois transistores, um NMOS e outro PMOS. Ambas as portas são

ligadas a uma tensão de entrada. A fonte do NMOS é conectada ao terra e o dreno ligado a

saída do outro transistor. É no dreno que obtemos a tensão de saída. Sobrando assim a fonte

do PMOS que é ligada a uma tensão Vdd, a qual a saída do transistor assumirá quando a

entrada for nula.

Operação

Nas figuras abaixo atribuímos valores para entrada do inversor para observarmos o seu

comportamento:

25

Caso 1- Entrada 0 V

Nesse caso observamos que Vgs=0, se isso acontece o transistor NMOS está em corte devido

ao fato de Vgs<Vt porque Vt≈0,7V. Logo a corrente no dreno será zero (id=0). Para

satisfazermos a equação do transistor PMOS que está em operação de tríodo:

N 6

<%

|<| ²

a tensão Vsd precisa ser nula. Com isso a saída

assumirá o valor de Vdd que no caso é de 5V.

Caso 2- Entrada 5V

Agora observamos uma situação contrária do caso 1. O transistor PMOS é quem está em corte

pois Vsg=0V (Vg=5V), também Vsg<Vt. Sabendo isso a corrente no dreno será zero. Agora

devemos

satisfazer

a

equação

do

NMOS

que

está

em

tríodo:

N 6

<%

|<| ². Concluímos que para id ser nula vds também precisa,

logo a saída assumira o valor da fonte do transistor NMOS que no caso é de 0 V.

26

Característica Transferência de Tensão

Agora vamos analisar o circuito provocando um aumento na tensão de entrada, obtemos o

gráfico que segue:

Observa-se 5 regiões de operação. A primeira e a última foram citadas nos casos anteriores em

que um dos transistores está em corte. Existem mais três regiões ilustradas no gráfico.

Também nota-se que Voh e Vol são independentes das dimensões dos transistores, o que

torna a tecnologia CMOS bem diferente de outras tecnologias.

Analisando a corrente na saída obtemos o gráfico:

Pode-se observar que a corrente máxima será em Vdd/2, pois os dois transistores estão em

saturação e a corrente será nula para os casos em que os transistores estão em corte.