Universidade Federal de Campina Grande

Unidade Acadêmica de Sistemas e Computação

Curso de Bacharelado em Ciência da Computação

Organização e Arquitetura

de Computadores I

Nível da Microarquitetura

(Parte Complementar)

Profa Joseana Macêdo Fechine Régis de Araújo

[email protected]

Carga Horária: 60 horas

DSC/CEEI/UFCG

Tópicos

Nível ISA

Nível da Microarquitetura

−

−

DSC/CEEI/UFCG

Datapath

Unidade de Controle

2

Microarquitetura

Microarquitetura: forma

como está implementada a

arquitetura em hardware

Processador:

DSC/CEEI/UFCG

Datapath: blocos funcionais

Controle: sinais de controle

Application

Software

programs

Operating

Systems

device drivers

Architecture

instructions

registers

Microarchitecture

datapaths

controllers

Logic

adders

memories

Digital

Circuits

AND gates

NOT gates

Analog

Circuits

amplifiers

filters

Devices

transistors

diodes

Physics

electrons

3

Microarquitetura

Múltiplas implementações para uma mesma

arquitetura:

Single-cycle

−

Multicycle

−

A execução de cada instrução é dividida em uma série

de passos menores

Pipelined

−

−

DSC/CEEI/UFCG

Cada instrução é executada em um único ciclo

A execução de cada instrução é dividida em uma série

de passos menores

Múltiplas instruções (parte de) executando ao mesmo

tempo.

4

Microarquitetura

Conceitos importantes:

Program execution time

Execution Time = (# instructions)(cycles/instruction)(seconds/cycle)

− Cycles/instruction = CPI

− Seconds/cycle = clock period

− 1/CPI = Instructions/cycle = IPC

DSC/CEEI/UFCG

Desafios na implementação de uma microarquitetura

Custo

Power

Desempenho

5

Microarquitetura

Processador MIPS

Subconjunto das instruções MIPS:

−

−

−

DSC/CEEI/UFCG

R-type instructions: and, or, add, sub, slt

Memory instructions: lw, sw

Branch instructions: beq

6

Micro-Arquitetura

Estado da Arquitetura

Determina o estado do Processador em um dado

instante de tempo

− PC

−

−

DSC/CEEI/UFCG

32 registradores

Memória

7

Microarquitetura

Elementos de estados do MIPS:

CLK

CLK

5

PC'

PC

32

32

5

5

32

32

A

RD

Instruction

Memory

A1

A2

WE3

RD1

RD2

A3

Register

WD3

File

32

32

CLK

WE

32

32

RD

32

Data

Memory

32

DSC/CEEI/UFCG

A

WD

8

Microarquitetura Processador MIPS

DSC/CEEI/UFCG

Datapath

Unidade de Controle

9

Processador

MIPS Single-Cycle

Execução de lw

1: Fetch da Instrução

CLK

CLK

PC'

PC

Instr

A

RD

Instruction

Memory

DSC/CEEI/UFCG

A1

CLK

WE3

WE

RD1

A

A2

RD2

A3

Register

WD3

File

RD

Data

Memory

WD

10

Processador

MIPS Single-Cycle

Execução de lw

2: Lê o operando fonte do RF

CLK

CLK

25:21

PC'

PC

A

RD

Instruction

Memory

DSC/CEEI/UFCG

Instr

A1

CLK

WE3

WE

RD1

A

A2

RD2

A3

Register

WD3

File

RD

Data

Memory

WD

11

Processador

MIPS Single-Cycle

Execução de lw

3: Sign-extend o imediato

CLK

CLK

PC'

PC

A

RD

Instr

25:21

A1

CLK

WE3

WE

RD1

A

Instruction

Memory

RD

Data

Memory

WD

A2

RD2

A3

Register

WD3

File

SignImm

15:0

Sign Extend

DSC/CEEI/UFCG

12

Processador

MIPS Single-Cycle

Execução de lw

4: Calcula o endereço efetivo de memória

ALUControl2:0

PC

A

RD

Instr

25:21

Instruction

Memory

A1

A2

A3

WD3

WE3

RD2

SrcB

Register

File

CLK

Zero

SrcA

RD1

ALU

PC'

010

CLK

CLK

ALUResult

WE

A

RD

Data

Memory

WD

SignImm

15:0

DSC/CEEI/UFCG

Sign Extend

13

Processador

MIPS Single-Cycle

Execução de lw

5: Lê o dado da memória e o escreva no RF

RegWrite

1

CLK

PC'

PC

A

RD

Instruction

Memory

Instr

25:21

20:16

A1

WE3

A2

RD2

A3

Register

WD3

File

SrcB

CLK

Zero

SrcA

RD1

ALU

CLK

ALUControl2:0

010

ALUResult

WE

A

RD

Data

Memory

WD

ReadData

SignImm

15:0

DSC/CEEI/UFCG

Sign Extend

14

Processador

MIPS Single-Cycle

Execução de lw

6: Determina o endereço da próxima instrução

RegWrite

1

CLK

PC'

PC

A

RD

Instr

Instruction

Memory

25:21

A1

A2

20:16

A3

+

WD3

WE3

RD2

SrcB

Register

File

CLK

Zero

SrcA

RD1

ALU

CLK

ALUControl2:0

010

ALUResult

WE

A

RD

Data

Memory

WD

ReadData

PCPlus4

SignImm

4

15:0

Sign Extend

Result

DSC/CEEI/UFCG

15

Processador

MIPS Single-Cycle

Execução de sw

Precisa escrever o valor do registrador na memória

RegWrite

0

CLK

CLK

PC'

PC

A

RD

Instr

+

Instruction

Memory

4

25:21

A1

WE3

ALUControl2:0

010

20:16

A2

20:16

RD2

SrcB

A3

Register

WD3

File

MemWrite

1

CLK

Zero

SrcA

RD1

ALU

ALUResult

WriteData

WE

A

RD

Data

Memory

WD

ReadData

PCPlus4

SignImm

15:0

Sign Extend

Result

DSC/CEEI/UFCG

16

Processador

MIPS Single-Cycle

Instruções R-Type: add, sub, and, or, ….

Escrever ALUResult no RF

−

Escreve em rd e não em rt

RegWrite

CLK

CLK

PC'

PC

A

RD

Instr

Instruction

Memory

25:21

20:16

A1

RegDst

1

WE3

1

0 SrcB

1

A2

RD2

A3

Register

WD3

File

15:11

+

varies

0

WriteReg4:0

MemWrite

CLK

Zero

SrcA

RD1

20:16

PCPlus4

ALUSrc ALUControl2:0

ALU

ALUResult

WriteData

MemtoReg

0

0

WE

A

RD

Data

Memory

WD

ReadData

0

1

0

1

SignImm

4

15:0

Sign Extend

Result

DSC/CEEI/UFCG

17

Processador

MIPS Single-Cycle

Instrução beq

Determina se os conteúdos dos registradores são iguais

Calcula o endereço alvo do desvio

−

(sign-extended immediate + PC+4)

PCSrc

CLK

0

PC'

PC

1

A

RD

Instr

Instruction

Memory

25:21

20:16

A1

A2

WE3

RegDst

x

RD2

0 SrcB

1

20:16

+

WriteReg4:0

ALUResult

WriteData

0

WE

A

RD

Data

Memory

WD

ReadData

0

1

1

SignImm

Sign Extend

<<2

+

15:0

CLK

MemtoReg

x

0

15:11

4

MemWrite

Zero

SrcA

RD1

A3

Register

WD3

File

PCPlus4

ALUSrc ALUControl2:0 Branch

0

110

1

ALU

RegWrite

0

CLK

PCBranch

Result

DSC/CEEI/UFCG

18

Processador

MIPS Single-Cycle

Unidade de Controle

31:26

5:0

MemtoReg

Control

MemWrite

Unit

Branch

ALUControl2:0

Op

ALUSrc

Funct RegDst

PCSrc

RegWrite

CLK

0

PC'

PC

1

A

RD

Instr

Instruction

Memory

25:21

20:16

A1

A2

A3

WD3

CLK

WE3

0 SrcB

1

RD2

Register

File

20:16

+

15:11

Sign Extend

WriteData

WE

A

RD

Data

Memory

WD

ReadData

0

1

0

1

SignImm

15:0

ALUResult

<<2

+

4

WriteReg4:0

PCPlus4

Zero

SrcA

RD1

ALU

CLK

PCBranch

Result

DSC/CEEI/UFCG

19

Processador

MIPS Single-Cycle

Control Unit

Control

Unit

Opcode 5:0

MemtoReg

MemWrite

Main

Decoder

Branch

ALUSrc

RegDst

RegWrite

ALUOp 1:0

Funct 5:0

DSC/CEEI/UFCG

ALU

Decoder

ALUControl 2:0

20

Processador MIPS

Single-Cycle

ALU

A

B

N

N

ALU

N

Y

DSC/CEEI/UFCG

3F

F2:0

Function

000

A&B

001

A|B

010

A+B

011

not used

100

A & ~B

101

A | ~B

110

A-B

111

SLT

21

Processador

MIPS Single-Cycle

ALU

A

B

N

N

N

0

1

F2

N

Cout

+

[N-1] S

Zero

Extend

N

N

N

N

0

1

2

3

2

F1:0

N

Y

DSC/CEEI/UFCG

22

Processador

MIPS Single-Cycle

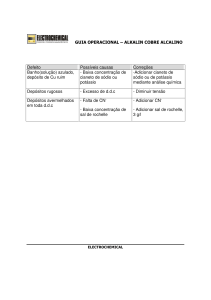

ALU Decoder

DSC/CEEI/UFCG

ALUOp1:0

Meaning

00

Add

01

Subtract

10

Look at Funct

11

Not Used

ALUOp1:0

Funct

ALUControl2:0

00

X

010 (Add)

X1

X

110 (Subtract)

1X

100000 (add)

010 (Add)

1X

100010 (sub)

110 (Subtract)

1X

100100 (and)

000 (And)

1X

100101 (or)

001 (Or)

1X

101010 (slt)

111 (SLT)

23

Processador

MIPS Single-Cycle

Funcionalidades

Jump

31:26

5:0

MemtoReg

Control

MemWrite

Unit

Branch

ALUControl2:0

Op

ALUSrc

Funct RegDst

PCSrc

RegWrite

CLK

0

1

0

1

PC'

PC

A

RD

Instr

Instruction

Memory

25:21

20:16

A1

CLK

WE3

RD2

A2

A3

Register

WD3

File

0 SrcB

1

20:16

PCJump

+

15:11

WriteReg4:0

PCPlus4

Sign Extend

WriteData

27:0

RD

Data

Memory

WD

ReadData

0 Result

1

PCBranch

31:28

25:0

DSC/CEEI/UFCG

A

<<2

+

15:0

ALUResult

WE

0

1

SignImm

4

Zero

SrcA

RD1

ALU

CLK

<<2

24

Processador

MIPS Single-Cycle

Decodificador Principal

Instruction

Op5:0

RegWrite

RegDst

AluSrc

Branch

MemWrite

MemtoReg

ALUOp1:0

Jump

R-type

000000

1

1

0

0

0

0

10

0

lw

100011

1

0

1

0

0

1

00

0

sw

101011

0

X

1

0

1

X

00

0

beq

000100

0

X

0

1

0

X

01

0

addi

001000

1

0

1

0

0

0

00

0

j

000100

0

X

X

X

0

X

XX

1

DSC/CEEI/UFCG

25

Processador

MIPS Single-Cycle

Desempenho: Quão rápido é o processador?

Cycle time: limitado pelo caminho crítico - lw

31:26

5:0

MemtoReg

Control

MemWrite

Unit

Branch

ALUControl2:0

Op

ALUSrc

0

0

PCSrc

Funct RegDst

RegWrite

0

1

PC'

PC

A

RD

Instr

Instruction

Memory

25:21

A1

20:16

A2

1

WE3

CLK

SrcA

RD1

1

0 SrcB

1

RD2

A3

Register

WD3

File

+

15:11

WriteReg4:0

Sign Extend

WriteData

0

WE

1

0

ReadData

A

RD

1

Data

Memory

WD

0

1

SignImm

15:0

ALUResult

<<2

+

4

Zero

0

20:16

PCPlus4

010

ALU

CLK

CLK

PCBranch

Result

DSC/CEEI/UFCG

26

Processador MIPS SingleCycle

Caminho crítico

Tc = tpcq_PC + tmem + max(tRFread, tsext) + tmux + tALU + tmem + tmux + tRFsetup

Na maioria das implementações os caminhos

limitantes são: memória, ALU, register file. Assim,

Tc = tpcq_PC + 2tmem + tRFread + 2tmux + tALU + tRFsetup

DSC/CEEI/UFCG

27

Processador

MIPS Single-Cycle

Element

Parameter

Delay (ps)

Register clock-to-Q

tpcq_PC

30

Register setup

tsetup

20

Multiplexer

tmux

25

ALU

tALU

200

Memory read

tmem

250

Register file read

tRFread

150

Register file setup

tRFsetup

20

Tc = tpcq_PC + 2tmem + tRFread + 2tmux + tALU + tRFsetup

= [30 + 2(250) + 150 + 2(25) + 200 + 20] ps

= 950 ps

DSC/CEEI/UFCG

28

Processador

MIPS Single-Cycle

DSC/CEEI/UFCG

Para um programa com 100 bilhões de instruções executando

em um processador MIPS single-cycle,

Execution Time

= (# instructions)(cycles/instruction)(seconds/cycle)

= (100 × 109)(1)(950 × 10-12 s)

= 95 seconds

29

Processadores Intel

Evolução dos Microprocessadores Intel

DSC/CEEI/UFCG

30

Processadores Intel

DSC/CEEI/UFCG

31

Processadores Intel IA-32

Chip do Pentium 4

Chip do Core Duo

DSC/CEEI/UFCG

32

Processadores Intel IA-32

Chip do Core i3

Chip do Core i5

Chip do Core i7

DSC/CEEI/UFCG

33

Processadores Intel IA-32

Fonte: http://techreport.com/review/18216/intel-core-i3-and-i5-dual-core-processors

DSC/CEEI/UFCG

34